# Pico-grid: Multiple Multitype Energy Harvesting System

A thesis submitted for the degree of Doctor of Philosophy by

### **Mohamad Hazwan bin Mohd Daut**

Robinson College

Department of Engineering

Electrical Engineering (Div. B)

University of Cambridge

September 2018

### **Abstract**

# MOHAMAD HAZWAN BIN MOHD DAUT PICO-GRID: MULTIPLE MULTITYPE ENERGY HARVESTING SYSTEM

This thesis focuses on the development of a low power energy harvesting system specifically targeted for wireless sensor nodes (WSN) and wireless body area network (WBAN) applications. The idea for the system is derived from the operation of a micro-grid and therefore is termed as a pico-grid and it is capable of simultaneously delivering power from multiple and multitype energy harvesters to the load at the same time, through the proposed parallel load sharing mechanism achieved by a voltage droop control method. Solar panels and thermoelectric generator (TEG) are demonstrated as the main energy harvesters for the system.

Since the magnitude of the output power of the harvesters is time-varying, the droop gain in the droop feedback circuitry should be designed to be dynamic and self-adjusted according to this variation. This ensures that the maximum power is capable to be delivered to the load at all times. To achieve this, the droop gain is integrated with a light dependent resistor (LDR) and thermistor whose resistance varies with the magnitude of the source of energy for the solar panel and TEG, respectively. The experimental results demonstrate a successful variation droop mechanism and all connected sources are able to share equal load demands between them, with a maximum load sharing error of 5 %. The same mechanism is also demonstrated to work for maximum power point tracking (MPPT) functionality. This concept can potentially be extended to any other types of energy harvester.

The integration of energy storage elements becomes a necessity in the pico-grid, in order to support the intermittent and sporadic nature of the output power for the harvesters. A rechargeable battery and supercapacitor are integrated in the system, and each is accurately designed to be charged when the loading in the system is low and discharged when the loading in the system is high. The dc bus voltage which indicates the magnitude of the loading in the system is utilised as the signal for the desired mode of operation. The constructed system demonstrates a successful operation of charging and discharging at specific levels of loading in the system.

The system is then integrated and the first wearable prototype of the pico-grid is built and tested. A successful operation of the prototype is demonstrated and the load demand is shared equally between the source converters and energy storage. Furthermore, the pico-grid is shown

to possess an inherent plug-and-play capability for the source and load converters. Few recommendations are presented in order to further improve the feasibility and reliability of the prototype for real world applications.

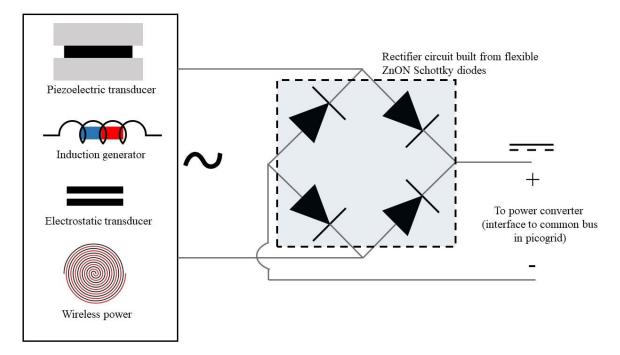

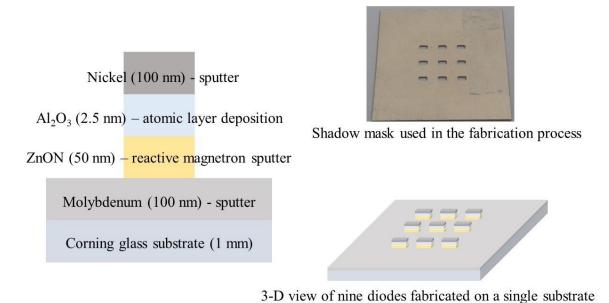

Next, due to the opportunity of working with a new semiconductor compound and accessibility to the fabrication facilities, a ZnON thin film diode is fabricated and intended to be implemented as a flexible rectifier circuit. The fabrication process can be done at low temperature, hence opening up the possibility of depositing the device on a flexible substrate. From the temperature dependent I-V measurements, a novel method of extracting important parameters such as ideality factor, barrier height, and series resistance of the diode based on a curve fitting method is proposed. It is determined that the ideality factor of the fabricated diode is high (> 2 at RT), due to the existence of other transport mechanism apart from thermionic emission that dominates the conduction process at lower temperature. It is concluded that the high series resistance of the fabricated diode (3.8 k $\Omega$  at RT) would mainly hinder the performance of the diode in a rectifier circuit.

### **Declaration**

This thesis is a collection of work completed by the author whilst pursuing his doctorate at the Department of Engineering, University of Cambridge. The work is entirely original except where due reference has been made. No contents from this thesis have been submitted at this institution or elsewhere for the application of another degree or qualification.

This thesis is comprised of 44672 words and 94 figures and tables. These do not exceed the limits set by the Department of Engineering.

Mohamad Hazwan bin Mohd Daut

September 2018

### Acknowledgements

I would like to express my highest gratitude to a few people who have made this PhD journey an enriching and rewarding experience.

First and foremost, I would like to express my highest appreciation to my main supervisor, Professor Arokia Nathan who has been extremely supportive throughout my entire time spent in Cambridge. He was there during the difficult times to advise me not only on professional matters, but also, on occasions, personal matters. I would also like to express my gratitude to my final year supervisor, Dr. Hasko who has been kind enough to provide the necessary support and guidance when my supervisor resigned from the university. Without either, my PhD would have been very difficult to accomplish.

I would also like to thank my fellow colleagues who have made my day-to-day work a very interesting and enjoyable experience, particularly to Dr. Hanbin Ma, Chen Jiang, Guangyu Yao, Philex, and the rest of the members of The Hetero-Genesys Laboratory. Hanbin was the first person to greet me when I arrived at Cambridge and has since provided me with insightful advices throughout my research. Chen Jiang was always there every morning asking me about my well-being and Guangyu has been supportive in cleanroom related matters. Without these people, my days in the lab would not have been such an enjoyable experience as it was.

Personally, I would like to thank Akmal, Zurina, Nik, Fendi, Fateen, Indra, and the whole Malaysian community in Cambridge in general for supporting me with good food, fun activities, and good companionship from the day I arrived to the day to the day I submitted this thesis.

For enabling me to come to Cambridge and start my PhD, I would like to thank my sponsors, Yayasan Khazanah and Cambridge & Commonwealth Trust. Also, I would like to thank and acknowledge CREST and Economic Planning Unit from the Malaysia government for providing me with research fund to support my research.

Finally and most importantly, I would like to thank my family; my father, mother, and three brothers who have given me the utmost support, love, and encouragement throughout my life. This acknowledgement would not be complete without me giving my highest gratitude to my fiancée, Amirah who has been very kind in dealing with my ups and downs throughout this journey.

## **Table of Contents**

| Abstract                                                     | i    |

|--------------------------------------------------------------|------|

| Declaration                                                  | iii  |

| Acknowledgements                                             | iv   |

| Table of Contents                                            | v    |

| List of Figures                                              | ix   |

| List of Tables                                               | xiii |

| List of Abbreviations                                        | xiv  |

| List of Publications                                         | xvi  |

| Chapter 1: Introduction                                      | 1    |

| 1.1 Background and Motivation                                | 1    |

| 1.2 Aim and Objectives                                       | 6    |

| 1.3 Pico-grid                                                | 7    |

| 1.4 Thesis Outline                                           | 9    |

| Chapter 2: Parallel Load Sharing – Theory and Demonstration  | 11   |

| 2.1 Foreword                                                 | 11   |

| 2.2 Background and Theory                                    | 11   |

| 2.2.1 The Need for Multiple Multitype Energy Harvesters      | 11   |

| 2.2.2 Voltage Droop Current Sharing Mechanism                | 19   |

| 2.2.3 P.U Equal Load Sharing and Simulation                  | 21   |

| 2.3 Droop Demonstration                                      | 26   |

| 2.3.1 I-V Characterisation for Harvesters                    | 26   |

| a. Solar Panel                                               | 26   |

| b. Thermoelectric Generator (TEG)                            | 28   |

| 2.3.2 Calculating Required Droop from Converter V-I Loadline | 30   |

| a. LTC-3129 for Solar Panel                                  | 31   |

| b. LTC-3105 for TEG                                                  | 35 |

|----------------------------------------------------------------------|----|

| 2.3.3 Variable Droop Demonstration                                   | 40 |

| a. Variable Droop for Solar Cell                                     |    |

| b. Variable Droop for TEGs                                           |    |

| 2.4 Load Sharing Demonstration                                       |    |

| 2.4.1 System Layout                                                  |    |

| 2.4.2 Case 1: Parallel Load Sharing Demonstration                    |    |

| 2.4.3 Case 2: Plug-and-play (PnP) Demonstration                      |    |

| 2.5 Summary                                                          |    |

| Chapter 3: Energy Storage and System Operation                       |    |

| 3.1 Foreword                                                         |    |

| 3.2 Energy Storage Integration                                       |    |

| 3.2.1 Rechargeable Battery and Supercapacitor                        |    |

| 3.2.2 Charging and Discharging Mechanism                             |    |

| a. BQ25504 for Battery Charging                                      |    |

| b. LTC3105 for Supercapacitor Charging                               |    |

| c. LTC3105 for Storage Discharging                                   |    |

| 3.2.3 Demonstration of Bus Voltage Dependent Mechanism (Mode Select) |    |

|                                                                      |    |

| 3.3 System Operation                                                 |    |

| 3.3.1 Start-Up                                                       |    |

| 3.3.2 No Source Condition                                            |    |

| 3.3.3 No Load Condition                                              | 79 |

| 3.3.4 Maximum Load Condition and Load Disconnect (Shedding)          | 81 |

| 3.4 Summary                                                          | 82 |

| Chapter 4: System Integration                                        | 83 |

| 4.1 Foreword                                                         | 83 |

| 4.2 System Integration                                               | 83 |

| 4.2.1 Plug-and-play Demonstration                                  | 85  |

|--------------------------------------------------------------------|-----|

| 4.2.2 Full System Evaluation                                       | 88  |

| 4.3 Wearable Prototype                                             | 92  |

| 4.3.1 Prototype Construction                                       | 92  |

| 4.3.2 Prototype Performance                                        | 95  |

| 4.3.3 Recommendations for Improvement                              | 96  |

| 4.4 Summary                                                        | 98  |

| Chapter 5: ZnON Thin Film Diode – Fabrication and Characterisation | 99  |

| 5.1 Foreword                                                       | 99  |

| 5.2 Background                                                     | 100 |

| 5.2.1 ZnON Semiconductor                                           | 100 |

| 5.2.2 Schottky MIS Diode                                           | 102 |

| 5.3 Fabrication and Characterisation Results                       | 105 |

| 5.3.1 Fabrication and Characterisation Method                      | 105 |

| a. Fabrication Method                                              | 105 |

| b. Characterisation Method                                         | 109 |

| c. Reproducibility                                                 | 110 |

| d. Evidence of Schottky Contact Behaviour                          | 112 |

| e. Effects of Post Deposition Annealing                            | 113 |

| 5.3.2 Temperature Dependent I-V Measurements                       | 116 |

| 5.3.3 Room Temperature I-V and C-V Measurements                    | 123 |

| a. I-V Measurements                                                | 123 |

| b. C-V Measurements and Carrier Concentration                      | 125 |

| 5.3.4 Comments on the Overall Performance of the Diode             | 125 |

| 5.4 Summary                                                        | 128 |

| Chapter 6: Conclusion and Future Work                              | 129 |

| 6.1 Conclusion                                                     | 120 |

| 6.1.1 Key Findings, Contributions, and Conclusion for Part 1                  | 130 |

|-------------------------------------------------------------------------------|-----|

| 6.1.2 Key Findings, Contributions, and Conclusion for Part 2                  | 131 |

| 6.2 Future Work                                                               | 133 |

| 6.2.1 Future Work for Work Package Part 1                                     | 133 |

| 6.2.2 Future Work for Work Package Part 2                                     | 133 |

| References                                                                    | 136 |

| Appendix                                                                      | 147 |

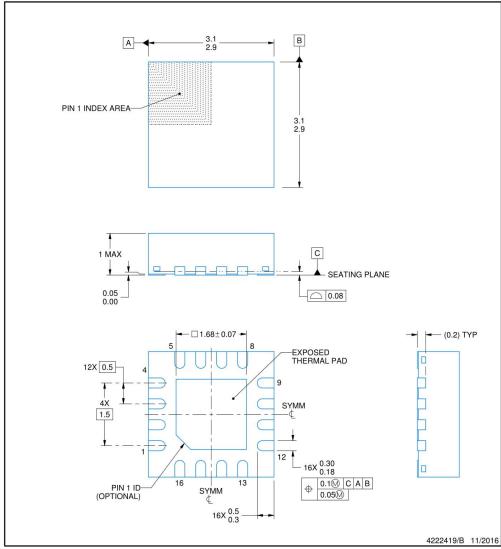

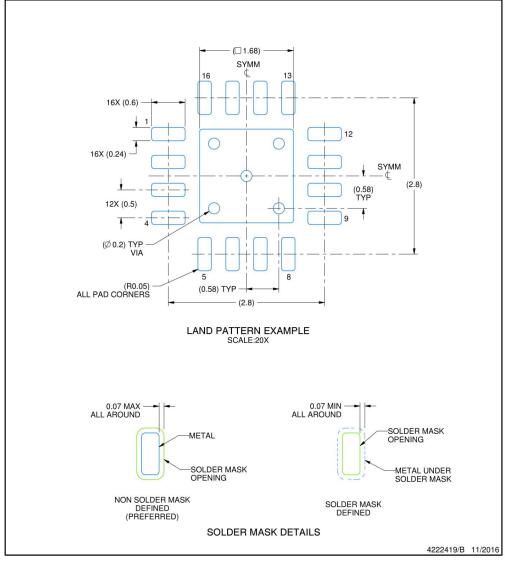

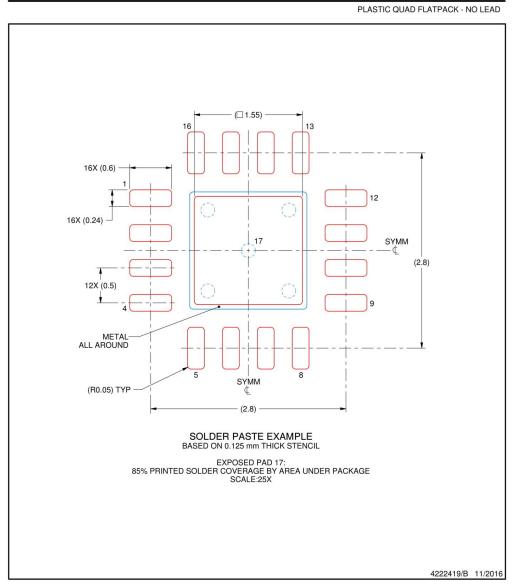

| Appendix 1 – Datasheets for DC-DC converter ICs                               | 147 |

| Appendix 2 – Comparison between rechargeable batteries and supercapacitor     | 230 |

| Appendix 3 – Bill of materials (BOM) for the pico-grid first prototype        | 232 |

| Appendix 4 – Wolfram Mathematica programme to plot the I-V curve of the diode | 237 |

### **List of Figures**

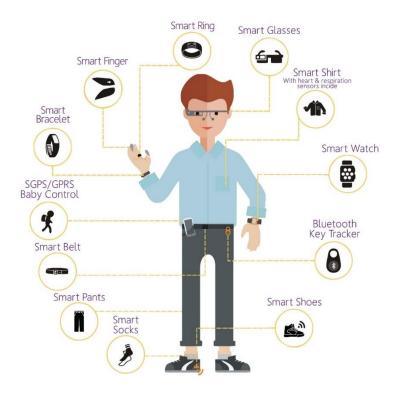

- Figure 1.1: Wearables on a person in the future. Image taken from RoweBots [3].

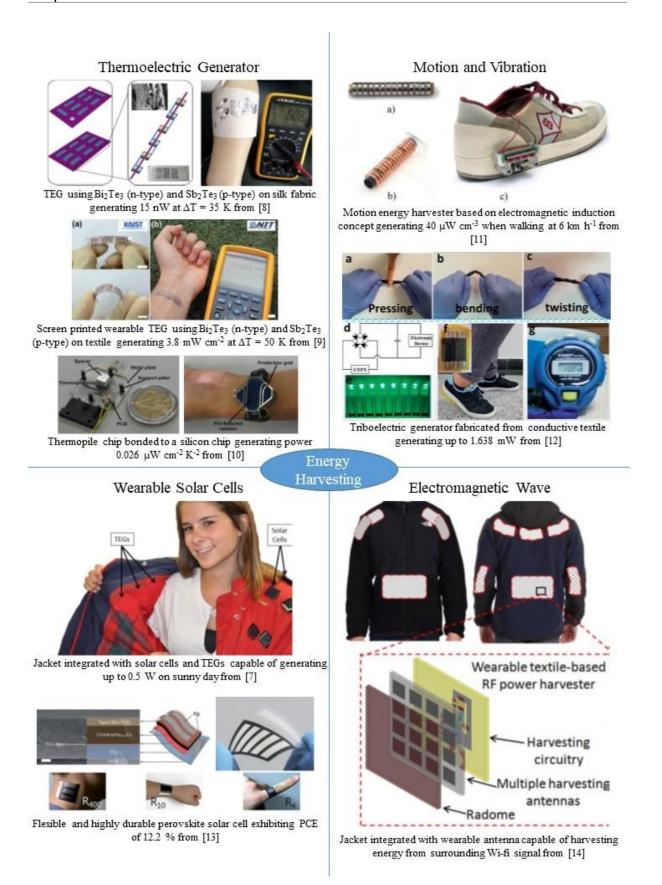

- Figure 1.2: Mechanism to harvest energy from the human body and surroundings to generate power for wearable devices. Images taken from their respective publications in [7]–[14].

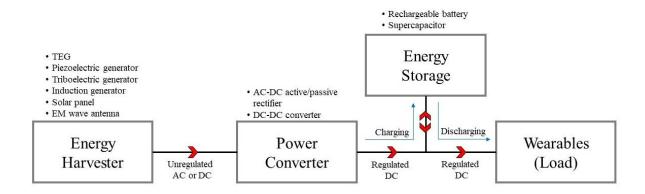

- Figure 1.3: System architecture of a wearables with its own energy harvester and energy storage.

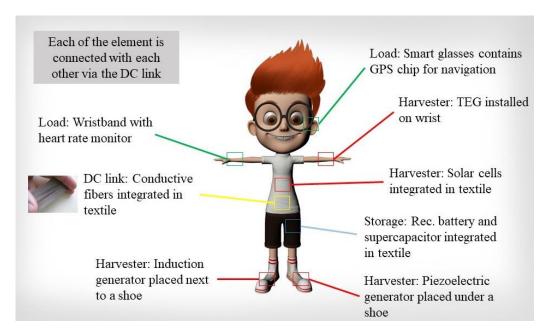

- Figure 1.4: The final prototype proposed for the pico-grid system on human body.

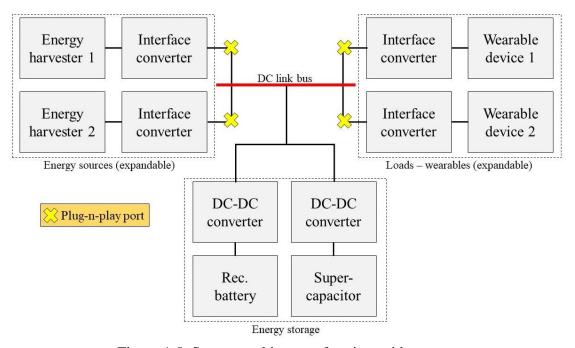

- Figure 1.5: System architecture for pico-grid system.

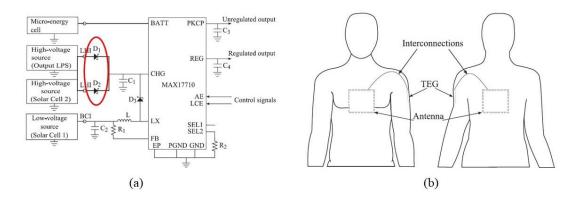

- Figure 2.1: (a) shows a multiple multitype energy harvesting system proposed by Lemey et al.

- [24]. The red oval shows the OR-ing diode configuration. (b) shows the actual depictions of the system on the human body. Images taken from [24].

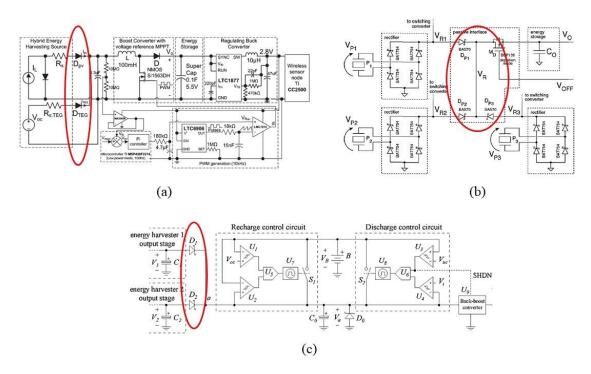

- Figure 2.2: Multiple multitype energy harvesting systems using OR-ing method reported in publications; (a) from [25], (b) from [26], (c) from [27]. Red ovals show the OR-ing configuration.

- Figure 2.3: Difficulty in OR-ing configuration due to the output voltage mismatch.

- Figure 2.4: Difficulty in OR-ing configuration due to the different power ratings.

- Figure 2.5: Proposed system by Kang et al. [31]. Left shows the circuitry architecture of the energy combiner system and the flowchart of the combiner operation is shown on the right.

- Figure 2.6: Multiple energy harvesting system utilising priority based queueing method proposed by Dini et al. [34] The system architecture is shown on the left and the operation flowchart is shown on the right.

- Figure 2.7: (a) shows the typical loadline of DC-DC converter (in blue) and the modified loadline with droop (in green). (b) shows the connection of three power converters with different rated power connected in parallel.

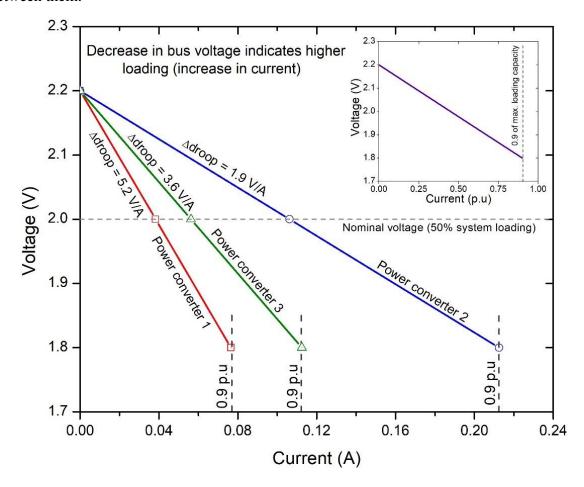

- Figure 2.8: V-I loadlines of all power converters and their respective voltage droop. The inset figure shows the loadlines of all power converters in P.U. The loadlines shown here represent the steady state value of the power converter.

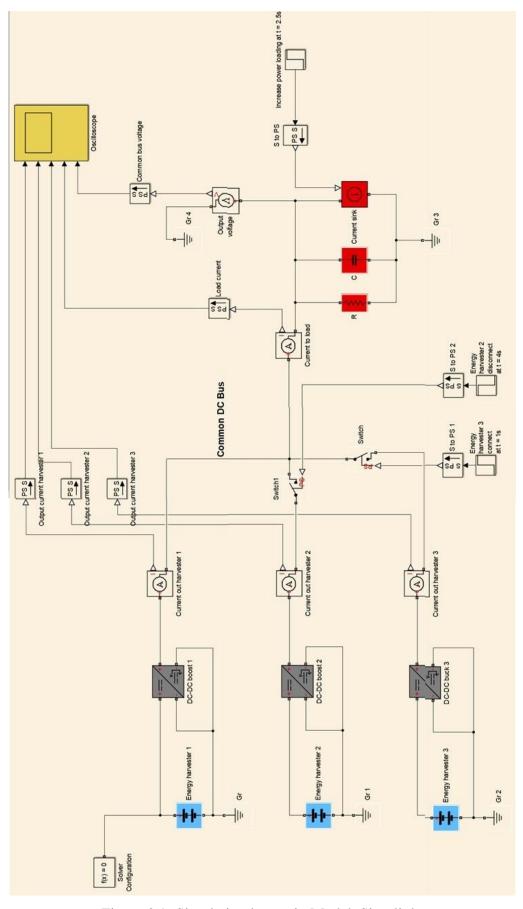

- Figure 2.9: Simulation layout in Matlab Simulink.

- Figure 2.10: Results from the simulation.

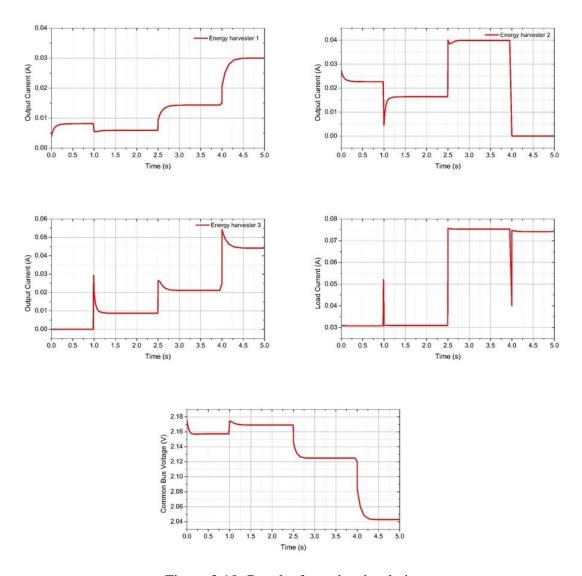

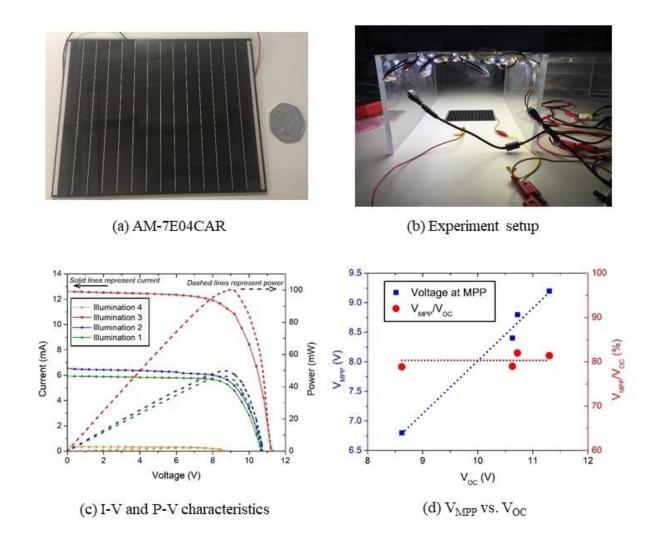

- Figure 2.11: Experimental setup and characterisation results from the solar panel.

- Figure 2.12: Pictures showing the TEG harvester and experiment setup together with the characterisation results.

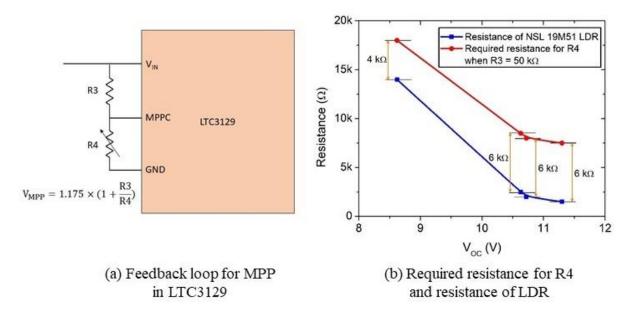

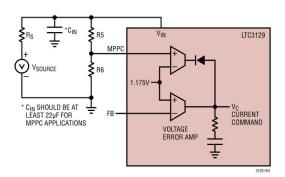

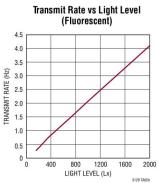

- Figure 2.13: The programmed MPP function and the resistance of the LDR compared with the required resistance to ensure a reliable MPP functionality.

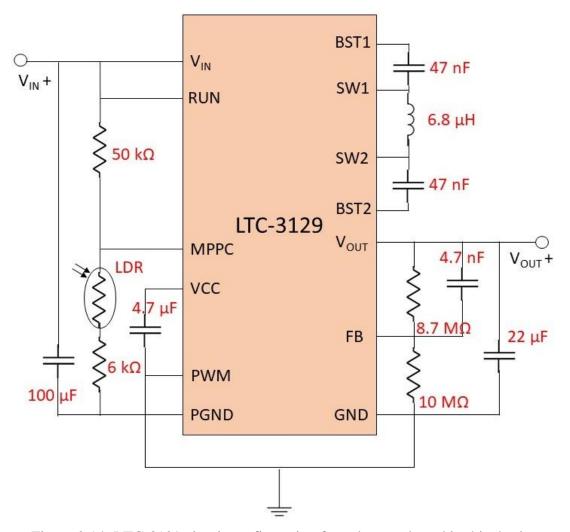

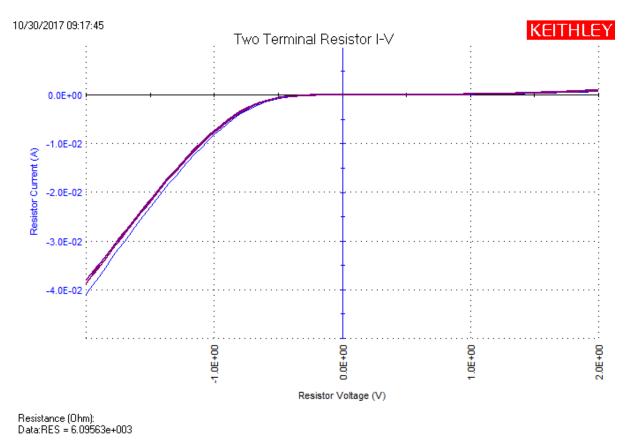

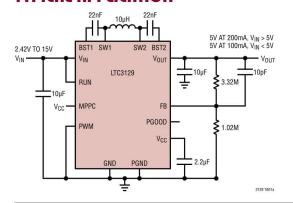

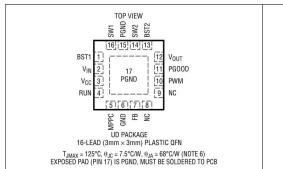

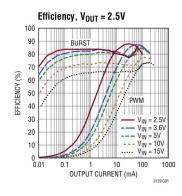

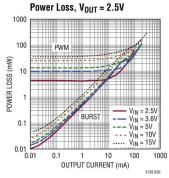

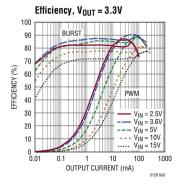

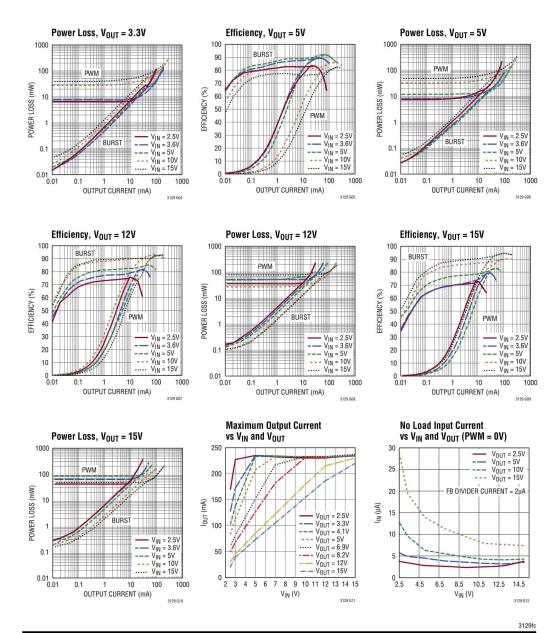

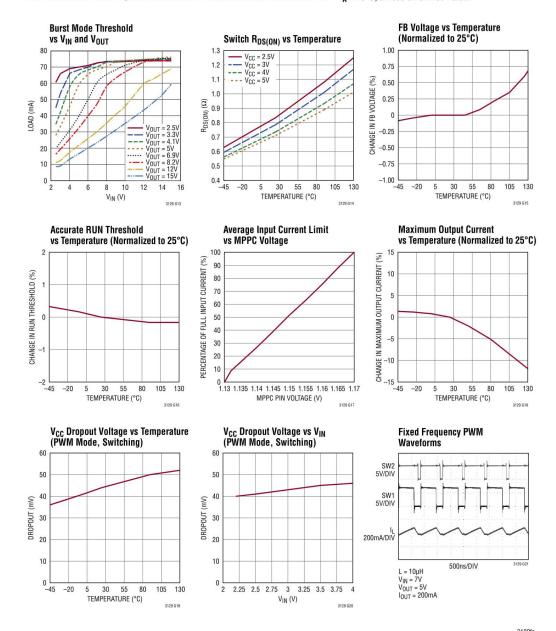

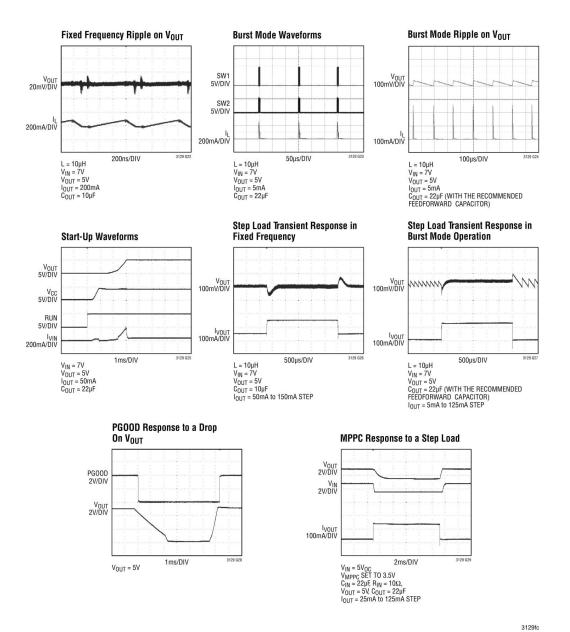

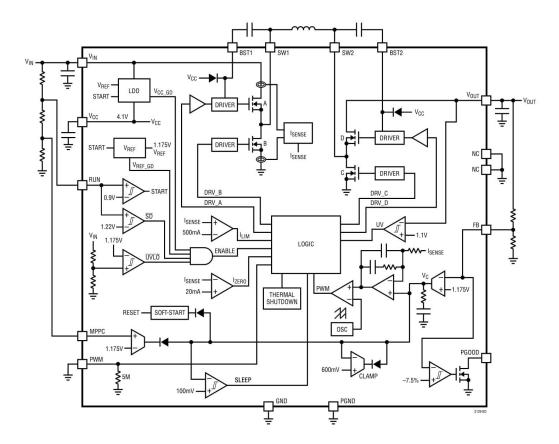

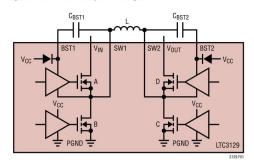

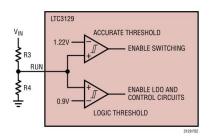

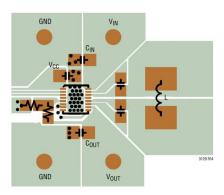

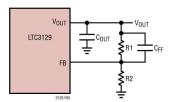

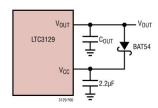

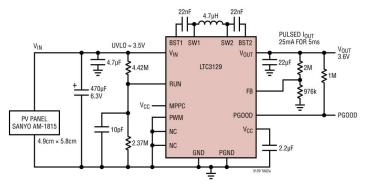

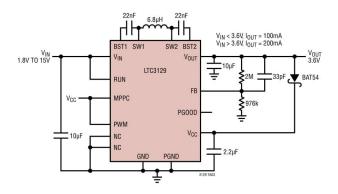

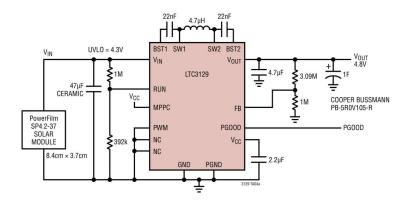

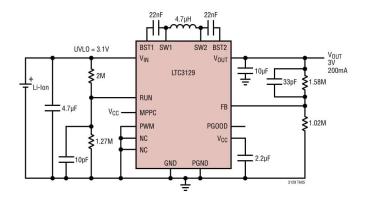

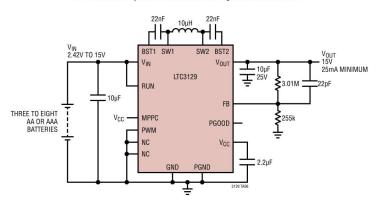

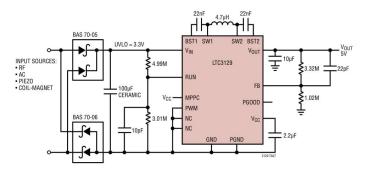

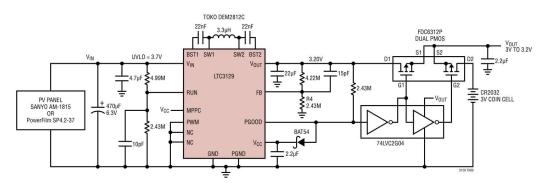

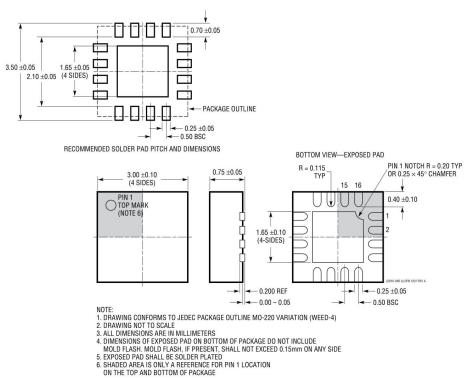

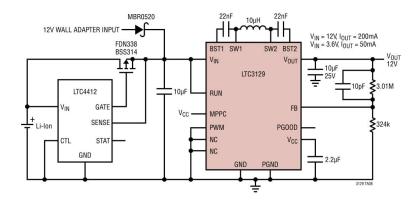

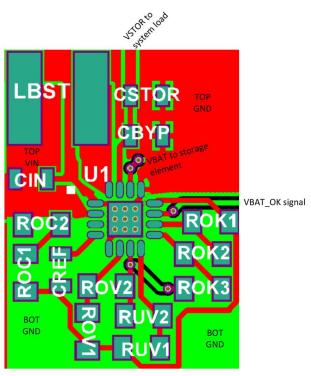

- Figure 2.14: LTC-3129 circuit configuration for solar panel used in this thesis.

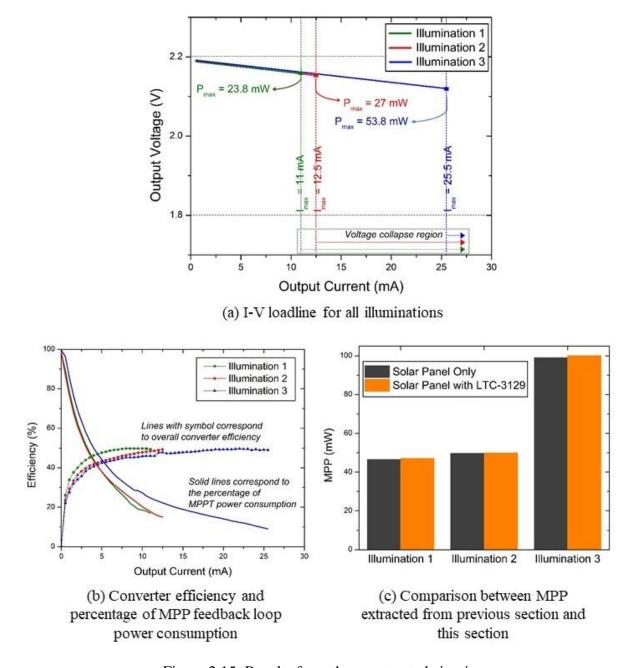

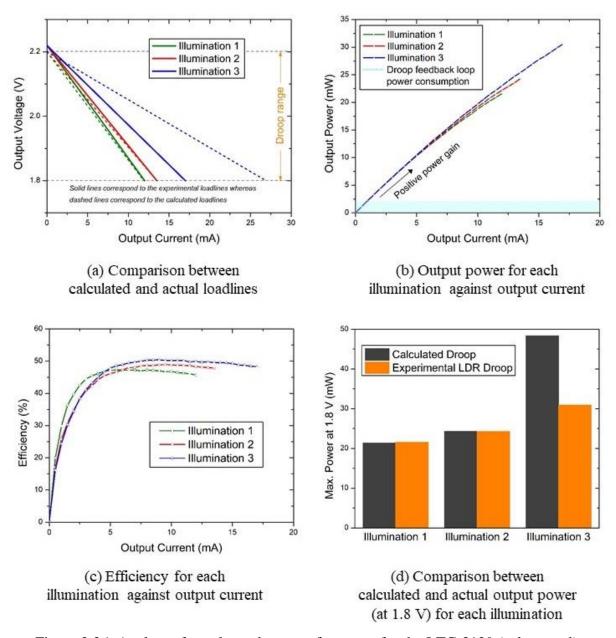

- Figure 2.15: Results from the constructed circuit.

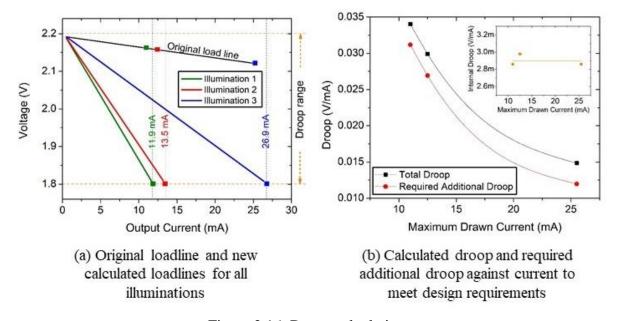

- Figure 2.16: Droop calculations.

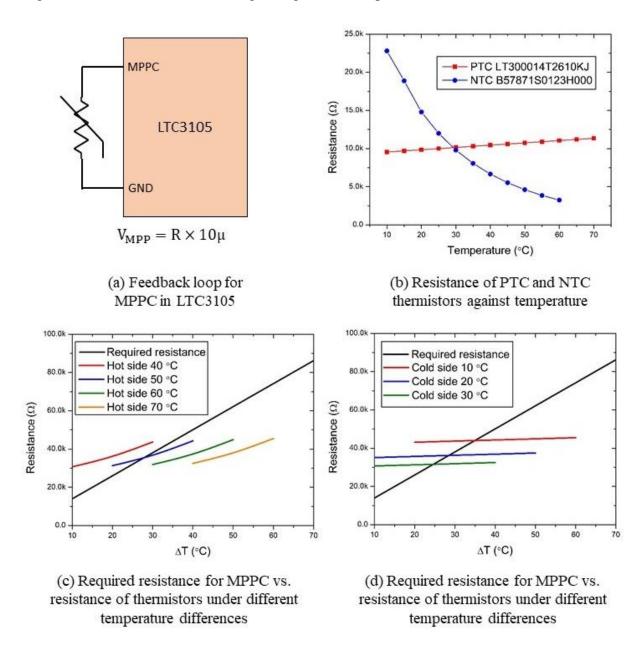

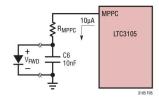

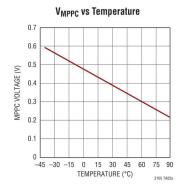

- Figure 2.17: The MPPC function, the resistance of the PTC and NTC thermistors, and the usage of these thermistors in simulated situations when compared to the required resistance to ensure a reliable MPPC functionality.

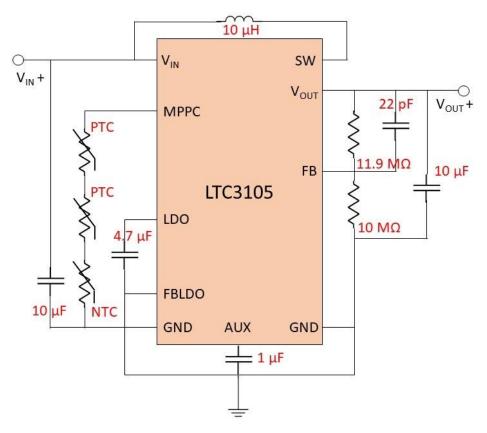

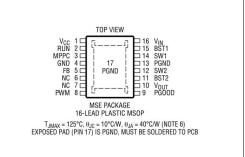

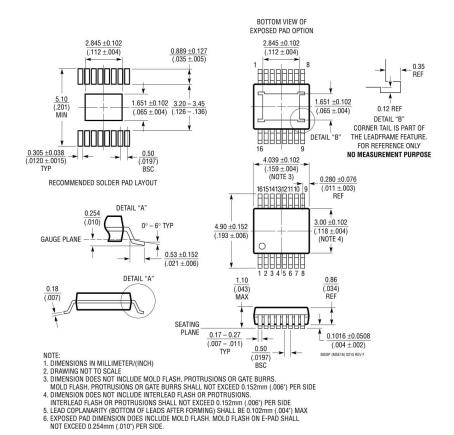

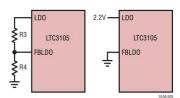

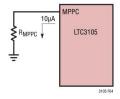

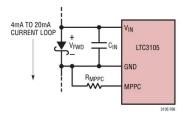

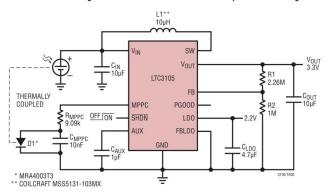

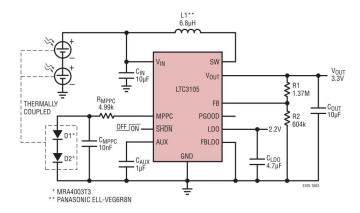

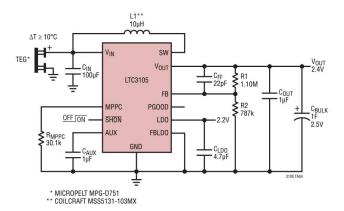

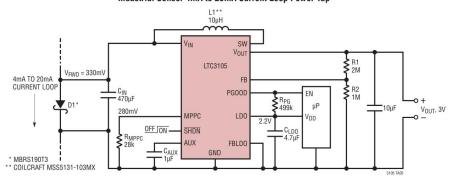

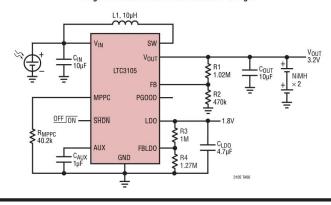

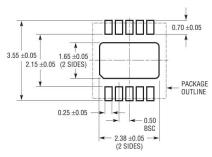

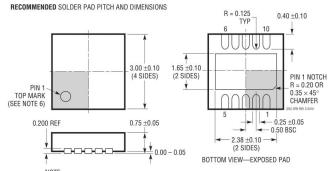

- Figure 2.18: LTC-3105 circuit configuration for TEGs used in this thesis.

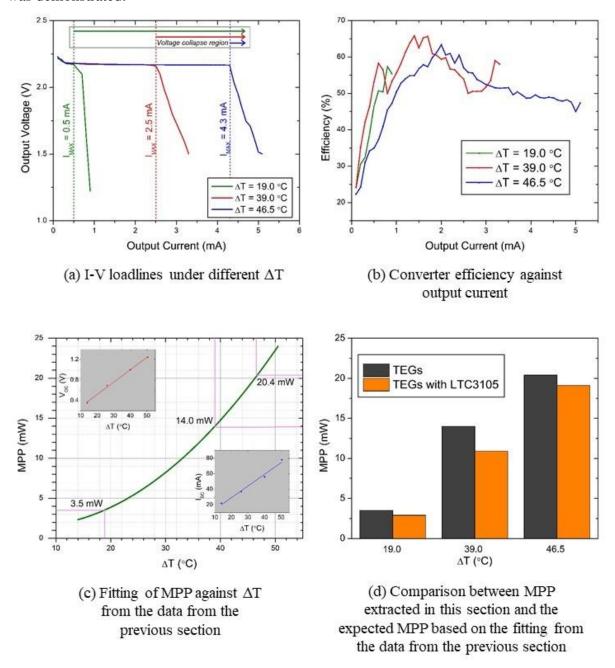

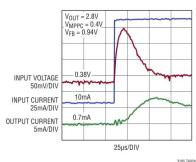

- Figure 2.19: Results from the constructed circuit.

- Figure 2.20: Droop calculations.

- Figure 2.21: The need for variable droop gain.

- Figure 2.22: Droop integrated in the voltage feedback loop of a DC-DC converter.

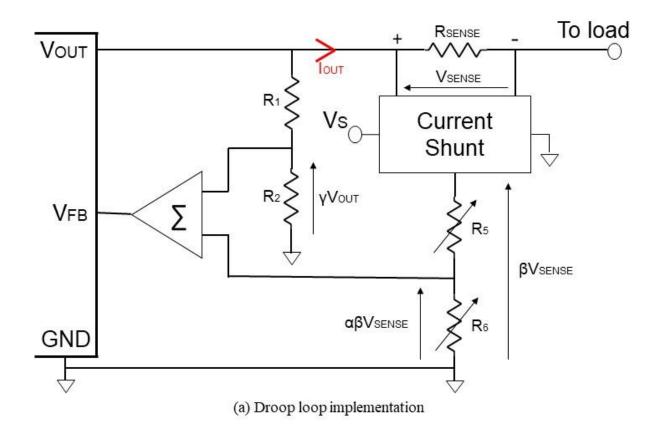

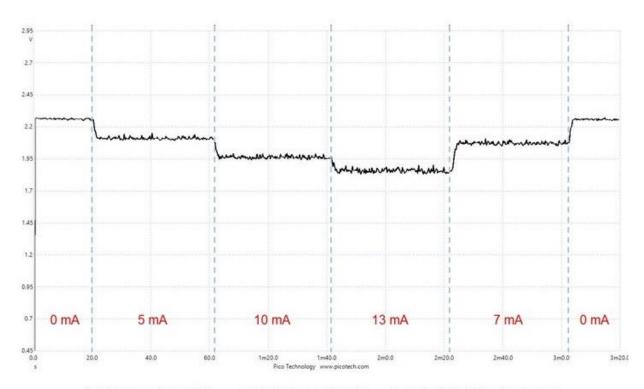

- Figure 2.23: Droop loop implementation and non-inverting summing amplifier configuration.

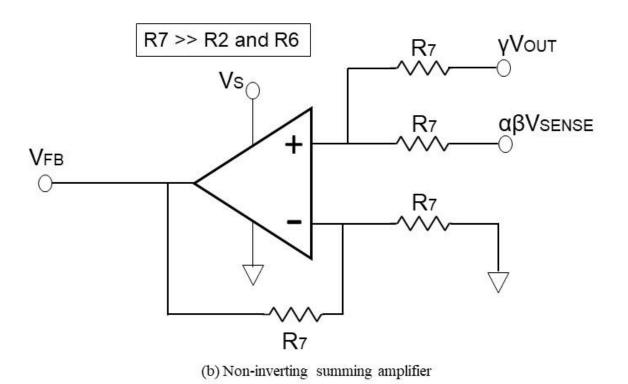

- Figure 2.24: Voltage droop feedback calculations for the LTC-3129 (solar panel).

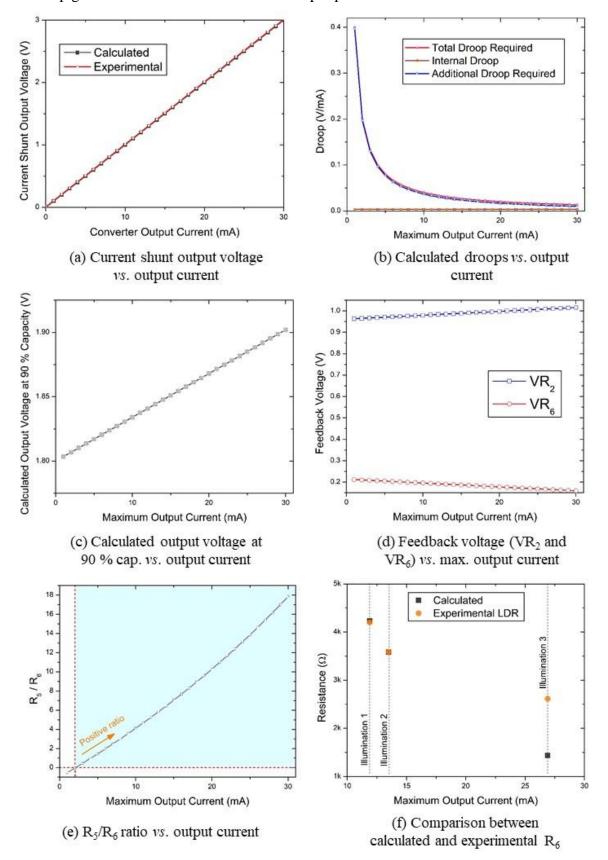

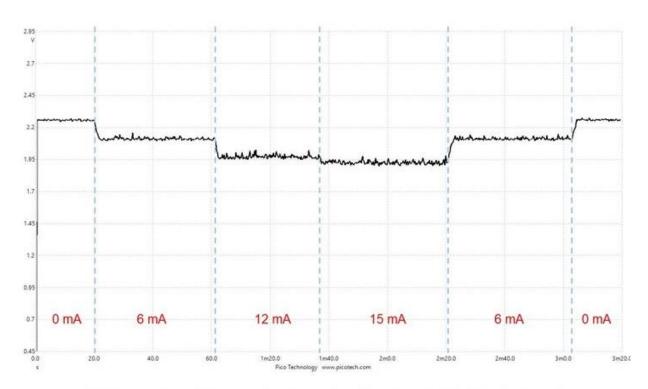

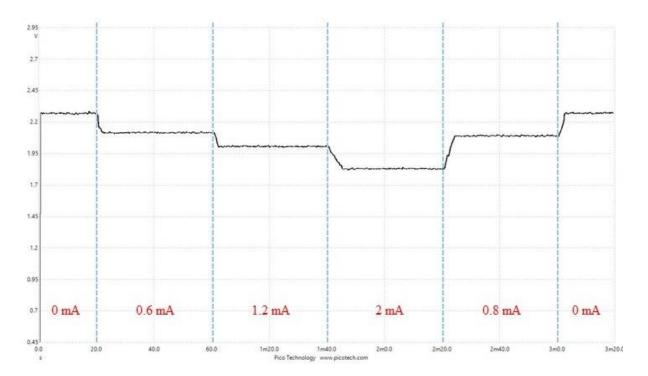

- Figure 2.25: Scope waveform results for the droop test for the LTC-3129 (solar panel).

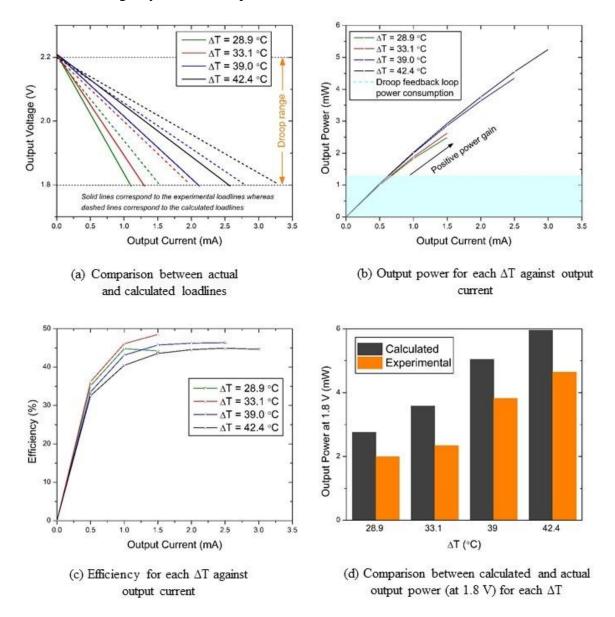

- Figure 2.26: Analyses for voltage droop performance for the LTC-3129 (solar panel).

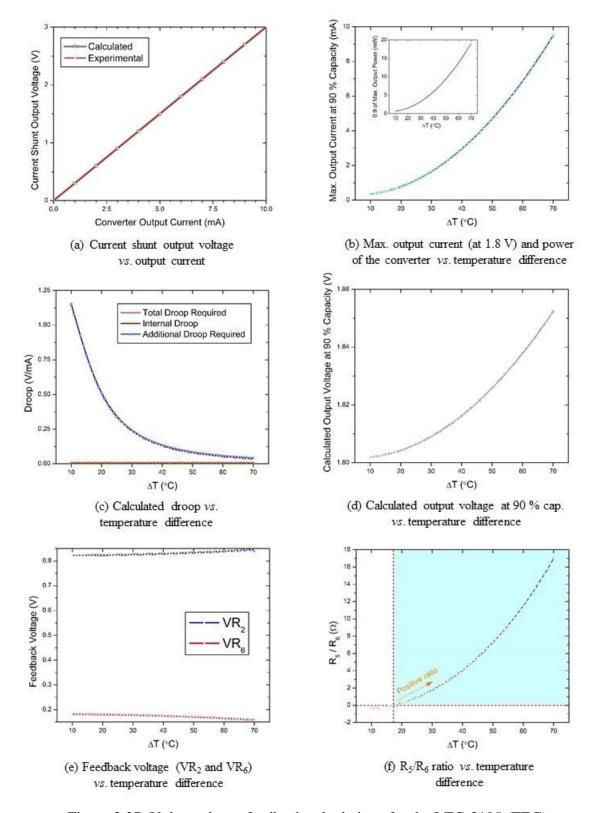

- Figure 2.27: Voltage droop feedback calculations for the LTC-3105 (TEG).

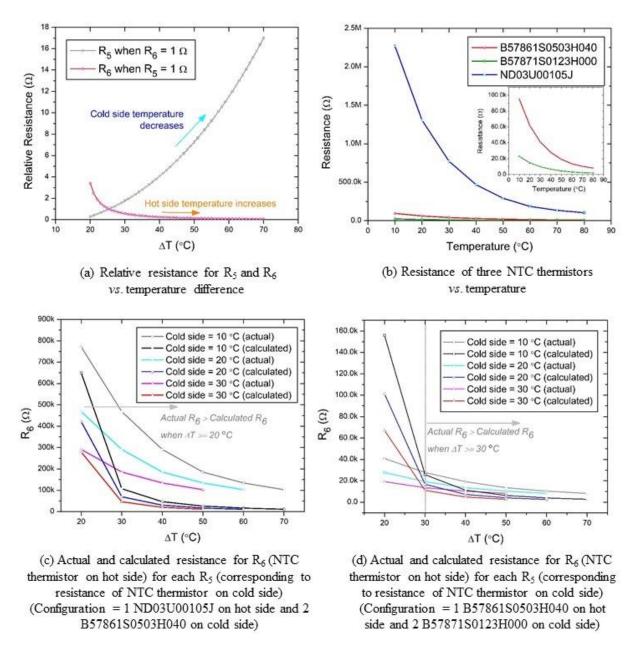

- Figure 2.28: Thermistors configurations for the LTC-3105 to self-track input power variation for TEG.

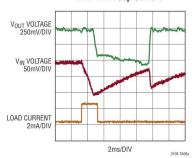

- Figure 2.29: Scope waveform results for the droop test for the LTC-3105 (TEG).

- Figure 2.30: Analyses for voltage droop performance for the LTC-3105 (TEG).

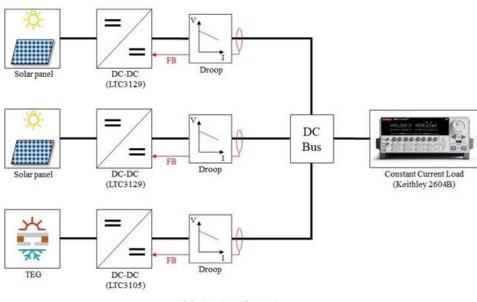

- Figure 2.31: System layout and test rig used to validate the load sharing experiments.

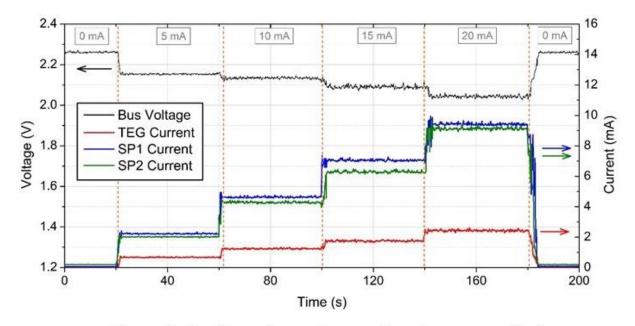

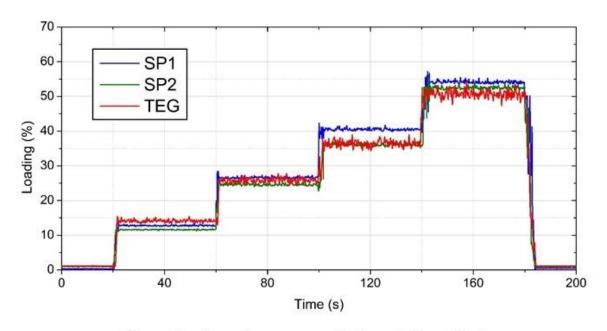

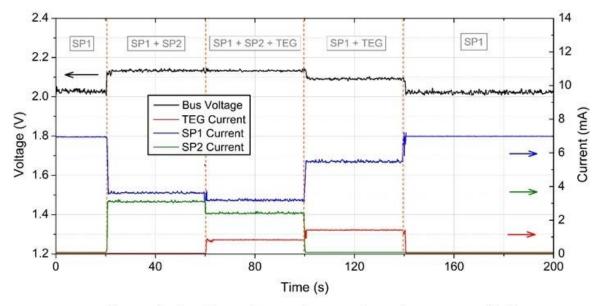

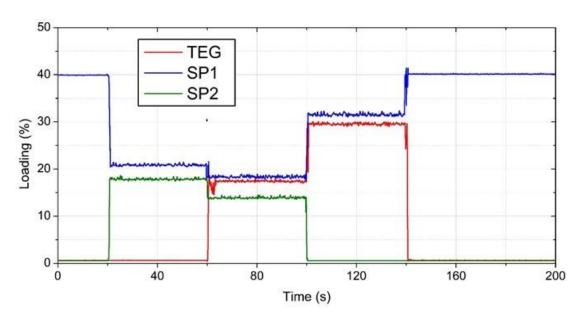

- Figure 2.32: Results from the test in case 1.

- Figure 2.33: Results from the test in case 2.

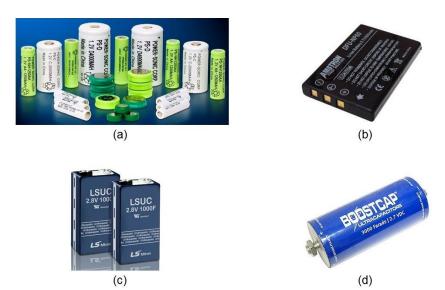

- Figure 3.1: (a) Family of Ni-MH battery family. (b) Li-ion battery. (c) 1000F rectangular supercapacitor. (d) 3000F cylindrical supercapacitor. All images were taken from [38]–[41] respectively.

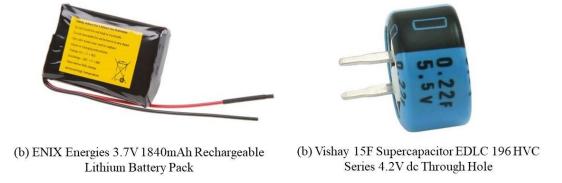

- Figure 3.2: Rechargeable battery and supercapacitor used in this thesis.

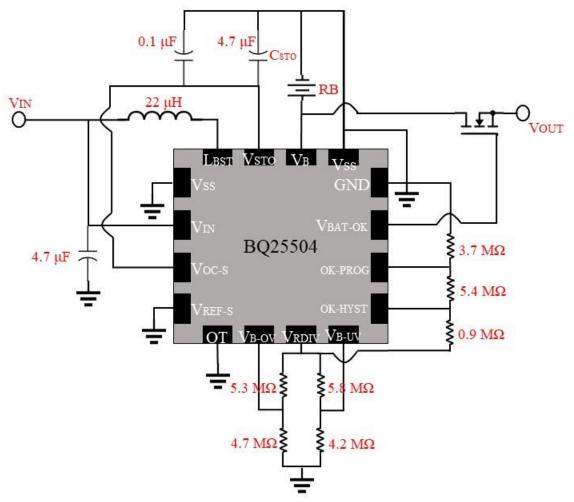

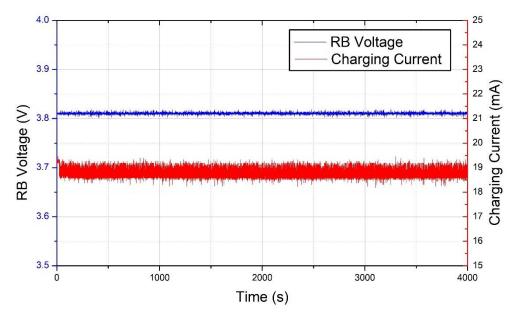

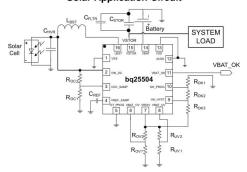

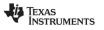

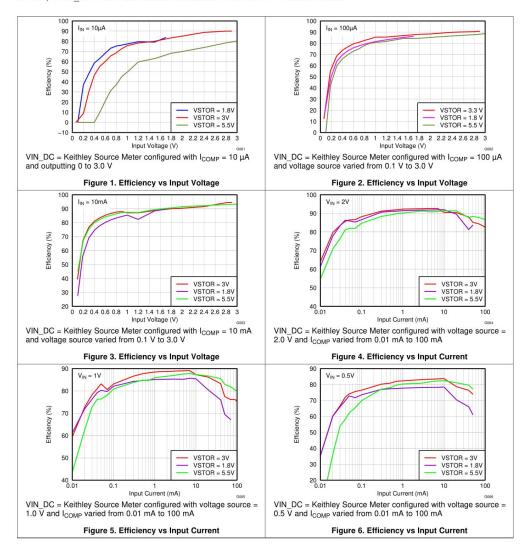

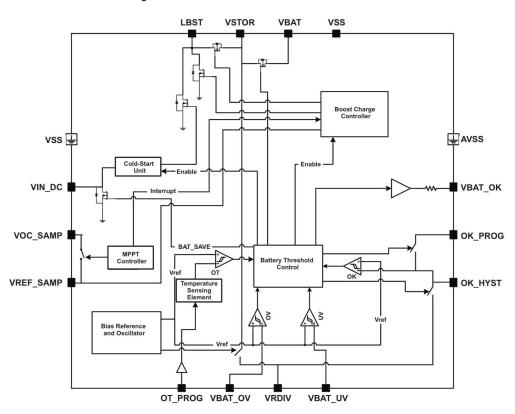

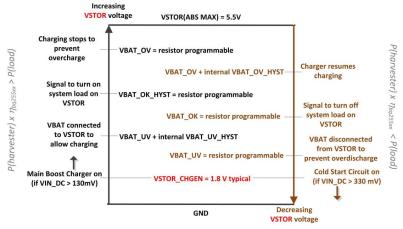

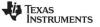

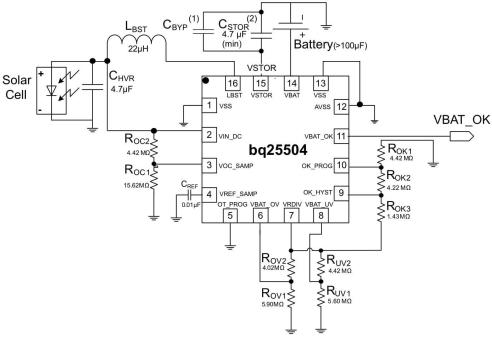

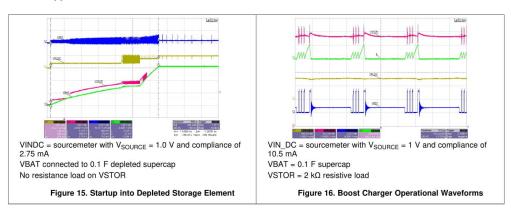

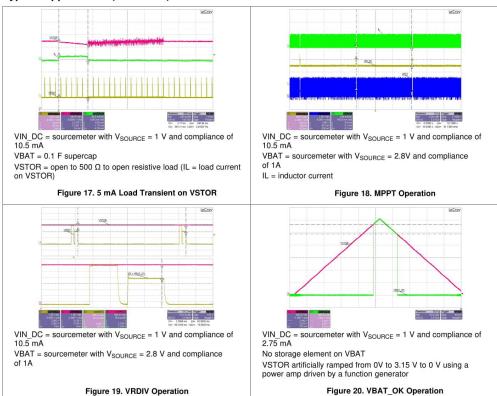

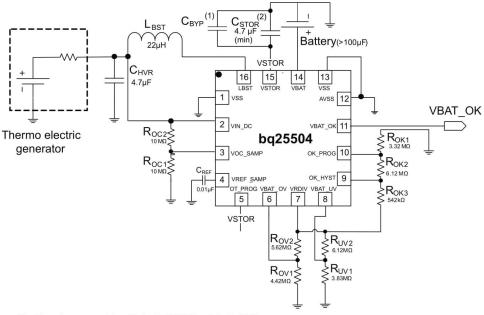

- Figure 3.3: Circuit configuration and voltage programmed level for BQ25504.

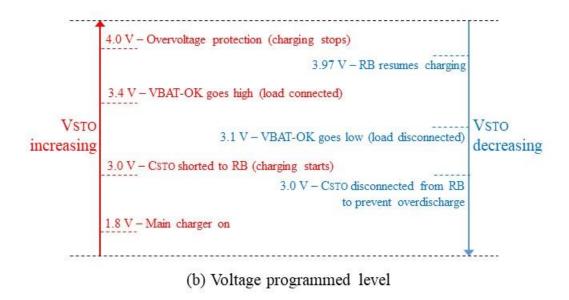

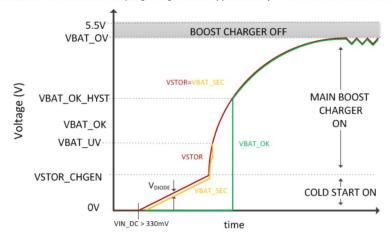

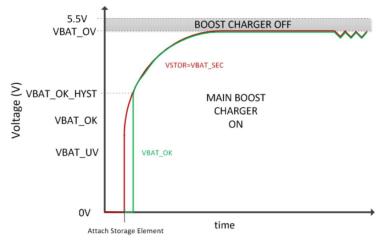

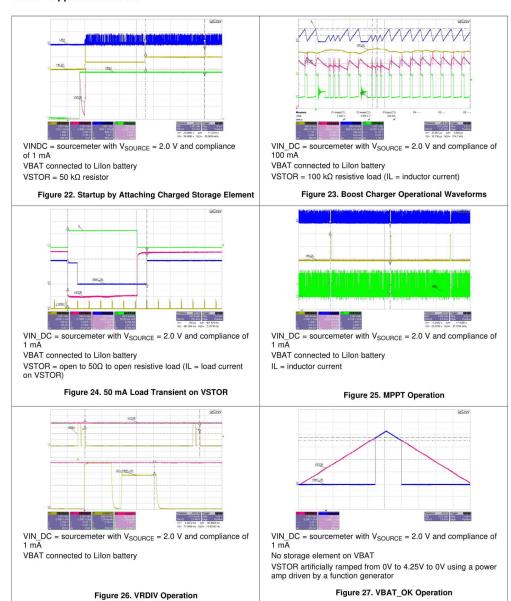

- Figure 3.4: Charging profile of the constructed circuit.

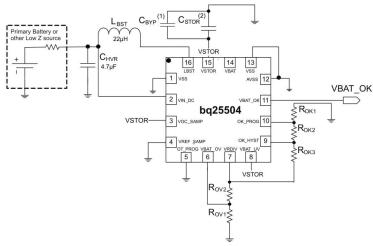

- Figure 3.5: Charging circuit for SC.

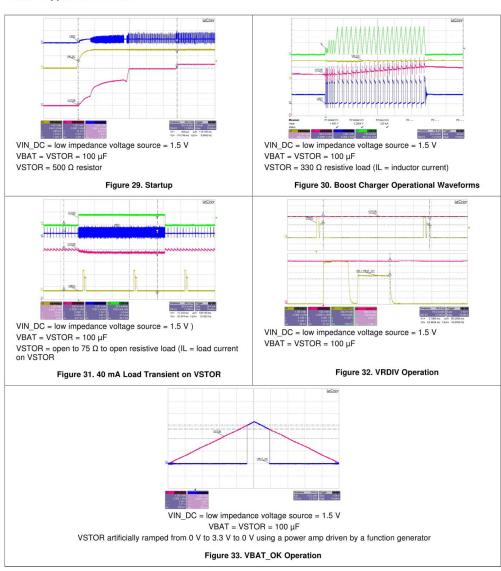

- Figure 3.6: Charging profile for SC.

- Figure 3.7: Converter loadline and efficiency for both discharging circuits.

- Figure 3.8: Operating mode at each bus voltage level.

- Figure 3.9: Configuration for the bus voltage dependent mechanism and the comparator.

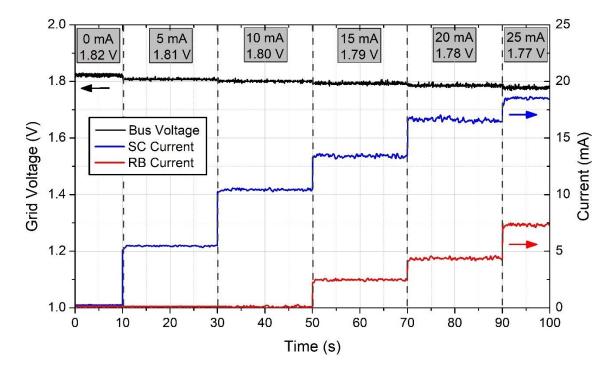

- Figure 3.10: Results from the bus voltage dependent mechanism configuration.

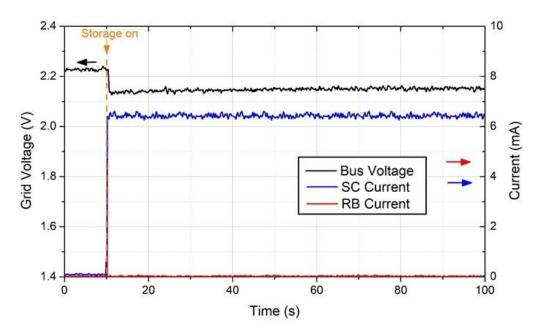

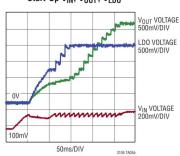

- Figure 3.11: Start-up profile for the pico-grid.

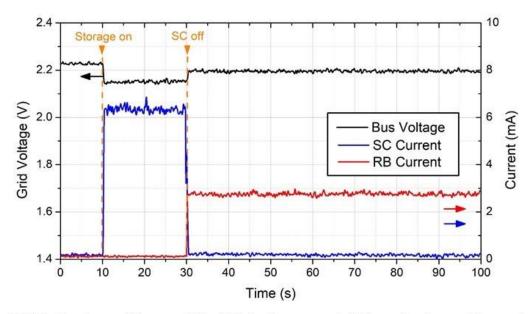

- Figure 3.12: No source condition whilst load is connected to the system.

- Figure 3.13: No load condition whilst SP1 and SP2 are connected to the DC bus.

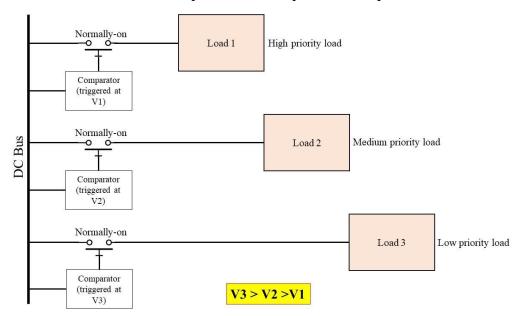

- Figure 3.14: Proposed load shedding mechanism.

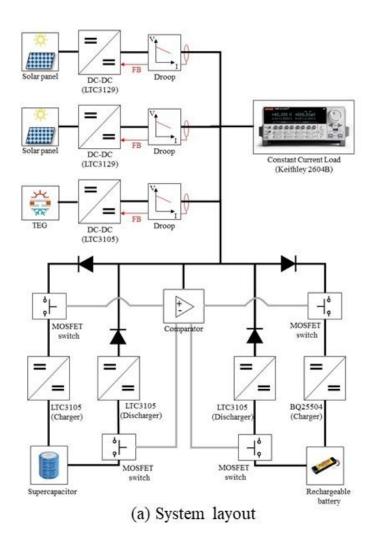

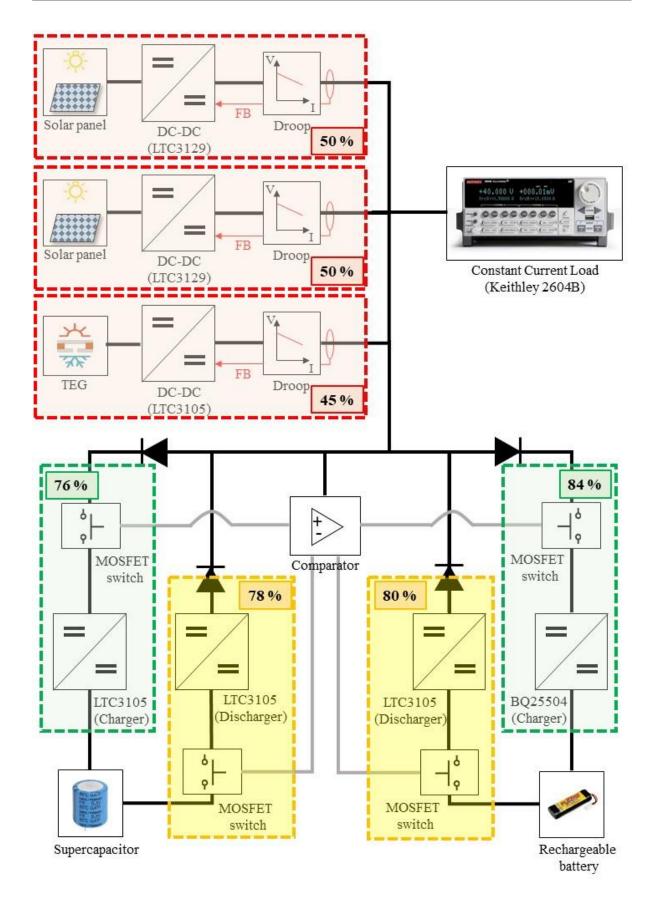

- Figure 4.1: System layout and test rig for the final system.

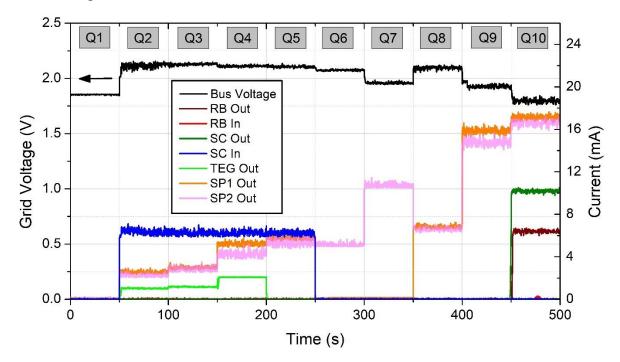

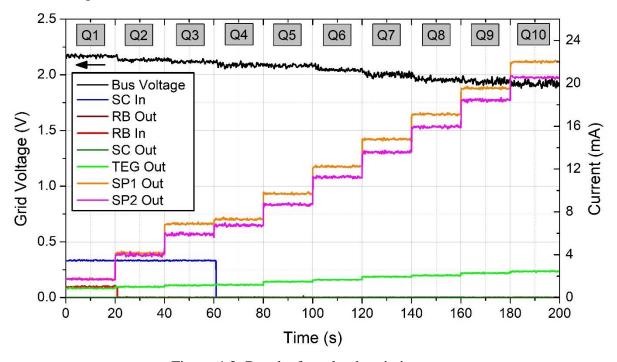

- Figure 4.2: Results from the plug-and-play test.

- Figure 4.3: Results from load variation test.

- Figure 4.4: Efficiency of each of the subsystems. The efficiency presented here has taken into account the power consumption of the droop/mode select circuitry.

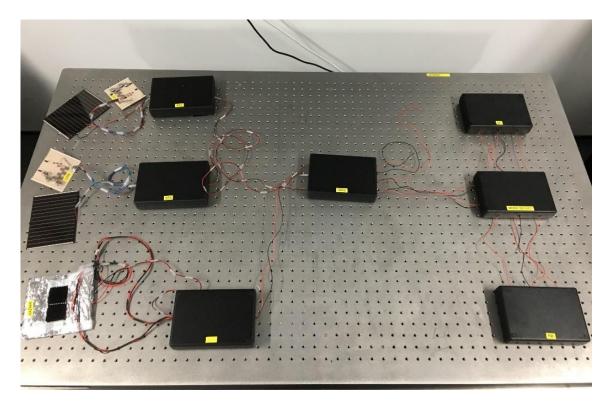

- Figure 4.5: The prototype. Each enclosure contains a full circuitry for each subsystem.

- Figure 4.6: The prototype when attached to a jacket.

- Figure 4.7: Scope view for the bus voltage of the wearable prototype.

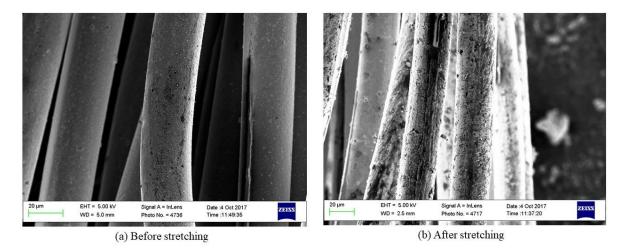

- Figure 4.8: SEM images show each yarn in the silver fibre in a good and new condition (left) and after multiple stretching (right). The samples used for both images are different.

- Figure 5.1: The need for a flexible diode for AC-DC rectification for AC energy harvesting mechanisms in WSN or WBAN applications.

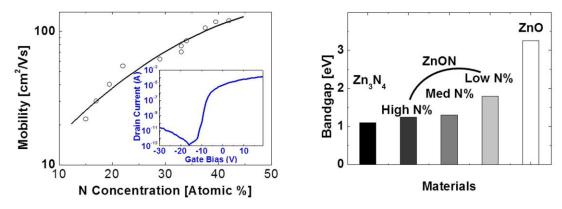

- Figure 5.2: The variation of mobility and bandgap of ZnON film with nitrogen content taken from [70].

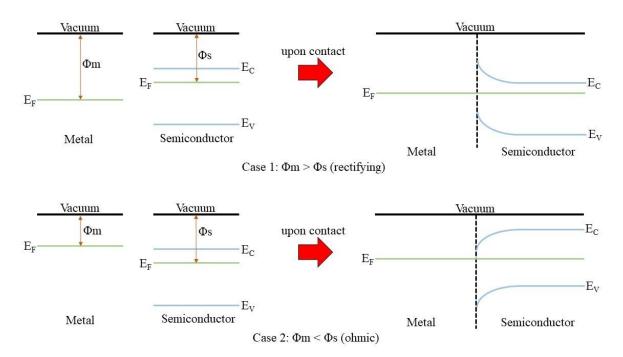

- Figure 5.3: Energy band diagram of MS contact at thermal equilibrium. The metal work function and semiconductor electron affinity both would define the operation of the contact.

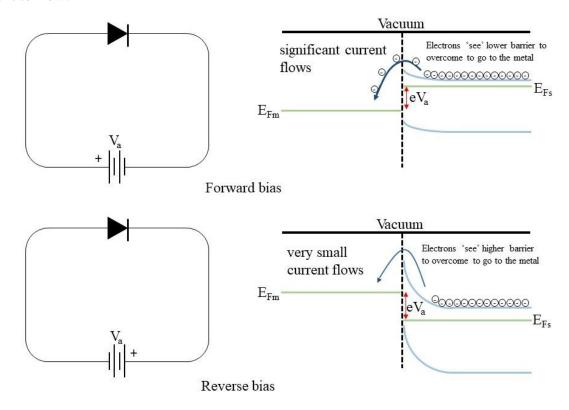

- Figure 5.4: Energy band diagram for a Schottky diode under forward and reverse bias condition.

- Figure 5.5: Structure and 3-D view of the fabricated diode. The shadow mask used in the fabrication is also shown here.

- Figure 5.6: MVSystems cluster tool deposition system used in the fabrication process.

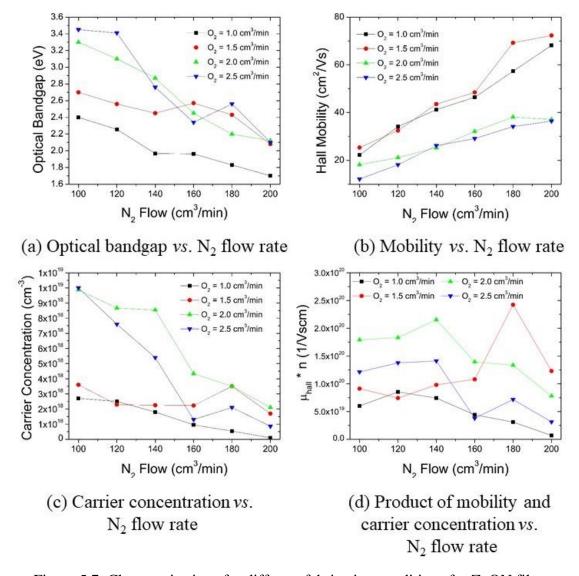

- Figure 5.7: Characterisations for different fabrication conditions for ZnON film.

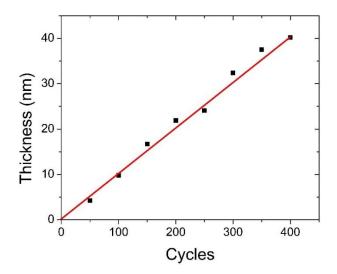

- Figure 5.8: Thickness of Al<sub>2</sub>O<sub>3</sub> film deposited from the ALD process obtained from the profilometer as a function of number of cycles.

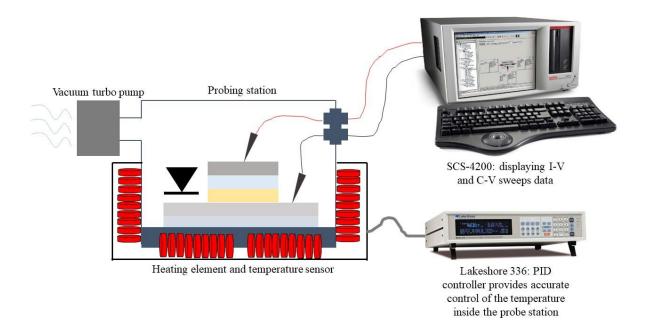

- Figure 5.9: Characterisation setup of the fabricated diode.

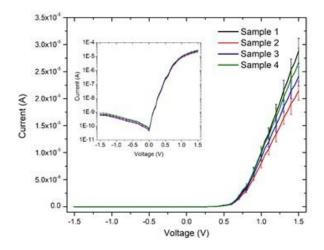

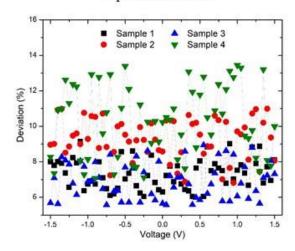

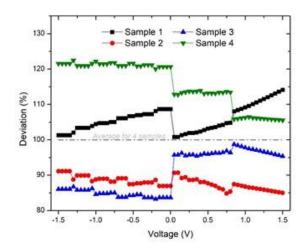

- Figure 5.10: Reproducibility of the performance of the diode for an as deposited film demonstrated by the fabrication of 4 samples from different batches.

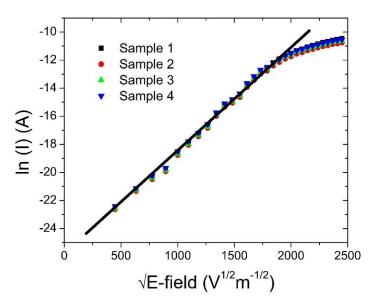

- Figure 5.11: Evidence of the formation of Schottky contact and thermionic emission transport mechanism in the fabricated diode.

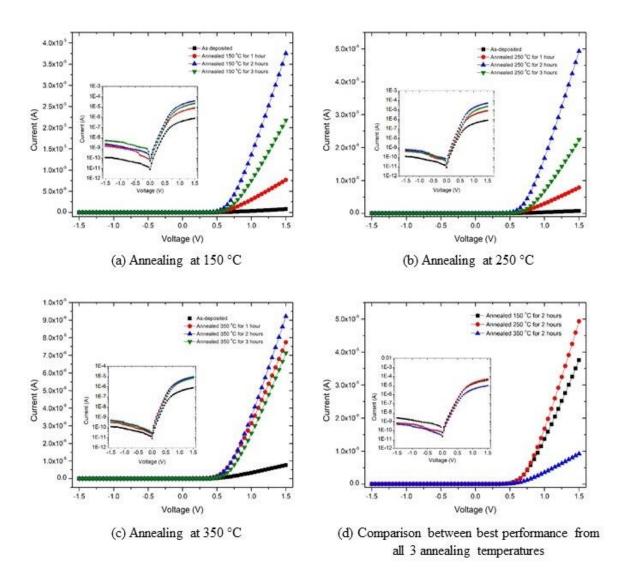

- Figure 5.12: Effects of post deposition annealing with different temperatures and duration to the performance of the diode.

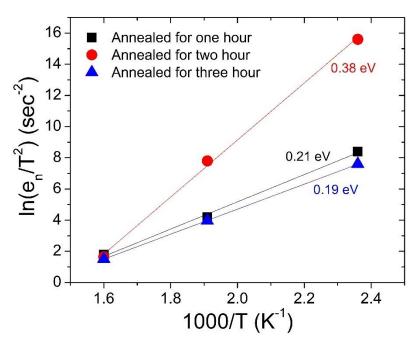

- Figure 5.13: Arrhenius plot to obtain the thermal activation energy of the traps in the diode.

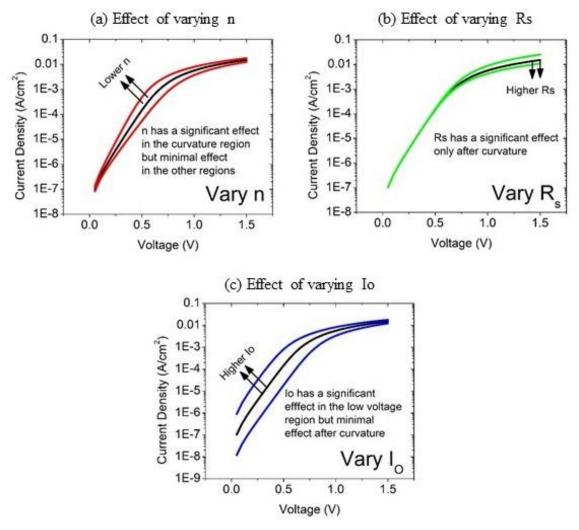

- Figure 5.14: Effects of varying specific parameters whilst maintaining other parameters as constant on the overall shape of the graph.

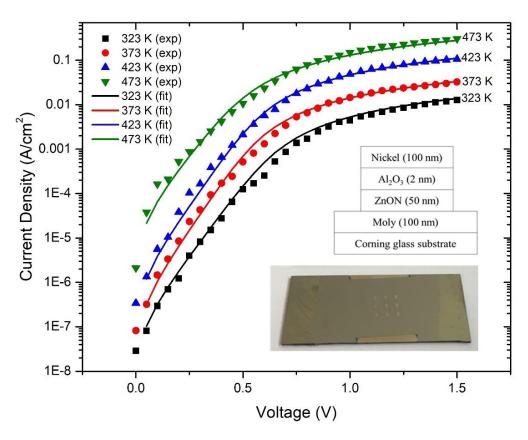

- Figure 5.15: Experimental and fitted curve for J-V temperature dependent measurements.

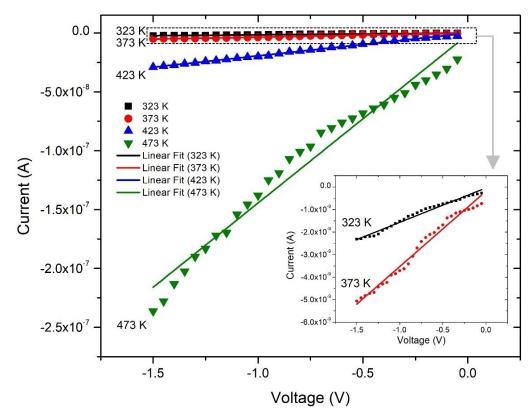

- Figure 5.16: Temperature dependent reverse bias experimental and fitted I-V data.

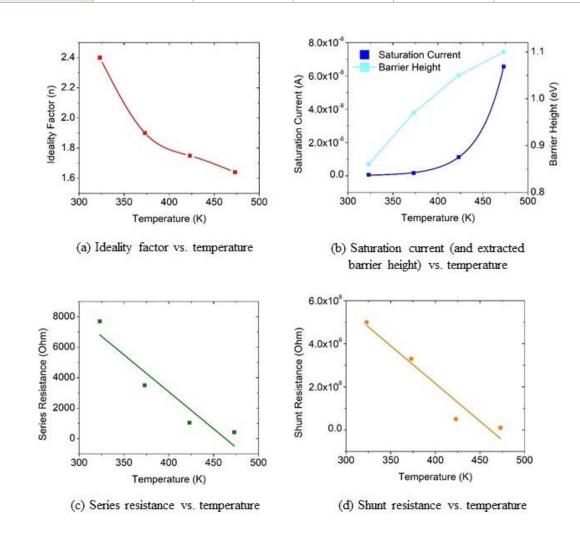

- Figure 5.17: Trends of each extracted parameter against temperature.

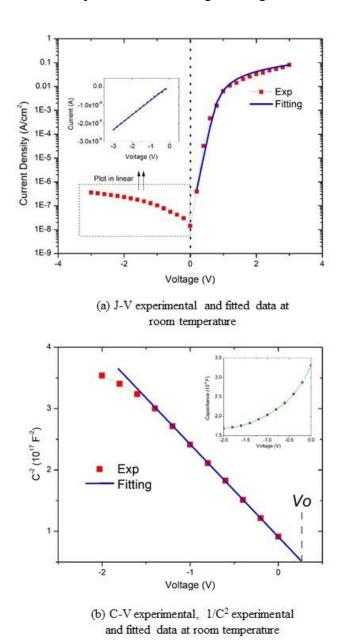

- Figure 5.18: J-V and C-V data and analysis at room temperature.

- Figure 6.1: I-V characterisation result for the ISO MIS diode.

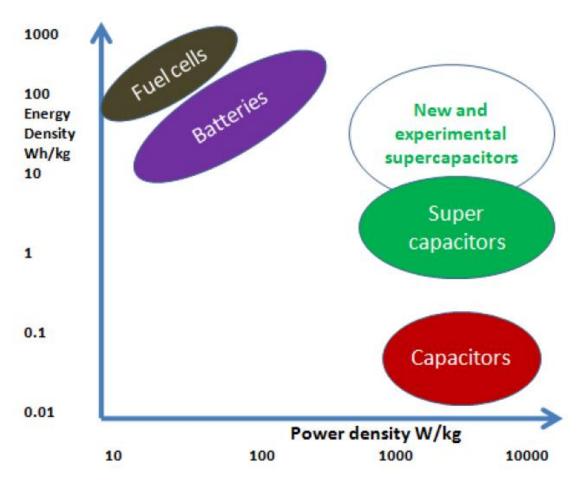

- Figure 7.1: Ragone chart for different energy storage technology [45].

- Figure 7.2: Programme in Wolfram Mathematica used to plot the I-V curve of the diode.

### **List of Tables**

- Table 2.1: Illumination level

- Table 2.2: Parameters for the solar panel for all illuminations

- Table 2.3: Extracted parameters for the TEGs under different temperature differences,  $\Delta T$ .

- Table 2.4: Parameters for droop voltage and full load.

- Table 3.1: Value of resistors in the voltage divider network.

- Table 4.1: Data from the plug-and-play test.

- Table 4.2: Data from load variation test.

- Table 4.3: Weight of each subsystem in the prototype.

- Table 5.1: Deposition process parameters for ZnON and Al<sub>2</sub>O<sub>3</sub>.

- Table 5.2: Extracted parameters from the curve fitting method.

- Table 5.3: Extracted parameters from the curve fitting method.

- Table 5.4: Comparison between diode in this chapter and other published work.

- Table 7.1: Comparison between different types of rechargeable battery and supercapacitor [42][44][105].

- Table 7.2: Bill of materials for the constructed prototype.

### **List of Abbreviations**

ac alternating Current

CC-CV constant current-constant voltage

CMOS complementary metal-oxide-semiconductor

COTS commercial-off-the-shelf

dc direct current

EDLC electric double layer capacitor

EM electromagnetic

ESR equivalent series resistance

GPS global positioning system

HEV hybrid electric vehicle

IC integrated circuit

IoT Internet-of-Things

I-T-V current-temperature-voltage

I-V current-voltage

JST Japan solderless terminal

LDO low-dropout

LDR light dependent resistor

MIS metal-insulator-semiconductor

MOSFET metal-oxide-semiconductor field-effect transistor

MPP maximum power point

MPPT maximum power point tracking

MS metal-semiconductor

NTC negative temperature coefficient

OCV open circuit voltage

PCB printed circuit board

PCE power conversion efficiency

PnP plug-and-play

PTC positive temperature coefficient

P.U per unit

P-V power-voltage

RB rechargeable battery

SBD Schottky barrier diode

SC supercapacitor

SEM scanning electron microscope

SG specific gravity

SOC state of charge

SP1 solar panel 1

SP2 solar panel 2

TCO transparent conductive oxide

TEG thermoelectric generator

TFT thin film transistor

UVLO undervoltage-lockout

V-I voltage-current

WBAN wireless body area network

WSN wireless sensor nodes

ZnO zinc oxide

ZnON zinc oxynitride

### **List of Publications**

#### **Publications related to this thesis**

**M. H. B. Mohd Daut**, A. Nathan, "Self-Adjusted Voltage Droop Load Sharing Mechanism for Paralleling Multiple Low Power DC-DC Converters for Energy Harvesting Applications", IEEE Transactions on Industrial Electronics, 2018 (submitted – under review).

**M. H. B. Mohd Daut**, D. G. Hasko, A. Nathan, "Picogrid: An Integrated Multiple Harvesters, Energy Storage and Loads System for WSN and WBAN", IEEE Transactions on Industrial Electronics, 2018 (ready to be submitted).

**M. H. B. Mohd Daut**, John F. Wager, A. Nathan, "ZnON MIS Diodes", IEEE Journal of Electron Devices Society, 2018 (submitted – under review).

#### Publication not related to this thesis

M. Y. Fan, **M. H. B. Mohd Daut**, "Unity Power Factor, Voltage Step-Up/Down Conversion Pulse-Width Modulated Switching Rectification for Wireless Power Transfer Receiver", IEEE Transactions on Power Electronics, 2018 (accepted – to appear).

#### Conferences

**M. H. B. Mohd Daut**, Guangyu Yao, Hanbin Ma, Arokia Nathan, "Fabrication and Electrical Characterisations of ZnON MIS Diode", TCM 2016, Greece (oral presentation).

**M. H. B. Mohd Daut**, Arokia Nathan, "Energy harvesting system for wearables", Robinson College Graduate Conference 2016, United Kingdom (oral presentation).

### Chapter 1

### Introduction

#### 1.1 Background and Motivation

Wearable devices are one of the emerging technological applications with a market share that has steadily increased from an estimated \$25 billion (USD) in 2015 to \$35 billion (USD) in 2018. It is forecasted to grow further to \$150 billion (USD) in 2026 [1]. Immense interest particularly in health related devices has flourished and attracted multiple investments and resulted in the birth of many start-up companies focusing on this area. Whilst the first generation devices mostly serve as a complement to smartphones, the second generation and latest trend tends to move towards 'embrace devices', which are autonomous devices capable of carrying out specific tasks and functionality without the assistance of smartphones and capable of communicating with other devices through the emerging concept of 'Internet-of-Things'. With the current trend, it is expected that in the future, many wearable devices will be worn by a single person, each carrying out a different and specific set of functions, and autonomously functioning with or without communications between them, as illustrated in Figure 1.1.

The nature of wearable devices which should be small, light, and compact would limit the battery size, and as a result, many of these devices are designed to have a very low power consumption to prevent the need of frequent recharging or battery replacement (typically from nW to mW). Moreover, most wearable devices are related to monitoring (body temperature,

glucose level, blood pressure *etc.*) or manually activated functionality (GPS, running timer *etc.*), which means that these devices mostly spend their time in 'sleeping' or 'standby' mode, which consume a very low quiescent power. In this aspect, there is an opportunity to power up these devices directly from the energy harvested from the human body. In recent years, the concept of energy harvesting has sparked an interest throughout the industry, and the number of publications related to this field has increased dramatically. Ever since its first proposal in a scientific publication by Starner in 1996 [2], the concept of harvesting energy from the human body is becoming more realistic now than it was 20 years ago as there has been an increase in the introduction of the energy harvesters or transducers that are capable of offering good efficiency, supported by the decreasing power consumption of most electrical and electronic devices. The interest to integrate energy harvesting mechanism into wearable devices arises due to few advantages. These include the reduction of system cost, less impact to the environment, less maintenance, and the possibility to further scale down the devices.

Figure 1.1: Wearables on a person in the future. Image taken from RoweBots [3].

The human body is an abundant energy generator, however with a low mechanical efficiency of around 15 -30 % which results in a lot of energy available to be harvested via various mechanisms. To put this into perspective, the daily amount of energy used by a human body is approximately 10 MJ (equivalent to 800 typical AA batteries or 0.2 kg of body fat), and based

on the metabolic efficiency alone, a significant amount of energy is released into the surroundings, mainly in the form of heat [4]. There are two main types of mechanism to harvest this energy; thermoelectric and through motion and vibration. Another possibility is to harvest energy from the surroundings through wearable harvesters or transducers, such as the concept of wearable solar panel and wearable electromagnetic wave rectenna.

Thermal energy from the human body can be harvested to produce electrical energy by means of thermoelectric devices. These devices contain thermoelectric material which can generate electrical voltage from temperature differences (Seebeck effect). Since the human body is continuously regulated to be at 36 °C, a significant amount of heat (up to 100 W [5]) is released to the surroundings. By placing thermoelectric generators on the human body, energy can be harvested from the difference between the body temperature and the surrounding temperature. The amount of harvested energy mainly depends on the magnitude of temperature difference and the surface area of the thermoelectric generator. Using this method, typically around few  $\mu$ W to mW can be harvested from a single thermoelectric generator placed on the human body.

Three main transducers are used to harvest energy from the motion and vibration of the human body. These are piezoelectric transducer (utilises piezoelectric material which can generate voltage when it vibrates), electromagnetic induction (utilises magnetic material to generate voltage from motion based on Faraday's law), and electrostatic transducer (varying capacitance under constant charge or constant voltage condition). Unlike thermal energy, motion and vibration energy is not continuously available to be harvested except when the human body is in motion. Generally, the amount that can be harvested from this method is in the  $\mu W$  range.

Apart from harvesting energy directly from the human body, it can also be used as a transducer to harvest energy from the surroundings. This is the case for electromagnetic wave (EM), in which the human body can act as an antenna to pick up this signal. Human tissues have a very high dielectric constant and can be easily coupled with a low frequency EM wave. This will then generate electricity in the human body, due to its conductive property. However, the amount of energy that can be harvested from this method is very low (approximately 50  $\mu$ W from [6]). Finally, by placing a wearable solar panel on human body, a significant amount of energy can be harvested from the surrounding illumination. For example, an integrated jacket with 16 solar panels has been demonstrated capable of generating 0.5 W of power during sunny day [7]. The method of harvesting energy from the human body and surrounding is presented in Figure 1.2.

Figure 1.2: Mechanism to harvest energy from the human body and surroundings to generate power for wearable devices. Images taken from their respective publications in [7]–[14].

Wearable devices will require a steady dc supply voltage in order to operate reliably. In order to power up wearable devices from the energy harvested from the human body, a power converter is needed as the front-end interface (rectifier or DC-DC converter). This power converter needs to be a low power converter. Furthermore, energy buffer/storage is also needed in order the support the intermittent nature of the energy harvester. The full system of wearable devices with energy powered from the human body would comprise all of these elements; energy harvester, power converter, energy storage, and wearables as shown in Figure 1.3.

Figure 1.3: System architecture of a wearables with its own energy harvester and energy storage.

From this, a major problem could potentially arise and subsequently an opportunity presents itself. In the future, it is forecasted that a human body would have a lot of wearable devices, and if each system were to be integrated with an individual dedicated energy harvester, then there would be multiple harvesters and multiple energy storage on a human body, which is an inefficient approach. Moreover, some energy harvesters are needed to be placed on a specific location on the human body for maximum efficiency but wearable devices may be worn on other parts of the body. There exist an opportunity for the harvesters and storage system for all of the wearable devices to be tied together to a single unit, reducing the size and weight of the whole system. If we can imagine that a human body is like a big city with multiple localised power plants (energy harvester and storage), multiple residential houses and industrial areas which consume power (wearable devices), and a big overhead cable connecting them together (conductive fibre through clothing), then we can imagine that the whole system can be modelled as the electricity grid system. From this, the concept of pico-grid, which is a low power grid system designed specifically to harvest energy from human body and distribute this energy to power up wearable devices is proposed, designed, and discussed.

### 1.2 Aim and Objectives

The main aim of this PhD project is to demonstrate a working prototype of a multiple energy harvesters system designed to power up multiple low power loads through a single link system. The introduction of the system itself which is named as a pico-grid, since it is possibly the smallest possible scale of the grid system, is the main contribution of this PhD. The main focus of the PhD is therefore to design an integrated system of these multiple sub-systems, and to ensure a seamless operation of the integrated system.

In order to achieve the main aim, the objectives that need to be completed include:

- Define the operation modes and parameters of the proposed pico-grid system, such as system architecture, power flow control, and voltage range.

- Design each sub-system independently within the set operation in order to ensure that each system can work independently before integrating them together.

- Determine and design an efficient load sharing mechanism among connected energy harvesters. In the system, the power consumed by all of the wearables will be jointly provided by multiple harvesters at the same time and therefore, a load sharing mechanism is needed to achieve this.

- Determine and design energy buffer and storage charging and discharging mechanism in the pico-grid. Energy storage is a requisite in the system and acts not only as buffer or storage for the harvested energy, but also as a back-up power supply in the case when energy is unavailable from the harvesters. In that sense, this sub-system serves either as a load or power source, depending on the power level in the system bus.

- Design a cut-off mechanism and load shedding operation in order to ensure the safety and reliability of the pico-grid system.

- Demonstrate the integration of each sub-system and a final working prototype of the picogrid system. The performance of the system will be analysed to ensure it meets the specifications set for the application requirements.

It should be noted that the pico-grid system is a system that comprises many sub-systems, and whilst each sub-system can potentially be further optimised to suit the overall operation of the integrated system, the main focus of this PhD project however is not to design and optimise each system but rather focus on introducing the system itself and to demonstrate an approach of systematic integration of each sub-system in order to achieve a working pico-grid prototype.

#### 1.3 Pico-grid

One of the most important innovations that has driven industrial and technological revolutions and enabled the development of a modernised world is the grid system. This system has enabled power to be delivered to any remote area from far away sources. Grid system is an autonomous interconnected system comprised of multiple energy sources and multiple loads connected via overhead cables (national grid).

The concept of a grid can be scaled down and applied exclusively on human body to power up wearable devices as shown in Figure 1.4, and is called 'pico-grid'. In this, a system of energy harvesters and multiple wearable devices are connected through a single bus, where the power flow takes place.

Since most wearable devices require a dc supply voltage, and since some energy harvesters generate dc voltage, the link which connects all of the elements together is proposed to be operated in dc. Plus, energy storage such as rechargeable battery and supercapacitor are also in dc, therefore by using a dc link bus, the need for any rectifier or inverter is eliminated and thus increases the efficiency of the system. This is unlike the typical grid system, which is mostly operated in ac. However, there is an emerging concept of a dc micro-grid, which is a small scale localised grid system connected to the main grid system and capable of providing and generating power on their own.

The pico-grid is proposed to be operated at 2.2 V, since this voltage is an intermediate level between a typical li-ion rechargeable battery (3.7 to 4.2 V) and the expected voltage produced by the energy harvesters (in the range from few mV to 1.5 V). Furthermore, most wearable devices require a dc supply voltage in the 5 V vicinity, which makes 2.2 V a good choice for the bus voltage. The voltage cannot be too low or too high from this range as the DC-DC converter would be pushed to the limit in order to provide a higher step-up or step-down ratio, which in turn would generate high losses and reduce the efficiency of the entire system.

The system architecture of the pico-grid is shown in Figure 1.5. There are two main operations, determined by the control system, and defined by the amount of available power and load demand:

• Condition 1 – power produced by energy harvesters is the same or higher than the load demand, in this case, the excess available power is used to charge the storage system.

Condition 2 – power produced by energy harvesters is lower than the load demand, in this

case, the storage system will discharge to support the load demand. If the demand is still not

met, then load shedding process will start based on the priority of the loads.

Finally, since pico-grid is used to supply power for wearable devices, the plug-and-play functionality is one of the required features in the system. The pico-grid will be designed to enable plug-and-play functionality not just for the wearable devices, but also for the energy harvesters.

Figure 1.4: The final prototype proposed for the pico-grid system on human body.

Figure 1.5: System architecture for pico-grid system.

#### 1.4 Thesis Outline

The contents of this thesis encompass the design, construction, testing, and evaluation of each sub-system related to the pico-grid system. After each sub-system has been designed and tested to ensure individual successful operation, all sub-systems are integrated together to form the full working system prototype, which is then tested and evaluated.

Chapter 2 provides an overview and overall design for the control system for the harvester converters to ensure successful parallel load sharing operation. The theory for load sharing is presented and discussed at the beginning of the chapter, and then the control design based on the proposed droop mechanism is presented, simulated, and discussed. Solar panel and thermoelectric generator (TEG) are selected to be the main energy harvesters. As the nature of the output power for these harvesters is time-varying, the droop mechanism needs to be designed to follow the variation of this power, to ensure maximum power is capable to be delivered to the load. Finally, the construction of multiple source converters for these harvesters with the proposed self-adjusted droop control system is presented and the performance is evaluated.

Chapter 3 presents the power flow operation for the power converters for the storage system which serves as the backbone for the pico-grid operation. A supercapacitor and rechargeable battery are selected as the main energy storage element. The mode select circuit to control the power flow for charging and discharging mechanism is presented and tested. Several important operations such as start-up operation are presented and evaluated. The proposed mechanism for load shedding is also presented and discussed. Experiments and tests are carried out to test the feasibility of the proposed mechanism and the performance is presented and discussed.

Chapter 4 which is the most important chapter presents the integration steps of the whole subsystems and discusses and evaluates the performance of the entire system. The first wearable prototype is built from the integrated system and the performance is evaluated. Few recommendations for improving the first prototype in order to be implemented in real world applications are outlined by the end of the chapter.

Chapter 5 presents an additional side project during the PhD involving fabrication and electrical characterisation of ZnON thin film diode in MIS structure which could potentially be deposited on a flexible substrate. This diode is initially intended to be implemented as a rectifier circuit

for energy harvesting applications. The results for the fabrication and subsequent temperature dependent I-V and C-V characterisations are presented and discussed.

Finally, the conclusions and future work are presented in Chapter 6.

### Chapter 2

# Parallel Load Sharing – Theory and Demonstration

#### 2.1 Foreword

In this chapter, the concept of simultaneously extracting energy from multiple harvesters is proposed, discussed, simulated, and demonstrated. This operation of load sharing among harvesters is a very important feature of the pico-grid system (multiple sources multiple loads), which differentiates it from the typical single source single load or single source multiple loads systems. The control method to achieve a seamless load sharing operation is presented and discussed. This method which relies on the concept of voltage droop regulation is further improved by integrating a self-adjusted feature to ensure that the variation of input power is considered. Finally, a multiple sources multiple loads system is built from commercial-off-the-shelf (COTS) components and the functionality of the load sharing concept is demonstrated.

#### 2.2 Background and Theory

#### 2.2.1 The Need for Multiple Multitype Energy Harvesters

Recently, the concept of WBAN has surfaced and attracted significant attention throughout the wearables industry [15]. In this system, a network of wirelessly interconnected sensors on human body work together to sense and monitor certain parameters of the body, which are mostly health-related, and send the signals to the processing centre, normally to a mobile phone, to alert the user on any fore coming health issues. This concept is very similar to the

WSN, in which a network of multiple sensors works autonomously and send signals to the central processor. These concepts are all related to the emerging concept of Internet-of-Things (IoT), in which multiple sensors, devices, appliances, and almost any product, are wirelessly connected and capable of exchanging data, sending instructions and commands, enabling wireless integration of almost every aspect of electronics devices. For WBAN and WSN, since most of the networks comprise sensors, therefore the power consumption of each node is very low. Traditionally, this is powered by a rechargeable battery. However, major drawbacks associated with a rechargeable battery such as a frequent charging requirement, performance degradation over time, operation sensitivity over a specific temperature range, and eventually the need for a replacement have made the integration of energy harvesting mechanism into these systems a more logical and realistic approach. Furthermore, multiple researchers have introduced efficient energy harvesters that can harvest and scavenge enough energy to sustain the operation of these wireless nodes. Multiple standalone sensor node systems powered by a single energy harvester have been introduced in the publications [16]–[19]. However, the intermittent and sporadic nature of the power output of most energy harvesters means that integration of energy storage is still a requisite requirement in these systems. This means that the nature of the harvester itself defeats the purpose of having the harvester in the system to replace the rechargeable battery. To counter this particular issue, the use of multiple and multitype energy harvesters in the system is introduced. Multiple harvesters with different energy harvesting or scavenging mechanisms (hence multitype) are needed to ensure a higher opportunity for a continuous supply of power, hence capable of sustaining the operation of these systems.

To reduce the overall footprints of the multiple energy harvesters, a single cell comprising multiple and multitype harvesters has been proposed. For example, recently Guo *et al.* [20] have introduced a hybrid triboelectric-electromagnetic generator capable of harvesting mechanical energy from harsh environments. The weakness with their generator is the harvesting mechanism solely relies on surrounding mechanical energy, and when this one type of energy is unavailable, then the amount of harvested power depletes to zero. A better solution to this type of hybrid energy harvester is a generator that can harvest multiple surrounding energy at once, such as the one demonstrated by Wu *et al.* [21], which is capable of harvesting mechanical, solar, and chemical energy at the same time. Other examples are demonstrated by Zheng *et al.* [22] and Lee *et al.* [23]. However, these papers do not outline another challenging

aspect associated with multiple and multitype harvesting system, which is how to extract and deliver the energy from all of these sources simultaneously to the target load.

Figure 2.1: (a) shows a multiple multitype energy harvesting system proposed by Lemey *et al.* [24]. The red oval shows the OR-ing diode configuration. (b) shows the actual depictions of the system on the human body. Images taken from [24].

Multiple methods have been proposed in the literature in relation to the power flow management and connectivity between multiple and multitype energy harvesters in a single system. The most common method of connecting two or more energy sources is through the power OR-ing method, in which every source is connected in parallel to a common link through a passive diode or a transistor in diode configuration. This diode serves to prevent each harvester to be perceived as a load by other harvesters, thereby preventing the power to flow to the harvester. Although this method ensures that the power is always delivered to the load if at least one of the sources is generating power, it suffers from energy wastage if two or more sources are generating power, since only the source with the highest voltage will be connected to the load. If the sources are energy harvesters, then the energy harvested by only one harvester with the highest voltage will be delivered to the load, regardless of the availability of another harvester with a higher power. For example, Lemey et al. [24] have demonstrated a system in which the large area around the antenna integrated in smart fabric interactive textile (SFIT) for WBAN is utilised for a multiple energy harvesting system. In their system, they used TEGs and solar panels with OR-ing diodes connected between them to supply COTS chip MAX 17710 to deliver regulated power to the load and charging battery at the same time. The main issue with their system is the OR-ing diodes which prevent the power to be extracted from both harvesters at the same time. However, this work is probably the closest concept to a pico-grid system, in which multiple harvesters are integrated together on human body in a single system

as shown in Figure 2.1. The same direct connection with the OR-ing mechanism is also presented by Tan *et al.* [25], Romani *et al.* [26], and Carli *et al.* [27] as shown in Figure 2.2.

Figure 2.2: Multiple multitype energy harvesting systems using OR-ing method reported in publications; (a) from [25], (b) from [26], (c) from [27]. Red ovals show the OR-ing configuration.

In the previous OR-ing configuration, one of the criteria that must be met by the energy harvesters in order to ensure successful delivery of power to the load is that the voltage produced by the harvesters must exceed the diode turn-on voltage, which is around 0.7 V for COTS silicon p-n diode, 0.3 V for COTS Schottky diode, and the threshold voltage of the COTS transistor for passive diode configured from a transistor. This means that some high power low voltage energy harvesters such as TEG would have difficulty to get its power transferred to the load. Furthermore, even for those harvesters that generate enough voltage to barely exceed this turn-on voltage, power loss incurred in terms of voltage drop across the diode would be enormous, further reducing the magnitude of power delivered to the loads. To counter this problem, the voltage of the harvesters is stepped up by the means of a power converter before the OR-ing diode as demonstrated by Magno *et al.* [28]. Another method of using a low drop-out (LDO) voltage regulator to replace OR-ing diode, hence increasing the overall power transfer efficiency was also demonstrated by Farrarons *et al.* [29]. However, the main issue associated with the power OR-ing method, in which only one harvester will be

connected to the load regardless of the availability of other harvesters still exists. Moreover, the power consumption of the power converter itself must be taken into consideration when evaluating the performance of the whole system.

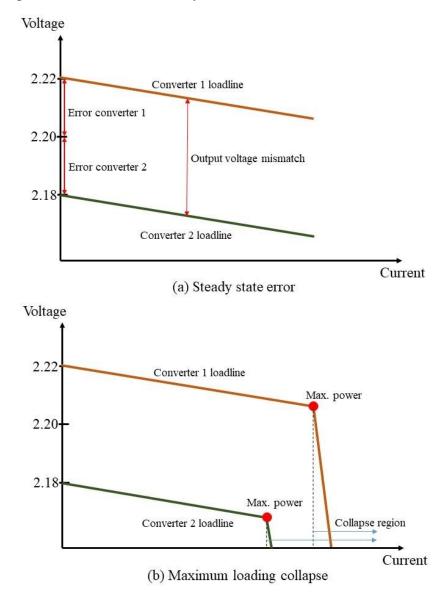

Figure 2.3: Difficulty in OR-ing configuration due to the output voltage mismatch.

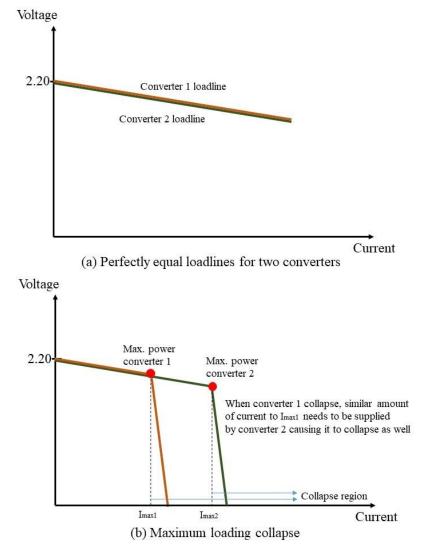

It can be argued that in the OR-ing configuration, if the output of each parallel-connected converter is tuned to produce a similar level of voltage, all converters will be able to deliver current to the load at all times. However, this is very difficult to achieve and may even lead to the collapse of the system due to two main reasons. The first reason is the difficulty to achieve a perfectly equal output voltage for all converters with the presence of steady state error in the output voltage. This can be further explained in Figure 2.3. In Figure 2.3 (a), assuming both converter 1 and 2 are tuned to produce 2.2 V, and if converter 1 outputs 2.22 V and converter 2 outputs 2.18 V under no load condition due to their steady state error, only converter 1 will

be connected to the load. Converter 2 will be connected to the load if the voltage level in converter 1 drops to its actual output voltage; 2.18 V due to the internal droop in converter 1. However, if the power rating in converter 1 is low and could collapse before the output voltage reaches 2.18 V, then it would collapse first even before converter 2 is connected to the load, as shown in Figure 2.3 (b). The second reason is the different in power rating between parallel connected converters. This is further illustrated in Figure 2.4. In Figure 2.4 (a), assuming that two converters are connected in parallel and are able to output a perfectly equal output voltage and possess a similar amount of internal droop, if converter 1 has a lower power rating than converter 2, then as the magnitude of drawn current increases, it would collapse and the loading for converter 2 will tremendously increase due to sudden unavailability of converter 1. If the amount of drawn current exceed the power rating of converter 2, then converter 2 will also collapse, and the overall operation of the system will collapse.

Figure 2.4: Difficulty in OR-ing configuration due to the different power ratings.

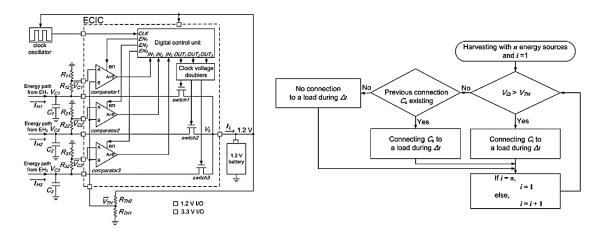

To further improve on this energy harvesting issue, a rapid charge/discharge energy storage such as a supercapacitor that can capture intermittent power is integrated into the system to ensure that all power from the harvesters can be stored first before being transferred to the load, still via a direct parallel connection. In this configuration, typically each harvester has its own dedicated power converter and supercapacitor, and the voltage of the supercapacitor is used as the indication of its storage status and when the energy should be transferred to the load. By using this buffer storage system, the energy from all harvesters can be captured at the same time, thereby eliminating the problem associated with the direct OR-ing configuration. Furthermore, since the load is effectively disconnected from the harvester and power converter during the charging process, the power converter can be easily integrated with MPPT function, further increasing the efficiency of the energy extraction process. This method was utilised by Ambimax [30], which is probably the most cited published work in multiple multitype energy harvesting system. Ambimax was built from COTS components and is capable of harvesting energy from multiple energy harvesters at the same time by integrating a dedicated supercapacitor for each of the harvesters, and when the voltage of the supercapacitor reaches a pre-set threshold voltage, then the node from that supercapacitor is short circuited to the load, thus enabling the power transfer. Another example is Kang et al. [31] who have demonstrated a system with an almost similar mechanism, however in an integrated package. Their proposed system is shown in Figure 2.5. The same concept was also demonstrated by Srujana et al. [32] and Morais et al. [33]. Although the efficiency of energy extraction is increased by effectively harvesting every available energy, the system is incapable of delivering all of the harvested energy at the same time to the load, especially when the power demand from the load is higher than what each single harvester could produce.

Some other methods have also been proposed. Dini *et al.* [34] have proposed a multiple multitype energy harvesting system based on a priority based queuing. In this system, a similar approach of using dedicated supercapacitor and MPPT was used, however instead of using the voltage of the supercapacitor as the connection switching parameter, a set of priority based mechanisms are proposed to transfer the power to the load. The pre-set queue places the harvester with the highest expected power output on the highest priority and when the circuit detects that the supercapacitor associated with this harvester has low power level, the queue will move to the second prioritised harvester, and so on. On the other hand, Shi *et al.* [35] have proposed a timely slot queue mechanism, in which each harvester is allocated a specific time slot to transfer power to the load. In determining the slot queue selection process, the harvesters

with output voltage lower than a pre-set threshold voltage are disabled. Finally, a well-designed system with plug-and-play capability was proposed by Weddell *et al.* [36], utilising a multiplexing method to select the power to be delivered to the load. Their complex system consists of a microprocessor used to store electronics datasheet of each of the elements in the system, and works together with the multiplexer to consistently determine the energy available in each node and transfer this energy to the load depending on the demand from the load.

Figure 2.5: Proposed system by Kang *et al.* [31]. Left shows the circuitry architecture of the energy combiner system and the flowchart of the combiner operation is shown on the right.

Figure 2.6: Multiple energy harvesting system utilising priority based queueing method proposed by Dini *et al.* [34] The system architecture is shown on the left and the operation flowchart is shown on the right.

In all of these reported systems, although the issue of harvesting every available energy simultaneously has been solved, none are capable of delivering power to the load directly and

simultaneously from all energy harvesters at any given time. This will become a major problem especially when the system is used to power up heavy load. In that sense, all of the reported work serve to improve the redundancy of the power by integrating them together to sustain the operation of the system, instead of integrating multiple harvesters to boost the power output capability. Apart from a few, most of the systems do not possess plug-and-play functionality for the harvesters. Furthermore, for systems that rely on a supercapacitor to store energy, between the period in which the supercapacitor is fully charged and the supercapacitor is connected to the load, the energy harvested during this period will not be extracted. It will be shown in the next section by using the method proposed in this work, all of these issues can be solved altogether concurrently.

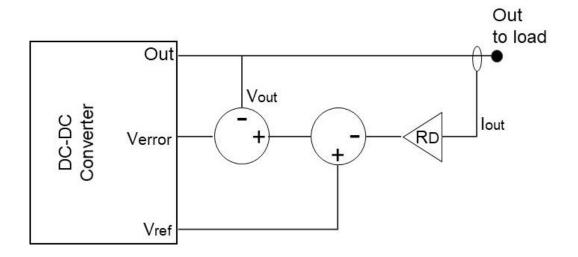

# 2.2.2 Voltage Droop Current Sharing Mechanism

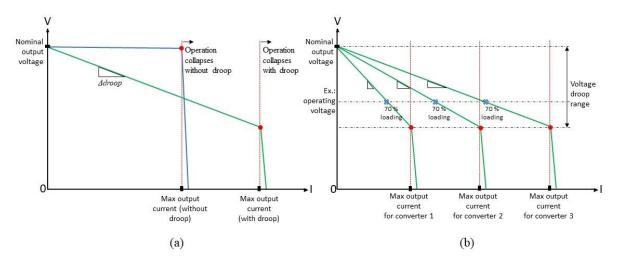

The proposed pico-grid system would comprise multiple energy harvesters, each equipped with a dedicated power converter to regulate the output voltage of the harvesters to meet the input requirements of the DC bus. The purpose of integrating multiple sources in this system is to improve redundancy, reliability, and loading capacity of the output power. Improvement in redundancy and reliability is achieved when a continuous supply of power to the load can be sustained via the introduction of multitype harvesters, which has been accomplished via multiple methods that have been reported in the literature presented in the previous section. On the other hand, improvements in loading capacity involves combining and transferring harvested power to the load altogether simultaneously, which has not been reported elsewhere. To achieve both of these objectives, a method capable of delivering power simultaneously to the load; voltage droop is explored. Voltage droop is defined as an intentional voltage drop of the output of a power converter when its output current is increased. As will be shown later, the introduction of this 'virtual impedance' at the output of a power converter not only would enable multiple power converters connected in parallel to simultaneously deliver power to the load, but can also be utilised to set each converter to share the same magnitude of current in terms of its generation capacity, or per unit (P.U).

When power converters are connected in parallel, there should be a cross regulation between them to enable current sharing. The concept of paralleling multiple power converters has been discussed in great details in publications, such as by Huang *et al.* [37]. In high power systems, this can be achieved through master-slave configuration, in which one master power converter is set to be operated in voltage controlled mode and the other power converters are set to be

operated in current source mode. In this configuration, the voltage is effectively determined by the master controller. Furthermore, in a few cases, the communication link between the controllers of these converters is required, further complicates the overall system architecture. However, in a low power system, this method is not feasible since the configuration consumes a significant amount of power. In this case, a simpler control mechanism is required.

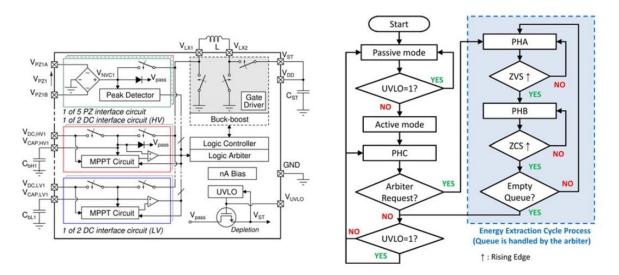

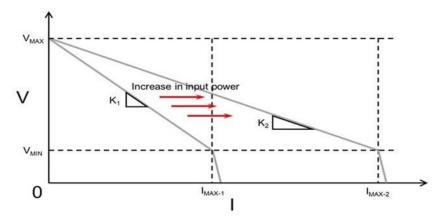

Generally, a DC-DC power converter is designed to output a constant voltage regardless of the output current. However, the presence of parasitic resistance between the output node of the converter and the input node of the load causes the drop of this voltage as seen by the input node. The higher the current drawn from the converter, the higher this voltage drop would be. The idea of voltage droop was derived from this phenomenon, in which an intentional voltage drop can be integrated in the output of the power converter by the introduction of virtual impedance, to shape the V-I loadline of the power converter, as shown in Figure 2.7 (a). This virtual impedance can be integrated in the control loop of the power converter, as will be shown in the latter section. The original loadline of a typical DC-DC converter is shown as a blue line. The voltage collapse region marked as a red dot indicates the collapse of the converter operation when the drawn current exceeds its output power capability. By integrating a virtual impedance, this loadline can be shaped to the steeper green line, enabling higher current to be drawn at lower voltages (same amount of output power).

Figure 2.7: (a) shows the typical loadline of DC-DC converter (in blue) and the modified loadline with droop (in green). (b) shows the connection of three power converters with different rated power connected in parallel.

If the maximum expected output powers for multiple converters are known, then each converter can be designed to have the same nominal output voltage at no load and at maximum load conditions, as shown in Figure 2.7 (b). When these converters are connected in parallel, each converter can supply current simultaneously to the load. Furthermore, current sharing in terms of their generation capacity is automatically achieved. For example, if the power demand from the connected load causing the operating voltage to droop as shown in Figure 2.7 (b), then each converter will supply a different magnitude of current according to their loadline characteristic, however their percentage of the loading is equal (70 % or 0.7 P.U in this case).

## 2.2.3 P.U Equal Load Sharing and Simulation

In order to demonstrate an equal load sharing mechanism achieved via the voltage droop method, a case study and full simulation is presented in this section. In the simulation presented, three energy sources; source 1 with 1 V 0.1 W output, source 2 with 0.8 V 0.5 W output, and source 3 with 3 V 0.25 W output are connected to a common bus, each via a dedicated power converter. For simplicity, it was assumed that the energy sources produce a consistent voltage and are capable of generating maximum power during the whole period of simulation. The load comprises a 70  $\Omega$  resistor, 1  $\mu$ F capacitor, and a 40 mA constant current sink, all connected in parallel. The nominal voltage of the bus was set at 2.0 V for 50 % loading of the system. The droop voltage range of 0.4 V was set from 2.2 V (0 % loading) to 1.8 V (90 % loading).

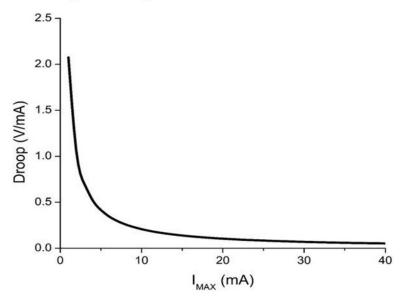

To determine the magnitude of the droop for each converter, the maximum output current of each power converter,  $I_{max \ loading}$  was determined according to the following relation:

$$I_{\text{(max.loading, 90\% loading)}} = \frac{0.9 \times \eta_{\text{converter}} \times P_{\text{harvester}}}{V_{\text{(max.loading, 90\% loading)}}}$$

Here  $\Pi_{converter}$  is the efficiency of the power converter at maximum loading,  $P_{harvester}$  is the maximum output power of the energy harvester, and  $V_{max \ loading}$  is the set output voltage of the power converter at 90 % loading (1.8 V for this case). The efficiency of each converter was assumed to be 90 % for the buck converter and 85 % for the boost converter. The value of 0.9 represents the set maximum loading of the converter in P.U in order to prevent the converter from approaching its full loading, which could possibly collapse the operation of the power converter. From this, the magnitude of the required voltage droop,  $\Delta$ droop was determined from the following relation:

$$\Delta Droop = \frac{V_{(no\,load,~0\%\,loading)} - V_{(max.loading,~90\%\,loading)}}{I_{(max.loading,~90\%\,loading)}}$$

Here  $V_{no\ load}$  represents the output voltage of the power converter at no load (open circuit) condition (2.2 V). From this, the droop regulation and subsequent V-I output loadline of each converter was determined and the results are shown in Figure 2.8. As can be observed from the figure, power converter 1 which outputs regulated voltage from energy source 1 possesses the highest droop due to its lowest power capability, and vice versa. The loadlines for all converters in P.U are shown in the inset figure. The loadlines in P.U are regulated to output the same P.U output current at a specific bus voltage, indicating that all converters share the loading equally between them.

Figure 2.8: V-I loadlines of all power converters and their respective voltage droop. The inset figure shows the loadlines of all power converters in P.U. The loadlines shown here represent the steady state value of the power converter.

The simulation layout in Simulink is shown in Figure 2.9. The simulation was run for 5 seconds and the readings for the output current for all sources, bus voltage, and load current were recorded and are shown in Figure 2.10.

Figure 2.9: Simulation layout in Matlab Simulink.

Figure 2.10: Results from the simulation.

The chronology of the simulation and results are discussed as follows:

- 1) At t = 0, power converter 1 (for energy source 1) and power converter 2 (for energy source 2) are both connected to the load of 70  $\Omega$  resistor and 1  $\mu$ F connected in parallel. Power converter 3 (for energy source 3) and 40 mA constant current sink are not connected in the system. It can be observed from the waveforms that both power converter 1 and power converter 2 deliver an output current simultaneously to the load. It can be determined from the bus voltage (2.16 V) that the loading of the system is less than 50 %. The output current from both converters are consistent with the designed loadlines as shown in Figure 2.8 before.

- 2) At t = 1, power converter 3 is connected, increasing the available power of the system. As a result, the bus voltage rises indicating that the loading of the system is reduced, and both

- output current from power converter 1 and power converter 2 decrease as the load is now shared with power converter 3.

- 3) At t = 2.5, 40 mA constant current sink is connected, increasing the load in the system. All power converters respond to this sudden change in load by increasing their output current, and the bus voltage drops due to the higher loading.

- 4) At t = 4, power converter 2 is disconnected, decreasing the available power in the system. As a result, the load is now shared between power converter 1 and power converter 3. The output current from both of these converters increase to balance out the absence of output current from power converter 2. The bus voltage decreases due to the higher loading in the system. In these simulations, it was observed that the steady state values of the converters agree with the designed loadlines.

This simple simulation shows that the operation of parallel power converters can be easily regulated via the introduction of this voltage droop mechanism. The observations and conclusion drawn from this simulation include:

- 1) Voltage droop enables all connected power converters to simultaneously deliver current, hence power to the load. This means that the system could be used to power up heavy load that could not be powered by a single energy harvester, hence increasing the loading capability of the energy harvesting system.

- 2) The system is capable in reliably responding to the connection and disconnection of any power converters and loads, and provided the generation capacity is higher than the power demand from the load, the system will not collapse. The response time is determined by the time constant of each converter connected to the system. This means that in the actual system, the plug-and-play feature is easily achievable.

- 3) Apart from a pre-set design value, there is no communication between power converters to regulate the sharing mechanism, hence there is no need to establish a communication link for the converters. The bus voltage is used by all converters as the main regulation parameter.

- 4) Load burden is shared equally by all connected power converter in terms of their generation capacity.

- 5) The bus voltage can be used to determine the loading in the system, hence more features such as load shedding can be integrated based on the magnitude of the bus voltage.

In the next section, the implementation of this voltage droop mechanism in actual control circuitry of the power converter is investigated. Furthermore, as energy harvesters possess

time-varying output power, the droop needs to be regularly tuned to match this variation and the solution for this issue will be presented.

# 2.3 Droop Demonstration

In this section, the implementation of voltage droop mechanism in presented. Although the general concept has been outlined in the previous section, the implementation aspect in actual circuits has neither been presented nor discussed yet. Moreover, the droop magnitude presented in the previous section is fixed and static, however since the amount of output power from the energy harvester will vary over time, the magnitude of the droop needs to be able to follow this variation. The method to achieve this droop variation with rated power for the energy harvester proposed here has not been reported elsewhere and is the main contribution from this chapter. This section investigates the implementation and presents the results of this variable droop mechanism in the feedback circuitry of a power converter.

### 2.3.1 I-V Characterisation for Harvesters

The first step to demonstrate the droop mechanism is to investigate the characteristics and performance of energy harvesters/transducers that will be used in the system. In this aspect, two types of harvester are proposed; solar panel and thermoelectric generator (TEG). Each of these harvesters was put under controlled environment conditions and the magnitude of harvested power that will be fed to the system is determined.

#### a. Solar Panel

The characteristics and equivalent circuit models of solar panel have been proposed, presented, and discussed in great details in the literature. Under any illumination, a typical solar panel possesses a standard and recognisable shape of current voltage (I-V) and power voltage (P-V) characteristics. Additionally, since solar panel possesses parasitic series and shunt resistance, there is a point in the P-V curve where the solar panel outputs the maximum available power to the load. This point is commonly known as maximum power point (MPP). This point typically occurs when the output voltage of the solar panel is at 80 % of its open circuit voltage ( $V_{OC}$ ). Most power converters are equipped with MPP tracking (MPPT) functionality designed to adjust the input impedance to ensure that the solar panel is always operating in the region around this MPP voltage ( $V_{MPP}$ ).

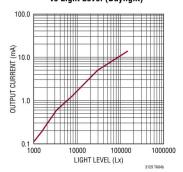

The solar panel used in this thesis is an amorphous silicon (a-Si) AM-7E04CAR manufactured by Sanyo as shown in Figure 2.11 (a). In order to obtain the I-V characteristic of this panel, it

was put under four different illuminations as described in Table 2.1 and the I-V curve was extracted for each illumination by drawing a set current from the panel by using Keithley Sourcemeter 2604B as shown in Figure 2.11 (b). Figure 2.11 (c) shows the extracted I-V and calculated P-V curves of the solar panel under these different illuminations. Figure 2.11 (d) presents the plot of output voltage of the panel when the MPP occurs  $(V_{MPP})$  against open circuit voltage  $(V_{OC})$ . All the relevant results are tabulated in Table 2.2.

IlluminationLEDLux (lx)Illumination 1White (cool white)500Illumination 2Yellow (warm white)600Illumination 3Both white and yellow1100Illumination 4Typical fluorescent indoor light120

Table 2.1: Illumination level

Figure 2.11: Experimental setup and characterisation results from the solar panel.

From the I-V curve, it can be observed that the short circuit current ( $I_{SC}$ ),  $V_{OC}$ , and extracted MPP vary strongly with illumination. The highest MPP of 100 mW was extracted when the solar panel was illuminated through a combination of warm and cool LEDs. Under a typical indoor fluorescent light illumination, 2 mW of MPP was able to be extracted. Finally, from the  $V_{MPP}/V_{OC}$  ratio, it can be observed that the MPP occurs at approximately 80 % of  $V_{OC}$ , which agrees with the expected behaviour of any typical solar panel.

Voc (V) Illumination Isc (mA)  $\mathbf{V}_{\mathbf{MPP}}\left(\mathbf{V}\right)$ MPP (mW) 4 8.62 0.35 6.8 2.04 3 11.30 9.2 99.09 12.62 2 10.72 6.55 8.8 49.72 10.63 5.93 8.4 1 46.62

Table 2.2: Parameters for the solar panel for all illuminations

### b. Thermoelectric Generator (TEG)

The TEG is able to convert the difference in temperature,  $\Delta T$  between its two exposed surfaces to a useful electrical voltage (Seebeck effect), which can be used to power up an external low power load. Generally, its equivalent circuit is simply a voltage source in series with an internal resistance. The magnitude of the output voltage varies linearly with the temperature difference. When the current flows through the TEG (when connected to the load), a reversible effect known as the Peltier effect can be observed; the applied voltage across the TEG created the temperature difference between its two surfaces. This causes the temperature of the hot side surface of the TEG to drop and vice versa, reducing the output voltage from the Seebeck effect and hence the output power of the TEG. Due to this unavoidable phenomenon, it is extremely important to maintain  $\Delta T$  between the two exposed surfaces in TEG to ensure a stable output power.

The TEG used in this thesis is Seebeck Effect Module GM250-241-10-12 manufactured by European Thermodynamics. Since the TEG possesses a very low output voltage, two similar TEGs exposed to the same temperature on each side are connected in series to boost the total output voltage. Insulating foam was placed in between the hot side and cold side. The surface of the hot side is directly exposed but heatsinks (PGA, 9.8 K/W, 36 x 36 x 12.3 mm) were attached to the surface of the cold side using a thermal interface (polyamide, 0.37 W/mK 0.127 mm) to provide a better heat dissipation. The constructed TEGs system is shown in Figure 2.12 (a). The small inset picture in the same figure shows the TEG module used in the system.

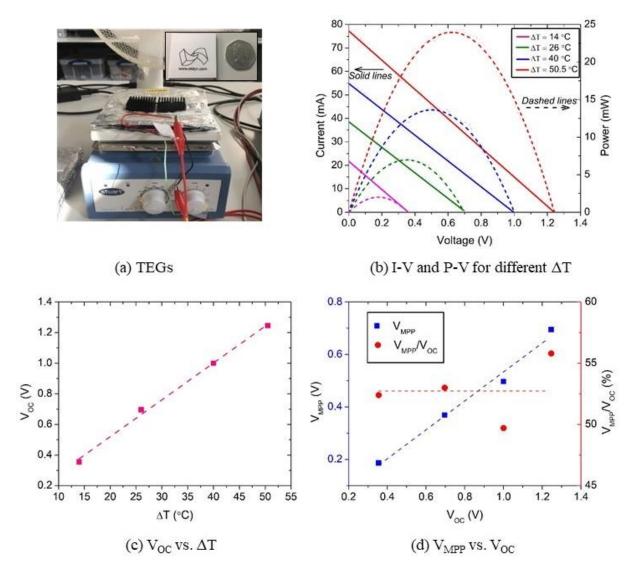

Figure 2.12: Pictures showing the TEG harvester and experiment setup together with the characterisation results.

To extract the I-V characteristics under a different  $\Delta T$ , a setup with a hotplate (Stuart UC152) and a digital thermometer (Omega HH501BJK) with a K type thermocouple were used. The hot side was placed directly on a hotplate and the heatsinks on the cold side were exposed to air with a fan facing towards it to assist the heat dissipation process. The hotplate temperature was controlled to heat up the hot side of the TEGs. In order to accurately monitor the surface temperature, K type thermocouples were placed on both sides. The temperature of the hotplate was varied and the  $\Delta T$  and respective I-V characteristic were extracted by sinking the current to Keithley Sourcemeter 2604B. The setup was left for 30 minutes between each measurement to ensure that the temperature was stabilised for both sides. The experimental setup is shown in Figure 2.12 (a). Figure 2.12 (b) shows the extracted I-V characteristics for multiple  $\Delta T$ . At  $\Delta T = 50.5$  °C, a maximum power of 24.5 mW was extracted from the TEGs. At  $\Delta T = 14$  °C

which is the typical  $\Delta T$  expected when the hot side is equal to the body temperature ( $\approx 36$  °C) and the cold side is equal to the room temperature ( $\approx 22$  °C), maximum power of approximately 2 mW was extracted. It can be observed that the I-V curves have a strong dependency on  $\Delta T$ . Figure 2.12 (c) shows this dependency by plotting  $V_{OC}$  against  $\Delta T$ . This plot reveals a strong agreement with the expected linear characteristics between these two parameters. Since TEG has a parasitic series resistance, similar to a solar panel, there will be a point where MPP will occur. Figure 2.12 (d) shows the plot of V<sub>MPP</sub> vs. V<sub>OC</sub> for the TEGs used in this thesis. From this, it can be concluded that the V<sub>MPP</sub> occurs at approximately 50 % of V<sub>OC</sub>. These findings agree with the typical characteristic of TEG as reported in the literature. All results are tabulated in Table 2.3.

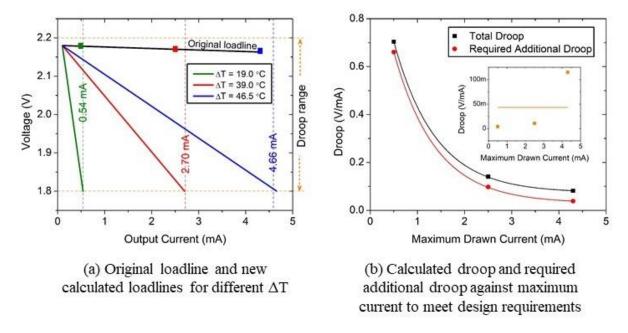

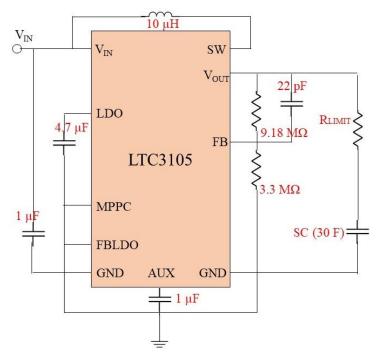

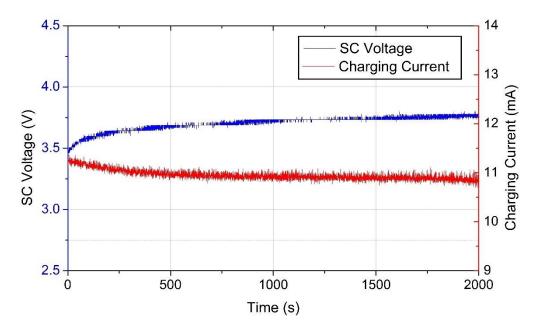

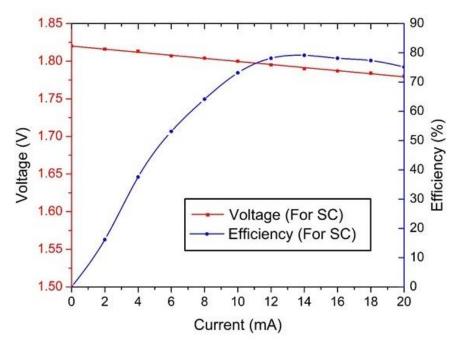

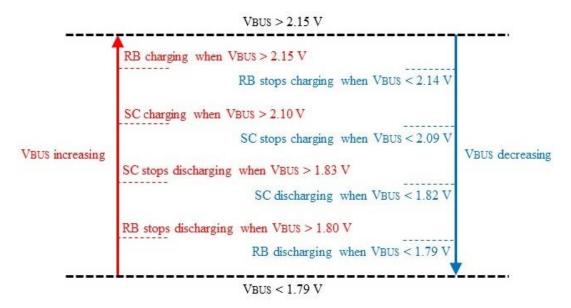

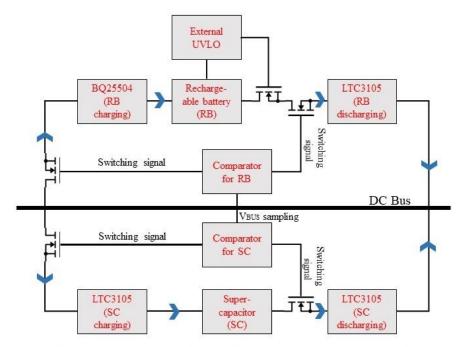

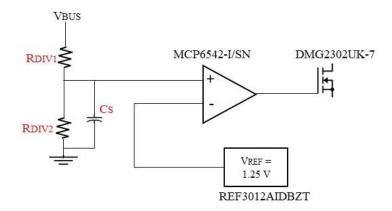

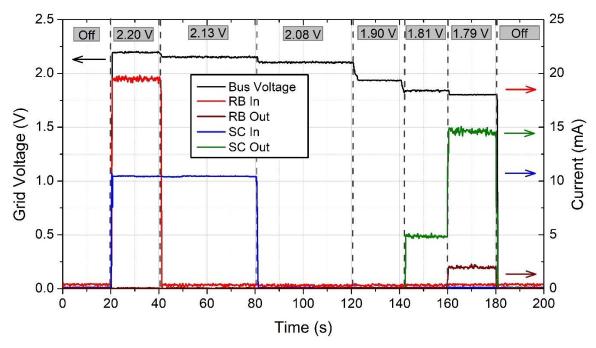

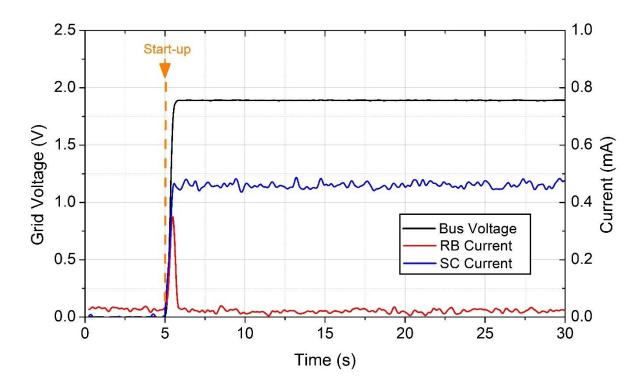

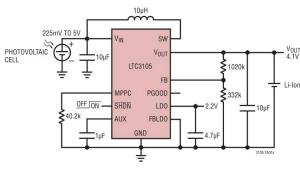

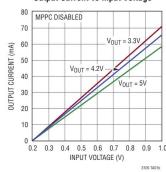

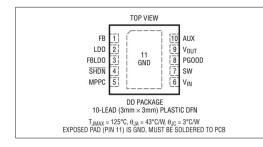

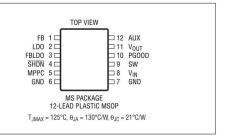

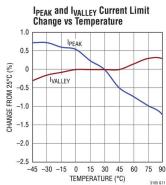

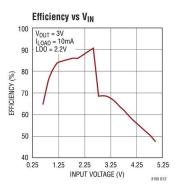

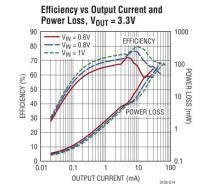

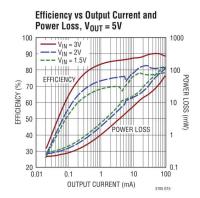

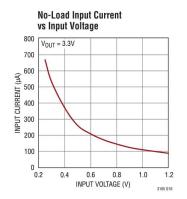

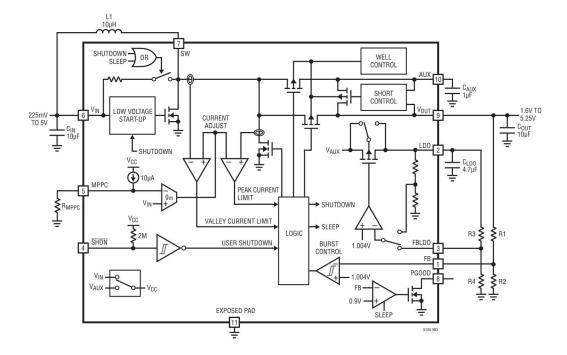

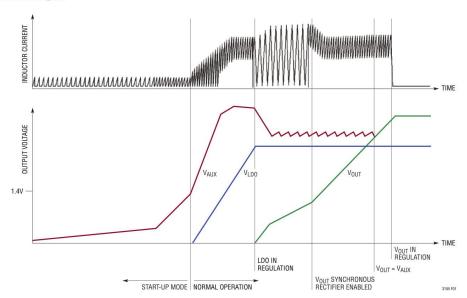

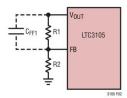

Table 2.3: Extracted parameters for the TEGs under different temperature differences,  $\Delta T$ .