# Software lock elision for x86 machine code

# Amitabha Roy

University of Cambridge Computer Laboratory Emmanuel College

April 2011

This dissertation is submitted for the degree of Doctor of Philosophy

## **Declaration**

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except where specifically indicated in the text.

This dissertation does not exceed the regulation length of  $60\,000$  words, including tables and footnotes.

### Software lock elision for x86 machine code

### Amitabha Roy

### **Summary**

More than a decade after becoming a topic of intense research there is no transactional memory hardware nor any examples of software transactional memory use outside the research community. Using software transactional memory in large pieces of software needs copious source code annotations and often means that standard compilers and debuggers can no longer be used. At the same time, overheads associated with software transactional memory fail to motivate programmers to expend the needed effort to use software transactional memory. The only way around the overheads in the case of general unmanaged code is the anticipated availability of hardware support. On the other hand, architects are unwilling to devote power and area budgets in mainstream microprocessors to hardware transactional memory, pointing to transactional memory being a "niche" programming construct. A deadlock has thus ensued that is blocking transactional memory use and experimentation in the mainstream.

This dissertation covers the design and construction of a software transactional memory runtime system called SLE\_x86 that can potentially break this deadlock by decoupling transactional memory from programs using it. Unlike most other STM designs, the core design principle is *transparency* rather than *performance*. SLE\_x86 operates at the level of x86 machine code, thereby becoming immediately applicable to binaries for the popular x86 architecture. The only requirement is that the binary synchronise using known locking constructs or calls such as those in Pthreads or OpenMP libraries. SLE\_x86 provides speculative lock elision (SLE) entirely in software, executing critical sections in the binary using transactional memory. Optionally, the critical sections can also be executed without using transactions by acquiring the protecting lock.

The dissertation makes a careful analysis of the impact on performance due to the demands of the x86 memory consistency model and the need to transparently instrument x86 machine code. It shows that both of these problems can be overcome to reach a reasonable level of performance, where *transparent* software transactional memory can perform better than a lock. SLE\_x86 can ensure that programs are ready for transactional memory in any form, without being explicitly written for it.

### Acknowledgements

I gratefully acknowledge my supervisor Steven Hand and adviser Tim Harris for all the advice, discussion and feedback they have provided throughout my time at Cambridge. In particular, I am thankful for all the drafts they have read through patiently. Their support has helped me gain considerable expertise and confidence. This thesis has also benefited from feedback by Robert Mullins and Ian Watson. I am also grateful to the Cambridge and Nehru trusts, the Overseas Research Scholarship, the Freshwater Fund and the Lundgren Research Award for funding my studies at Cambridge.

A ton of thanks go out to my family, particularly my mother and father for having believed in me and for putting up with my insistence on exploring the unknown instead of settling down. This PhD simply would not have been possible without the both of you. Thanks also go out to the rest of the "troops" and yes, all the cats!

This thesis is indebted to Mohita, my wife, who I met here at Cambridge. I plead guilty to spending, perhaps, too much time "solving things in my head" as you have so rightly observed. I promise to henceforth spend much more time with you. Indeed, Cambridge would have a been an awfully lonely place without you by my side. Thanks also go out to your family for having welcomed me into their fold.

Finally I'd like to acknowledge my friends for the Mexican van (Derek, Eiko, Anil, Theo, Malte and Chris), for all the squash (Nishant), the action movies (Pradipta), the table football (Anastasios, Fei, Fernando and Periklis) and indeed too many to name here.

Some of the experiments for this thesis were performed on the COSMOS Consortium supercomputer within the DiRAC Facility jointly funded by STFC, the Large Facilities Capital Fund of BIS and the University of Cambridge. I am grateful to them for the use of the SGI Altix UV1000 supercomputer.

# **Contents**

| 1 | Intr | oduction                                     | 17 |

|---|------|----------------------------------------------|----|

|   | 1.1  | Motivation                                   | 17 |

|   | 1.2  | Contributions                                | 20 |

|   | 1.3  | Outline                                      | 20 |

|   | 1.4  | Publications                                 | 21 |

| 2 | Bacl | kground                                      | 23 |

|   | 2.1  | Hardware transactional memory                | 24 |

|   | 2.2  | Software transactional memory                | 27 |

|   |      | 2.2.1 Non-blocking data structures           | 28 |

|   |      | 2.2.2 Non-blocking STMs                      | 28 |

|   |      | 2.2.3 Lock-based STMs                        | 30 |

|   |      | 2.2.4 Word-based and object-based STMs       | 32 |

|   | 2.3  | STM instrumentation                          | 33 |

|   |      | 2.3.1 Library                                | 33 |

|   |      | 2.3.2 Compiler                               | 35 |

|   |      | 2.3.3 Binary rewriting                       | 36 |

|   | 2.4  | Atomicity specifications                     | 36 |

|   |      | 2.4.1 Atomic block                           | 37 |

|   |      | 2.4.2 Lock elision                           | 38 |

|   | 2.5  | Weak vs strong atomicity                     | 41 |

|   | 2.6  | Single lock atomicity and memory consistency | 43 |

|   | 2.7  | Hybrid transactional memory                  | 44 |

|   | 2.8  | Performance benefits of transactional memory | 45 |

|   | 2.9  | Software lock elision for x86 machine code   | 46 |

| 3 | x86-         | safe sof | tware transactional memory               | 49  |

|---|--------------|----------|------------------------------------------|-----|

|   | 3.1          | x86 m    | emory consistency model                  | 49  |

|   | 3.2          | Counte   | erexamples                               | 55  |

|   | 3.3          | A seria  | alising design: STM_x86_strict           | 58  |

|   |              | 3.3.1    | STM primitives                           | 58  |

|   |              | 3.3.2    | Speculation phase                        | 59  |

|   |              | 3.3.3    | Commit phase                             | 61  |

|   |              | 3.3.4    | SLA speculation                          | 63  |

|   | 3.4          | Recove   | ering scalability: STM_x86               | 67  |

|   |              | 3.4.1    | Publication safety                       | 72  |

|   |              | 3.4.2    | Aborts                                   | 73  |

|   | 3.5          | Compa    | arison with language level memory models | 73  |

|   |              | 3.5.1    | Memory update consistency                | 74  |

|   |              | 3.5.2    | Speculation safety                       | 75  |

|   |              | 3.5.3    | Dynamic separation                       | 75  |

|   | 3.6          | Mappi    | ng critical sections to SLA              | 75  |

|   | 3.7          | Mixing   | g locking with transactions              | 78  |

|   | 3.8          | Impler   | nentation                                | 80  |

|   |              | 3.8.1    | Metadata and logging                     | 80  |

|   |              | 3.8.2    | Arbitrary granularity logs               | 80  |

|   |              | 3.8.3    | Lock blacklists                          | 83  |

|   | 3.9          | Evalua   | tion of STM_x86                          | 83  |

|   | 3.10         | Discus   | sion                                     | 87  |

| 4 | <b>x86</b> 1 | machin   | e code instrumentation                   | 89  |

|   | 4.1          | Appro    | ach                                      | 89  |

|   |              | 4.1.1    | Static binary rewriting                  | 89  |

|   |              | 4.1.2    | Dynamic binary rewriting                 | 90  |

|   |              | 4.1.3    | Combining static and dynamic techniques  | 91  |

|   | 12           | w96 in   | estrumentation modes and backends        | 0.1 |

|   | 4.3            | Active mode                              | 3   |

|---|----------------|------------------------------------------|-----|

|   |                | 4.3.1 Identifying critical sections      | 4   |

|   |                | 4.3.2 Basic block discovery              | 5   |

|   |                | 4.3.3 Basic block instrumentation        | 6   |

|   |                | 4.3.4 PIC operations                     | 8   |

|   | 4.4            | Passive mode                             | 9   |

|   |                | 4.4.1 Preparation                        | 9   |

|   |                | 4.4.2 Intercept and dispatch             | 0   |

|   | 4.5            | Exceptions                               | 1   |

|   | 4.6            | Checkpoints                              | 12  |

|   |                | 4.6.1 Registers                          | 12  |

|   |                | 4.6.2 Memory                             | 12  |

|   | 4.7            | SLE_x86 in practise                      | 14  |

|   |                | 4.7.1 Backends                           | 15  |

|   | 4.8            | Evaluation of the instrumentation system | 15  |

|   | 4.9            | Evaluation of SLE_x86                    | 17  |

|   | 4.10           | Discussion                               | 18  |

| _ | <b>~</b> • • • |                                          | 4   |

| 5 | Criti          | ical section characterisation 11         | . 1 |

|   | 5.1            | Disjoint access parallelism              | 2   |

|   | 5.2            | Lock contention                          | 3   |

|   | 5.3            | Profiler operation                       | 5   |

|   | 5.4            | Profiling                                | 6   |

|   | 5.5            | Post processing                          | 7   |

|   | 5.6            | Characterising a Microbenchmark          | 9   |

|   | 5.7            | Characterising STAMP                     | 0   |

|   | 5.8            | Discussion                               | :3  |

| 6  | Thre                                 | ead-private data tags                      | 125 |

|----|--------------------------------------|--------------------------------------------|-----|

|    | 6.1                                  | Generic capabilities                       | 125 |

|    | 6.2                                  | Associating tags with locations            | 128 |

|    | 6.3                                  | Applications                               | 129 |

|    |                                      | 6.3.1 OpenMP thread private data           | 129 |

|    |                                      | 6.3.2 Stack data                           | 130 |

|    | 6.4                                  | Adaptive tagging for STAMP                 | 131 |

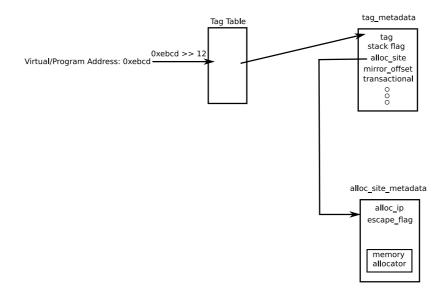

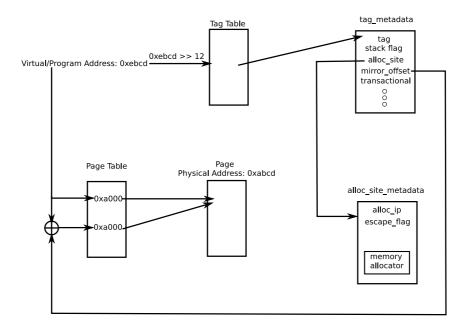

|    |                                      | 6.4.1 Tag metadata and allocation sites    | 133 |

|    |                                      | 6.4.2 The non-transactional access problem | 134 |

|    |                                      | 6.4.3 Reducing undo-logging overheads      | 136 |

|    |                                      | 6.4.4 Inlining checks                      | 137 |

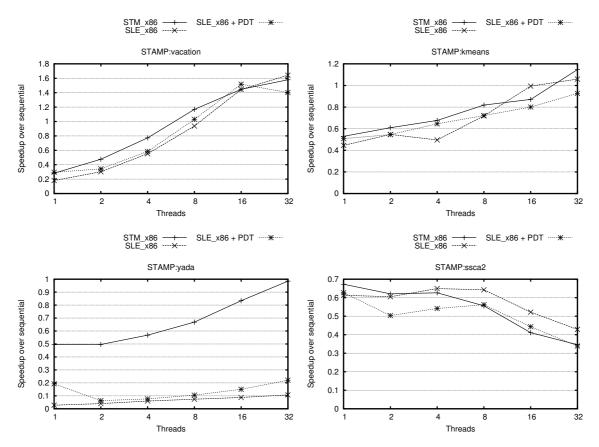

|    | 6.5                                  | Evaluation                                 | 137 |

|    | 6.6                                  | Discussion                                 | 142 |

| 7  | App                                  | licability                                 | 145 |

|    | 7.1                                  | Scalability                                | 146 |

|    | 7.2                                  | Impact on software development             | 148 |

|    | 7.3                                  | Condition variables and fine-grained locks | 151 |

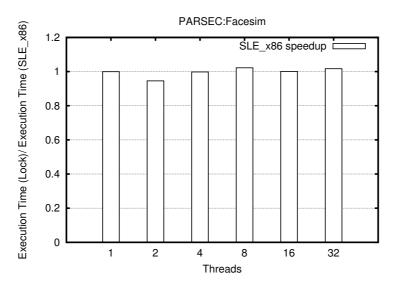

|    |                                      | 7.3.1 Facesim                              | 153 |

|    |                                      | 7.3.2 Fluidanimate                         | 153 |

|    | 7.4                                  | Discussion                                 | 156 |

| 8  | Con                                  | clusion                                    | 157 |

|    | 8.1                                  | Summary                                    | 157 |

|    | 8.2                                  | Future research                            | 159 |

| Αŗ | pend                                 | lix A: SLE_x86 restrictions                | 160 |

| Ar | ppendix B: Experiment configurations |                                            |     |

# **List of Figures**

| 2.1  | Sorted linked list using Herhily et al's HTM instructions | 25 |

|------|-----------------------------------------------------------|----|

| 2.2  | Sorted linked list using Hammond et al's TCC              | 26 |

| 2.3  | Linked list using the TL2 library                         | 34 |

| 2.4  | Sorted linked list using atomic blocks                    | 37 |

| 2.5  | A barrier for two threads                                 | 38 |

| 2.6  | Privatisation                                             | 42 |

| 2.7  | Publication                                               | 43 |

| 2.8  | Memory ordering differences                               | 44 |

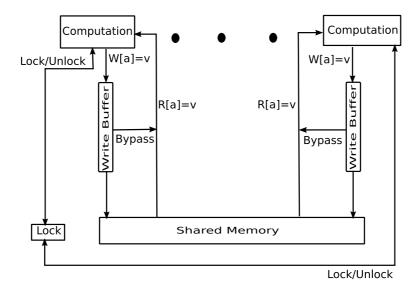

| 3.1  | TSO machine                                               | 50 |

| 3.2  | Loads must be ordered after earlier transactions          | 55 |

| 3.3  | Stores must be ordered across atomic blocks               | 57 |

| 3.4  | mfence in a transaction                                   | 63 |

| 3.5  | Visibility of writes from a transaction                   | 64 |

| 3.6  | Privatisation                                             | 68 |

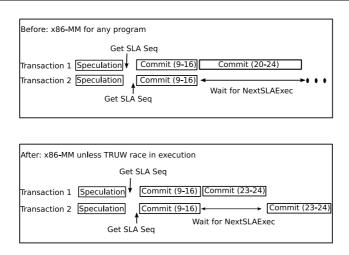

| 3.7  | Optimisation trades generality for scalability            | 72 |

| 3.8  | Publication                                               | 73 |

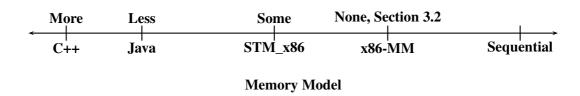

| 3.9  | Memory consistency model vs weak atomicity                | 74 |

| 3.10 | Memory consistency implications for an STM                | 74 |

| 3.11 | Symmetric dependent visibility                            | 76 |

| 3.12 | Buggy signalling                                          | 77 |

| 3.13 | Type of asymmetric data race                              | 78 |

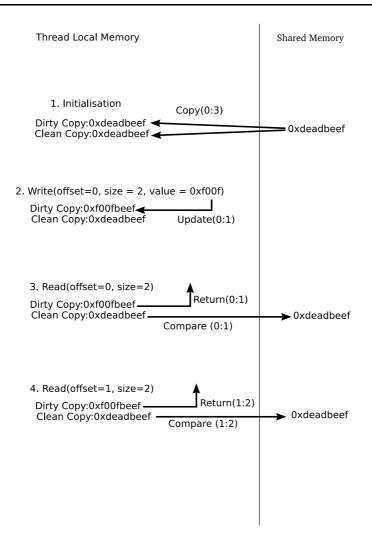

| 3.14 | Bypassing writes to reads                                 | 81 |

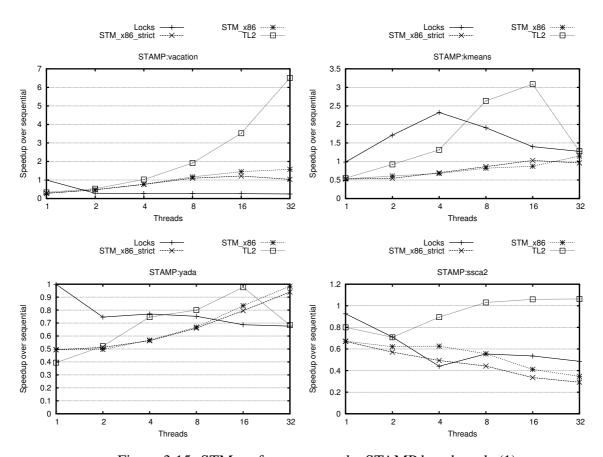

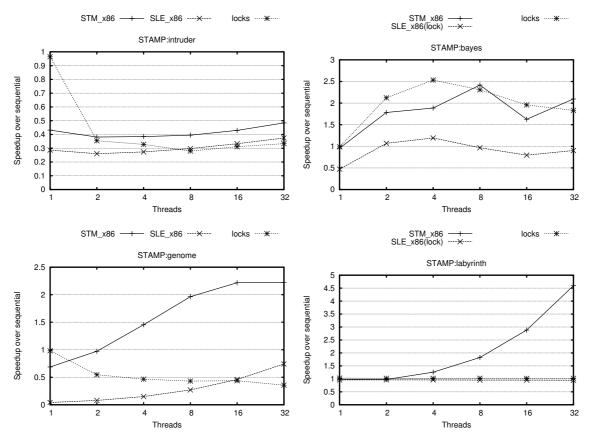

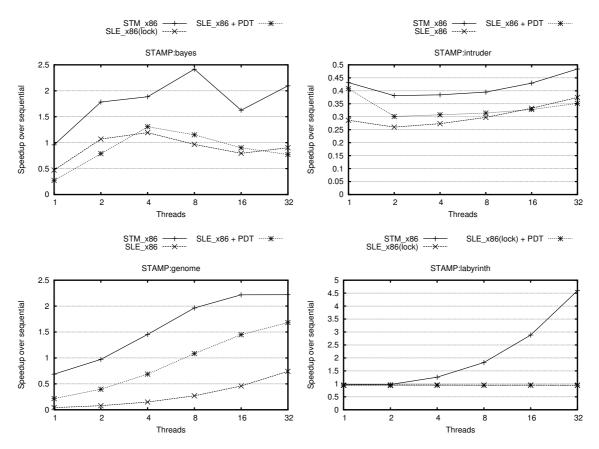

| 3.15 | STM performance on the STAMP benchmarks(1)                                             | 84  |

|------|----------------------------------------------------------------------------------------|-----|

| 3.16 | STM performance on the STAMP benchmarks(2)                                             | 85  |

| 3.17 | TL2: Maximum variation in execution time as a fraction of the median                   | 86  |

| 3.18 | Is using STM_x86 better than using the lock? ('*' means also better than sequential)   | 86  |

| 4.1  | Possibly nested locking                                                                | 90  |

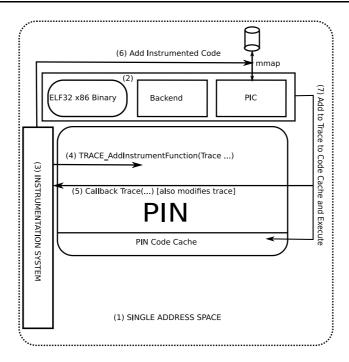

| 4.2  | Execution in active mode                                                               | 93  |

| 4.3  | The same function in multiple contexts                                                 | 94  |

| 4.4  | Shared memory instrumentation for a basic block                                        | 97  |

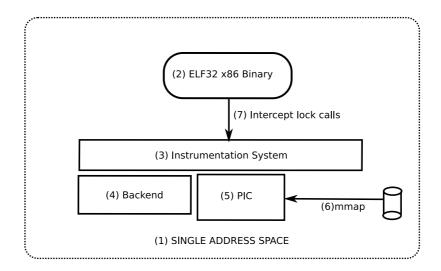

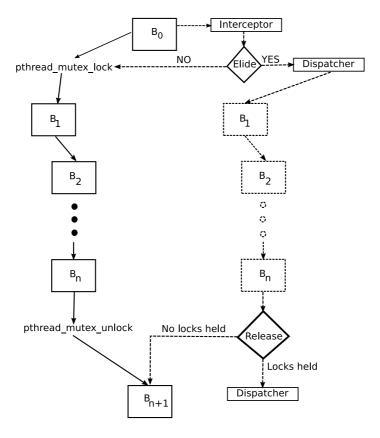

| 4.5  | Execution in passive mode                                                              | 99  |

| 4.6  | Intercept and dispatch                                                                 | 101 |

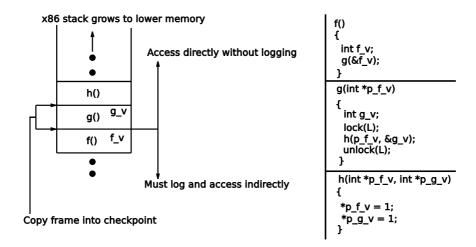

| 4.7  | Checkpointing the stack                                                                | 103 |

| 4.8  | Putting it together: Using SLE                                                         | 104 |

| 4.9  | STAMP: Static characteristics                                                          | 106 |

| 4.10 | Basic blocks added to PIC in each active execution iteration                           | 106 |

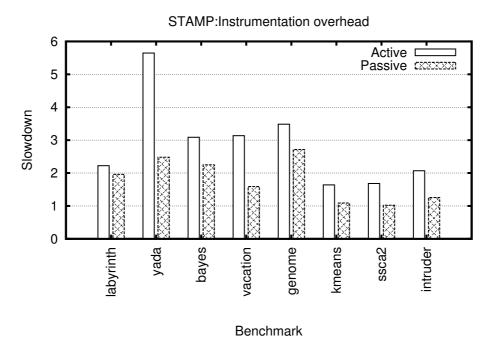

| 4.11 | Binary instrumentation overhead                                                        | 107 |

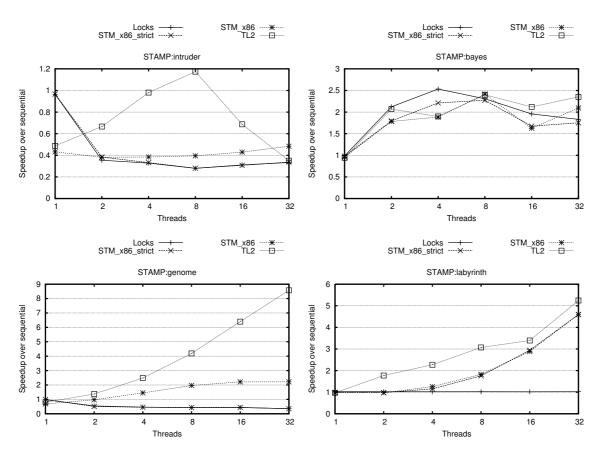

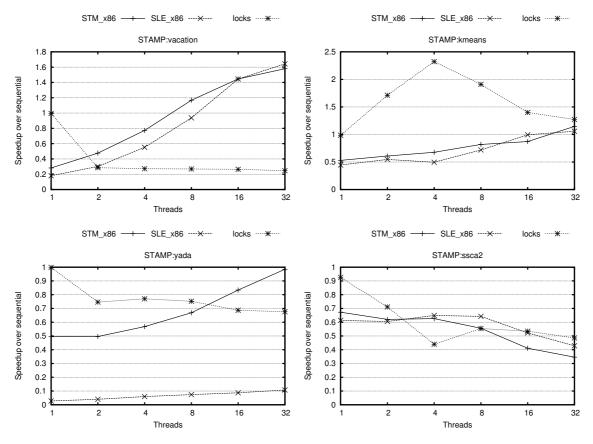

| 4.12 | SLE on the STAMP benchmarks(1)                                                         | 108 |

| 4.13 | SLE on the STAMP benchmarks(2)                                                         | 109 |

| 4.14 | Is using SLE_x86 better than using the lock? ('*' means also better than sequential) 1 | 109 |

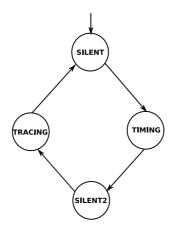

| 5.1  | Profiler phases                                                                        | 116 |

| 5.2  | Example profiling output                                                               | 117 |

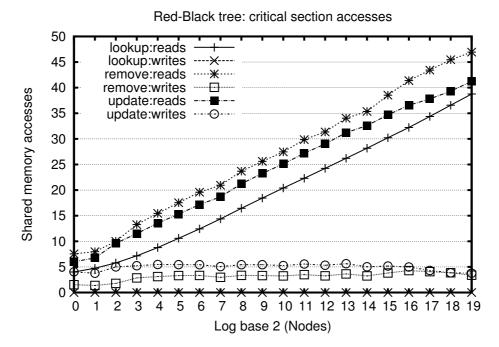

| 5.3  | Red-Black tree memory access characterisation                                          | 120 |

| 5.4  | STAMP critical section memory operations                                               | 121 |

| 5.5  | A fragment of code from the labyrinth benchmark                                        | 122 |

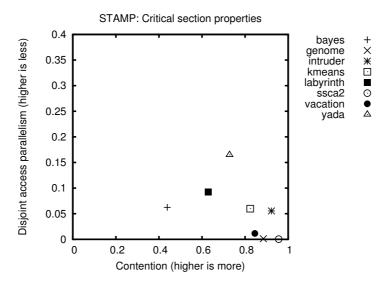

| 5.6  | STAMP critical section characteristics                                                 | 123 |

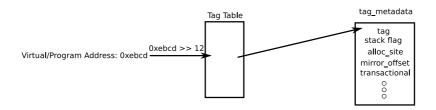

| 6.1  | Association of tag metadata with pages                                                 | 129 |

| 6.2  | Example of OpenMP ThreadPrivate from Quake                                             | 129 |

| 6.3  | Sharing stack locations in the Bodytrack benchmark from PARSEC                         | 132 |

| 6.4  | A fragment of code from the Genome benchmark                                           | 133 |

| 6.5  | Extended tag metadata for adaptivity                                                   | 134 |

| 6.6  | Extended tag metadata with mirror mappings                                                                       | 136 |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 6.7  | Inlined tag check                                                                                                | 137 |

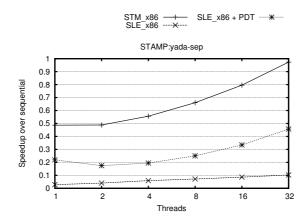

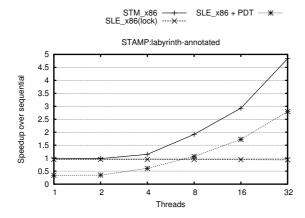

| 6.8  | SLE (with private data tagging) on the STAMP benchmarks(1)                                                       | 138 |

| 6.9  | SLE (with private data tagging) on the STAMP benchmarks(2)                                                       | 139 |

| 6.10 | Yada data structure: original (top) and separated (bottom)                                                       | 140 |

| 6.11 | Performance of Yada after data structure decomposition                                                           | 141 |

| 6.12 | Labyrinth source fragment: original (top) and annotated(bottom)                                                  | 141 |

| 6.13 | Performance of Labyrinth with annotation                                                                         | 142 |

| 6.14 | Is using Best Of(SLE_x86, SLE_x86 with PDT) better than using the lock?  ('*' means also better than sequential) | 142 |

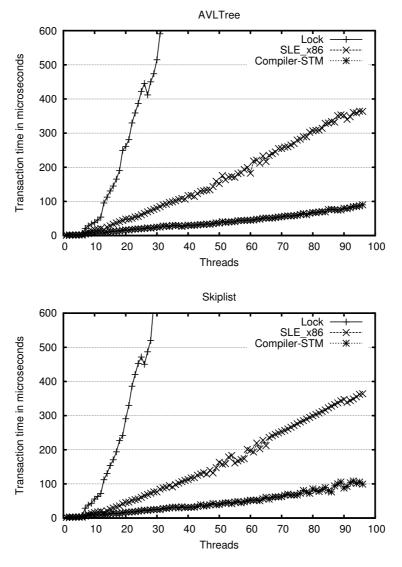

| 7.1  | Microbenchmark profiles(8 threads)                                                                               | 147 |

| 7.2  | Scaling on a Corei7 NUMA system                                                                                  | 147 |

| 7.3  | Scalability at CPU socket intervals                                                                              | 148 |

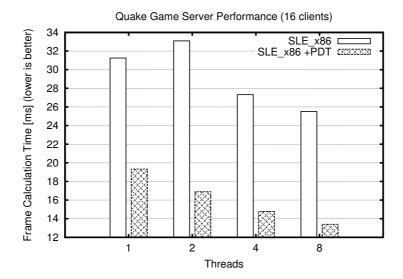

| 7.4  | Quake using SLE                                                                                                  | 149 |

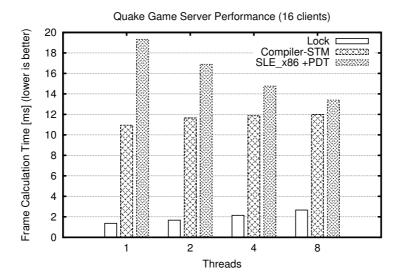

| 7.5  | Quake using different implementations of critical sections                                                       | 150 |

| 7.6  | Quake profile                                                                                                    | 150 |

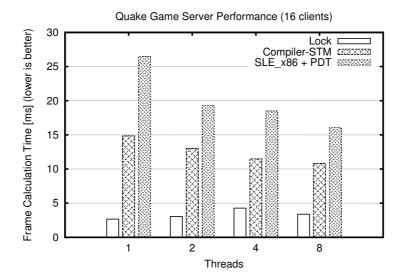

| 7.7  | Quake using different implementations of critical sections (older Xeon system)                                   | 151 |

| 7.8  | PARSEC critical section memory operations                                                                        | 154 |

| 7.9  | Using SLE on Facesim                                                                                             | 155 |

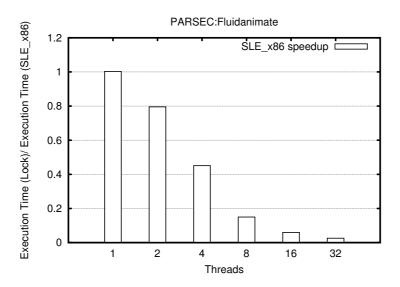

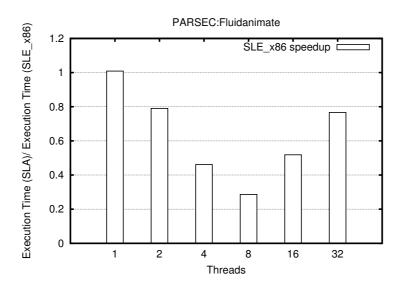

| 7.10 | Using SLE on Fluidanimate                                                                                        | 155 |

| 7.11 | Using SLE on Fluidanimate with Single Lock Atomicity                                                             | 156 |

# **Chapter 1**

# Introduction

This dissertation describes the design, construction and evaluation of a system that applies software transactional memory (STM) to an x86 binary synchronising with locks. The system aims to improve scalability when coarse-grained locks are a bottleneck in the program while guaranteeing that the result of execution of the program is indistinguishable from that were locks to be used.

In this chapter I outline the motivation for this work. I also summarise the contributions of the dissertation and list the contents of the following chapters that describe the contributions in detail.

## 1.1 Motivation

Locks are the most popular method of synchronisation in multithreaded programs. With increasing thread counts in systems due to the availability of multicores, coarse-grained locks can become a scalability bottleneck in programs. This has led to a tension between coarse-grained and fine-grained locking in programs. Coarse-grained locking is easier to get right since fine-grained locking is (a) prone to programming errors such as deadlock and (b) makes composable software engineering hard since calls that cross multiple modules need to be aware of held locks in order to avoid deadlock. On the other hand fine grained locks provide better scalability since critical sections do not need to wait on the same lock if they need to access different shared memory locations.

A simple example serves to illustrate the problem of locking granularity. Consider the problem of implementing a concurrent red-black tree. A straightforward solution would be to start from a sequential implementation of red-black trees available in a standard textbook [CLRS01] and protect the tree with a single coarse grained lock. A more scalable solution is to use the considerably more complicated relaxed version of red-black trees [HOSS97] that relaxes the

data structure by decoupling insertion and deletion from re-balancing. One could then refer to Fraser's dissertation [Fra03] that includes a fairly non-trivial fine grained locking protocol for relaxed red-black trees.

The parallel programming research community has been investigating transactional memory [HM93] as the solution to this problem. Hardware transactional memory provides special hardware support for executing blocks of code transactionally. Software transactional memory implements transactional memory entirely in software making the benefits of transactions available to programs running on current microprocessors without the need to wait for hardware transactional memory to become available. When using transactional memory, rather than explicitly waiting for and acquiring any coarse-grained locks, execution proceeds speculatively and uses a two phase commit protocol similar to database style transactions. Transactions thus only need to wait for each other when there are conflicting accesses to the same piece of shared data. In the example, two updates to a red-black tree can proceed in parallel, if they modify different subtrees. This is usually the case for large enough trees and thus optimistic concurrency control can provide the scalability of fine grained locking without the associated complexity (a fact that Fraser also demonstrated [Fra03]). However, in spite of almost a decade of research into transactional memory there is no transactional memory hardware nor any examples outside the research community of the use of software transactional memory.

Using software transactional memory is too disruptive to software engineering for large pieces of software. The stumbling block to adoption is a clean integration of transactional memory into the software stack. Integrating transactional memory into a language requires defining the semantics of a construct that can expose transactional memory to the programmer (such as an *atomic block* [HF03]) and ensuring that the software transactional memory implementation preserves those semantics *and* the language memory model (which in the case of many widely used languages is only just being defined). Further, an STM requires either tedious and error-prone instrumentation of source to use an STM library or equally tedious annotation of source to use experimental STM compilers that are yet to agree on language extensions. Finally precompiled library calls and system calls (and I/O in general) are difficult to use in transactions unless one is prepared to sacrifice scalability by serialising transaction execution in order to execute *irrevocably* [WSAT08]. At the same time, overheads associated with software transactional memory fail to motivate programmers to expend the needed effort to use software transactional memory. The only way around the overheads in the case of general unmanaged code is the anticipated availability of hardware support.

On the other hand, architects are unwilling to devote power and area budgets in mainstream microprocessors and deal with the complexity of hardware transactional memory implementation. They point to transactional memory being a "niche" programming construct. Further, the limitations of hardware means that a hybrid solution where some transactions can be executed in software is necessary. Unfortunately, the lack of mainstream acceptance of software transac-

tional memory means that even if hardware transactional memory were to become available it would be some time before programs could be modified to take advantage of it.

A deadlock has thus ensued that is blocking transactional memory use and experimentation in the mainstream. These problems have prompted some researchers to label software transactional memory a research toy [CBM<sup>+</sup>08] and raise serious questions about the future of transactional memory in general.

The crux of the problem with integrating transactional memory into language level synchronisation is that it is contrary to the systems design principle of "separating mechanism from policy". Transactional memory is a mechanism for synchronisation with optimistic concurrency control and is not a sound and easy way to *specify* (or think about) synchronisation. Hence this dissertation proposes leaving the well known and ubiquitous lock as the means for specifying synchronisation in programs. A coarse grained lock can (and should) be used for easy and maintainable synchronisation.

This leaves the question of when to apply the mechanism of "transactional memory". This thesis proposes applying it as late as possible: to machine code at runtime and making it an *optional* mechanism of execution. Software transactional memory is used to elide¹ lock acquisition and speculatively execute the critical section as a transaction. Applying it late means that the software development environment stays unchanged. It also means that the mechanism is language and compiler neutral (and requires no changes to either). Legacy code (including libraries) is no longer a problem. Keeping it optional means that the program can be simply executed with locks for debugging as usual. Locking can also be selectively used for critical sections that do operations that are difficult to reconcile with transactional memory such as system calls, *without* requiring other unrelated transactions to stop running as with current proposals for irrevocability in STMs.

These benefits are attractive enough for various other researchers to design and implement lock elision systems. Other proposals for lock elision so far either involve unavailable hardware [RG01]; are limited to Java [ZWAT<sup>+</sup>08]; or require the programmer to convert code to use a new synchronisation primitive together with a special compiler [USB09].

This dissertation presents the design and implementation of a software lock elision system (SLE\_x86) that uses as a starting point an x86 binary synchronising with locks. Although the implementation I describe is x86 specific the general approach could be replicated for other architectures. It provides a clean separation of mechanism from policy while being usable on current off-the-shelf hardware. Additionally I show how the infrastructure built for SLE\_x86 can be used to build a runtime profiler for x86 binaries. This provides statistics about critical sections in the binary and insights into their possible interaction with transactional memory; particularly to explain the benefit or lack thereof that can be obtained through the use of software lock elision.

<sup>&</sup>lt;sup>1</sup>Elision n.: A deliberate act of omission.

The driving design principle for SLE\_x86 is *applicability* and *transparency*. It is a widely and easily applicable software transactional memory runtime system, since it requires *nothing* from the programmer in terms of awareness of transactional memory. It makes software transactional memory backward-compatible with existing code. Unlike other STM designs, performance is only a secondary design goal for SLE\_x86 and the design sacrifices performance when needed for transparency.

### 1.2 Contributions

It is my thesis that software transactional memory can be automatically, transparently and correctly applied at runtime to critical sections in binaries that synchronise with locks and are not constructed to have any awareness of software transactional memory.

The first key contribution of this dissertation is the design and construction of a software transactional memory that preserves the x86 memory consistency model. I start by showing that it is *impossible* for a non-trivial STM to preserve the x86 memory consistency model for all programs. I then show that it is possible to recover scalability by excluding programs that contain a certain type of data race. I argue that such races likely correspond to program bugs and there exist practical techniques to detect such races.

The second key contribution of this dissertation is a lightweight low-overhead mechanism to instrument critical sections in lock-based x86 programs. My instrumentation infrastructure is built with two key design goals in mind. The first is that the cost of inserting instrumentation should be zero. The second is that the execution overhead outside critical sections should be zero. These ensure that software lock elision is "pay to use" in terms of overhead. The instrumentation infrastructure also incorporates a number of novel methods to safely filter out thread-private accesses to further reduce overhead.

## 1.3 Outline

I now outline the organisation of the rest of this dissertation.

In Chapter 2 I survey background literature and place the ideas of this dissertation in proper context. I also delineate my contributions in this dissertation with reference to previous work in lock elision and profilers that attempt to to quantify program suitability for the use of optimistic concurrency control.

In Chapter 3 I consider the requirements for building an STM runtime that can be used to elide locks and execute critical sections concurrently. Preserving the semantics of x86 machine code requires considering the behaviour of the program in terms of the memory model of the

underlying hardware. The STM runtime should thus strive to preserve the memory model even while applying optimistic concurrency control to critical sections. There have been no previous STM designs that have considered a hardware memory consistency model and the focus of the chapter is on designing an STM algorithm that preserves the x86 memory consistency model. I also include an evaluation of the STM against designs that are *more* scalable but only support weaker *language level* memory consistency models.

In Chapter 4, I present a lightweight and low overhead technique to instrument shared memory accesses within critical sections of x86 programs. My technique builds on an existing stable binary rewriting engine but removes associated overheads. The chapter also includes an evaluation of the instrumentation system on its own (in terms of overhead over manual instrumentation) and an evaluation of a complete system for software lock elision in combination with the STM design of the previous chapter.

In Chapter 5 I present the design and construction of a profiler that makes use of this instrumentation to profile the suitability of an x86 binary for using transactional memory. I identify the two key metrics that need to be measured (lock contention and critical section disjoint access parallelism) and show how they can be measured with minimum error from executions of the binary. This profiler is extremely useful to debug the performance of SLE and, being TM agnostic, is useful to characterise the suitability of x86 binaries for TM in general.

In Chapter 6 I tackle one of the key problems with the SLE system built and evaluated in the previous chapters: instrumentation of thread-private data leads to significant overheads for some benchmarks over an STM applied through manual instrumentation. I present a technique for automatically distinguishing thread-private data and safely eliminating STM related overheads for them.

In Chapter 7 I evaluate software lock elision in a more general setting. In previous chapters, I focus on a single comprehensive benchmark (the STAMP benchmark suite) geared towards exercising speculation. In this chapter I compare with compilers that support STM at a language level, on systems architected at a hardware level for scalability and finally on the more real world benchmark of the Quake game server.

In chapter 8, I conclude and provide some suggestions for further areas of research.

## 1.4 Publications

Some of the research described in this dissertation also appears in the following publications:

1. Amitabha Roy, Steven Hand and Tim Harris. Hybrid binary rewriting for memory access instrumentation. In *Proceedings of the Conference on Virtual Execution Environments*, 2011.

#### 1. Introduction

- 2. Amitabha Roy, Steven Hand and Tim Harris. Poster: Weak atomicity under the x86 memory consistency model. In *Proceedings of the Symposium on Principles and Practice of Parallel Programming*, 2011.

- 3. Amitabha Roy, Steven Hand and Tim Harris. Exploring the Limits of Disjoint Access Parallelism. In *Proceedings of the USENIX Workshop on Hot Topics in Parallelism*, 2009.

- 4. Amitabha Roy, Steven Hand and Tim Harris. A runtime system for software lock elision. In *Proceedings of the European Conference on Computer Systems*, 2009.

Of these, the last mentioned publication described a system with the exact *opposite* design goals to the one in this dissertation. It covered the design of a software lock elision system that emphasised performance over transparency, requiring the programmer to manually annotate source code and only supporting the weaker C++ memory model.

# Chapter 2

# **Background**

Transactional memory for general purpose software was inspired by database transactions and aims to bring the benefits of optimistic concurrency control to synchronisation problems in multithreaded code. Starting with the earliest proposals [HM93, ST95], the fundamental idea behind transactional memory has been to not wait for access to data, on the premise that critical sections will not, in the common case, make conflicting accesses.

The advantages of this kind of synchronisation can be illustrated by data structures that have potential for disjoint access parallelism, such as red-black trees that have historically been an important benchmark for the transactional memory community. If one were to consider a large tree and threads making simultaneous lookup, update and delete operations, it is highly likely that a read access will not conflict with a write access since the updates would be confined to a subtree not accessed by a reader. The data structure and its access patterns thus exhibit disjoint-access-parallelism [IR94] i.e. parallelism emanates from the fact that concurrent accesses are likely made to disjoint sets of locations.

Given this scenario, protecting the entire tree with a lock is likely too conservative. However, omitting the lock would be wrong as there is no guarantee that accesses to the tree from simultaneously executing critical sections are always disjoint. It is possible (but hopefully uncommon) that they will conflict. Transactional memory provides an ideal synchronisation mechanism for such a scenario. Entire computations and shared memory accesses representing one of the possible operations on the tree are encapsulated in a "transaction" and presented to the transactional memory system. The transaction is then executed using optimistic concurrency control. All transactions proceed in parallel. If no conflict is detected the transactions can complete simultaneously. On the other hand if a conflict is detected the transactional memory system has the capability to roll back the transaction that has encountered a conflict and restart it. The effect of such a system on the concurrent accesses to the red-black tree – when the tree is used to implement the set abstract data type – is to present a linearised schedule to the programmer [HW90]. A linearised schedule is a total order on the access operations, consistent with the

behaviour of a set, that also respects the constraint that an operation that finishes before another operation begins is also ordered before it in the linearised schedule. The transactional memory system thus presents to the programmer the illusion that threads execute with mutual exclusion even though they are in fact accessing the data structure in parallel.

The rest of this chapter surveys various transactional memory systems starting with hardware transactional memory and then moving on to software transactional memory. I then focus on software transactional memory and discuss ways to apply transactional memory instrumentation to programs. Next, I discuss means for specifying synchronisation to the underlying transactional memory system and its interaction with the memory consistency model. Finally, I discuss the system built in this dissertation in comparison to other transactional memory research.

# 2.1 Hardware transactional memory

One of the earliest proposals for hardware transactional memory [HM93] proposed allowing a sequence of memory operations to be made atomic by piggy-backing on existing and widely used cache coherence protocols. Herlihy et al. proposed additional instructions for transactional load (LT) and transactional store (ST), both of which operate on memory addresses. They also added one to validate the currently executing transaction (VALIDATE) and finally one to commit the currently executing transaction (COMMIT). Using these extensions to the instructions set architecture, one can write code to add a node to a concurrent sorted linked list, as illustrated in Figure 2.1. The example uses the LT instructions to load pointers to successive nodes until the right successor has been determined. It then uses the ST instruction to insert the new node. If the commit using the COMMIT instruction succeeds it breaks out of the loop. Otherwise, it waits for a time dictated by an exponential backoff (to avoid transactions starving each other). Also interesting is the use of the VALIDATE instruction. It ensures that the data set of the transaction (locations read and written) have not been accessed by other threads and thus the thread's view of shared memory (in this case the linked list nodes determined to have a smaller value than that of the node being inserted) is *consistent*.

The implementation proposed by Herlihy et al. consisted of an extra transactional cache that was smaller than and held data exclusive from that in the normal cache of the processor. Transactional loads and stores placed their accessed cache lines in the transactional cache. Lines in the transactional cache accessed by the current transaction (such as those holding linked list nodes in the example) were either in XCOMMIT or XABORT states. The former state labeled lines that were to be discarded on a successful commit, while the latter state was for lines that were to be discarded on an abort. Every line filled in the transactional cache would have a second copy added, with one placed in the XCOMMIT and one in the XABORT state. Crucially, stores would only be made to lines in the XABORT states and thus stores were buffered and discarded in case

```

typedef struct node_st {

int value;

struct node_st *next;

} node_t;

node t * head;

void add_node(node_t * new)

{

node_t **pcur;

node_t *cur;

while(true) {

pcur = &head;

while(VALIDATE()) {

cur = LT(pcur);

if(cur == NULL)

ST(pcur, new)

break;

}

if(LT(&cur->value) >= new->value) {

new->next = cur;

ST(pcur, new);

break;

}

pcur = &cur->next;

if(COMMIT())

break;

exponential_backoff();

}

}

```

Figure 2.1: Sorted linked list using Herhily et al's HTM instructions

the transaction aborted. This capability to roll back speculative changes is fundamental to the way transactional memory (both the hardware and software variants) operates.

Subsequently, hardware transactional memory matured to the point where it was proposed as the *sole* means of synchronisation with coherency and consistency built around the idea of a transaction [HWC<sup>+</sup>04]. Hammond et al. proposed that *all* code be run in transactions with transaction boundaries marking points where speculative changes are committed back to main memory. Their objective was to simplify the cache coherence and memory consistency for large scale chip multiprocessors. They did away with the conventional snoopy or directory based protocols. Instead, processors arbitrated for commit ordering and broadcasted writes within a transaction as a broadcast packet. Processor caches only snooped the broadcast packets which could

```

typedef struct node_st {

int value;

struct node_st *next;

} node_t;

node t * head;

void add_node(node_t * new)

{

node_t **pcur;

node_t *cur;

TRANSACTION_BEGIN_MARKER()

pcur = \&head;

while(1) {

cur = *pcur;

if(cur == NULL) {

*pcur = new;

break;

}

if(cur->value >= new->value) {

new->next = cur;

*pcur = new;

break;

pcur = &cur->next;

TRANSACTION_END_MARKER()

}

```

Figure 2.2: Sorted linked list using Hammond et al's TCC

result in the currently running transaction being aborted in the event of a conflicting write from a previously committed transaction. The HTM system of Hammond et al. results in the broadcast of occasional large packets (4KB-8KB based on their simulations). This requires larger amounts of bandwidth from the interconnect but is relatively latency insensitive as compared to traditional cache coherence protocols that require low latency transfers of smaller amounts of data. Furthermore, within a transaction there was no need to order reads or writes, with the transactional memory system providing the illusion of sequential consistency to committed transactions. Another interesting contrast between the proposal of Hammond et al. and that of Herlihy made a decade earlier is the software interface. Hammond et al. do away with transactional loads and stores. Instead all operations within transactions are handled transactionally (which is the only mechanism to access memory). The linked list example thus simplifies to Figure 2.2. The simplification is due to the fact that Hammond et al's system was targeted towards general purpose concurrent code rather than simply lock-free data structures.

Both the proposals of Herlihy et al. and Hammond et al. chose to retain the original as well as modified versions of cache lines in a transaction. On a commit the original version was discarded while on an abort the modified version was discarded. In the case of Herlihy's proposal both versions were kept in the transactional cache while Hammond chose to depend on main memory for the original (unmodified) version. Moore et al. [MBM+06] made the observation that in the common case when the commit succeeds, keeping the old version around was wasteful. They came up with an HTM that applied changes directly to cache lines and chose to log old values into a special "before-image" log. Commits reduce to simply flash clearing marking bits for cachelines written in the transaction and discarding the log.

A common problem with early hardware transactional memory proposals had been cases where transactions overflowed the cache (or a set in a set-associative cache). Rajwar et al. proposed a solution to this problem by virtualising the transactional logs into virtual memory of the process [RHL05]. In the (assumed) common case where transactions fit in cache, they use a standard HTM. If the transaction overflows the cache, the data and associated tags are placed in a log in the process's virtual memory. Incoming snoops would need to lookup this log (using a firmware or software walker). They further proposed reducing this cost by maintaining a bloom filter to filter out incoming snoops before initiating an expensive walk of the virtual memory log in software.

In spite of the wealth of research into hardware transactional memory there has thus far been only one manufactured mainstream microprocessor that incorporated general purpose HTM. The Rock microprocessor from the SPARC family (now cancelled) incorporated a best-effort hardware transactional memory [DLMN09]. Modestly sized hardware transactions can be executed using Rock's hardware transactional memory. Interestingly functions calls, "difficult" instructions such as division, and TLB misses are not allowed in a transaction (in addition to capacity limits) and the authors point to this being a serious impediment in their attempts to apply the HTM to various benchmarks. In general the HTM is "best-effort" with no guarantee that a transaction can be executed entirely in hardware. The authors recommend using it to assist an alternative software transactional memory implementation that guarantees eventual transaction commit to obtain best performance without undue restrictions on the contents of transactions (I discuss hybrid transactional memory implementations later in the chapter).

Due to the absence of hardware transactional memory support in mainstream processors, software transactional memory has also received considerable attention in the research community. I discuss software transactional memory in the next section.

# 2.2 Software transactional memory

Software transactional memory was proposed by Shavit and Touitou in 1995 [ST95], clearly inspired by the then recent proposal of hardware transactional memory by Herlihy et al. However,

they wanted to implement general purpose transactional memory entirely in software by making use of an atomic compare-and-swap instruction<sup>1</sup> that was available in most architectures. Furthermore, although the proposal of Herlihy et al. was termed "lock-free" since it did away with mutual exclusion locks, it was in fact blocking because threads could end up infinitely aborting each other. Shavit et al's solution was implemented entirely in software and allowed threads to execute transactions with a non-blocking guarantee: some thread would make progress as long as any (not necessarily the same) thread was able to execute instructions.

### 2.2.1 Non-blocking data structures

Software transactional memory has essentially evolved from research into non-blocking data structures. In general non-blocking data structures are those where the suspension of one or more executing threads does not prevent other threads from making progress. This distinguishes such data structure designs from those using a lock, since suspending a thread holding a lock means that other threads requiring the same lock cannot make progress. In the worst case all threads would need the lock leading to no progress in the system. There are three types of non-blocking guarantees:

- Wait freedom guarantees that every thread completes it operation within a constant number of steps regardless of the suspension of other threads.

- Lock freedom guarantees that as long as some thread in the system takes steps, some (not necessarily the same) thread will complete its operation on the data structure.

- Obstructions freedom guarantees that any thread that continues taking steps will complete its operation regardless of the suspension of other threads.

Wait freedom, lock freedom and obstruction freedom thus provide successively weaker guarantees. Various algorithms have been proposed for data structures with non-blocking guarantees, such as lock free double-ended queues [Mic03] and their obstruction free variant [HLM03]. The primary difficulty with these designs is that they are limited to specific data structures and algorithms. One of the motivators for early STMs was that they could be used to implement any data structure with the needed non-blocking guarantee, starting from simple single-threaded algorithms for that data structure.

# 2.2.2 Non-blocking STMs

Shavit et al.'s work spawned a number of STM designs that incorporated some form of non-blocking guarantee. These were classified (in retrospect) into two primary classes.

$<sup>^{1}</sup>$ cas (loc, old, new): atomically check if the current contents of loc is old and if so set it to new. Return the contents of loc that was read.

The first class of STM designs comprises of lock-free ones. As described above an STM design is lock-free if some thread makes progress towards completing a transaction as long as *any* thread is able to execute instructions. The underlying feature of lock-free STM designs is "recursive helping". A thread on encountering an obstruction in executing its transaction (possibly due to the obstructing thread being unable to run) helps the obstructing thread complete its transaction before continuing execution of its transaction. Shavit et al.'s original proposal was lock-free but could deal with only static sized transactions (where the set of reads and updates were known a-priori). Also Shavit et al.'s proposal was evaluated on a simulator and thus left some question about the practical applicability of lock-free STM designs. A more practical STM for dynamic data structures that is also lock-free is Keir Fraser's Object-Based Software Transactional Memory (OSTM) [Fra03]. One of the key contributions of Fraser's thesis was a comparison of red-black tree and skiplist data structures on actual NUMA systems when built using the best available fine grained locking mechanisms versus OSTM. He showed that OSTM was able to outperform locks except at low thread counts, thus establishing the practical possibilities for software transactional memory to scale general purpose code.

An alternative to lock freedom for software transactional memory is obstruction freedom. This is a stronger guarantee than that provided by a simple lock since if any other thread holds a necessary lock, suspending it will preclude any thread from completing. On the other hand this is a weaker guarantee than lock freedom. There is no guarantee that any thread makes progression towards completing its transaction: on encountering an obstruction, obstruction free implementations either choose to abort the current transaction or abort the obstructing transaction. It is thus possible for transactions to abort each other indefinitely, leading to livelock. However, obstruction freedom admits substantially simpler implementations than lock-free STMs. One of the earliest proposals for obstruction free STMs was Dynamic Software Transactional Memory (DSTM) [HLMS03]. In addition to proposing obstruction freedom as a simpler non-blocking guarantee, this was one of the first STMs to allow dynamically allocated objects to be accessed transactionally, thus allowing concurrent versions of dynamic data structures such as linked lists and trees to be implemented.

A key challenge in designing transactional memory with any kind of progress guarantee is handling STM metadata. A fundamental building block in non-blocking STM designs is the capability to atomically switch the state of entire objects from the current to the next version when a transaction modifying it commits. For example in the case of DSTM each object consisted of a header that pointed to a transactional locator. The locator object consisted of a pointer to the transaction that had last opened it for write, a pointer to an old version and pointer to a new version. If the transaction pointed to had committed, then the new version was the correct version to use for transactions reading the object. On the other hand if the transaction had aborted, then the old version was the correct version to use. If the transaction was still running, DSTM (in the spirit of obstruction freedom) allowed the accessing transaction to either wait or abort the

obstructing transaction. This double indirection is a source of significant overhead and hence later obstruction free designs (such as Rochester Software Transactional Memory [MSH+06]) reduced the number of indirections to one. Non-blocking Zero Indirection Software Transactional Memory (NZSTM) [TWGM07] further reduced this overhead with a metadata design that – in the common case of an uncontended object – required no indirection.

Another interesting challenge, specific to obstruction free STMs, is tackling livelock. The job of deciding whether an obstructing transaction should be aborted or waited for was delegated to a 'contention manager', which is responsible for ensuring progress in the system. Obstruction free STMs spawned extensive research into contention management (a good example being that in RSTM [SS05]), which could be plugged into the obstruction free implementation, regardless of the actual STM design. Contention managers usually employed randomised backoff with some form of heuristic to decide when to abort an obstructing transaction. The heuristics are driven by feedback about commit and abort events and present a rich design space. For example, 'timestamp' based contention managers give precedence to older transactions. On the other hand 'karma' style contention managers take into account the amount of work done by competing transactions when deciding which one to abort.

#### 2.2.3 Lock-based STMs

An alternative to STM systems that provide some kind of non-blocking guarantees are *lock-based* STMs. Ennals [Enn05] argued that non-blocking guarantees were an unnecessary source of overhead in STM design. He based his reasoning on two key observations. The first is that a runtime could tailor the number of running threads to the number of cores (hardware threads) available. This makes it unlikely that an operating system would swap out a thread running a transaction thereby leading to an obstruction. The second is that thread failure still remains a problem for non-transactional versions of the program or non-transactional parts of the same program. Thus, guarding against thread failure with a non-blocking guarantee is not very useful in the practical sense. The most important contribution of Ennals' work was however the comparison of his lock-based (blocking) STM design against non-blocking STMs. For example, he showed that his algorithm consistently takes only around 50%—60% of the time taken by Fraser's lock free implementation. As a consequence of avoiding object indirection, he also showed that his algorithm incurred only around 50% of the cache misses and 22% of the TLB misses of Fraser's algorithm for red-black trees.

Lock-based STMs represented a low enough overhead to consider applying STMs to real world programs and spawned much research into building and tuning lock-based STMs. Ennals' work was followed up by Dice et al.'s Transactional Locking 2 (TL2) [DSS06] algorithm that made important advances on the practicality front over the original proposal. It proposed to decouple metadata from data by using out-of-band metadata. This enabled the STM to be

#### Algorithm 1 TL2 algorithms

#### **TransactionBegin:**

ReadVersion := GlobalClock

#### TransactionalWrite(loc, value):

Append (loc, value) to WriteSet

#### **TransactionalRead(loc):**

if (loc, value) in WriteSet then

// Correctly handle read after write cases

Return most recent value from WriteSet

#### else

current metadata := metadata for loc

value := contents of memory at loc

Check metadata for loc is still at current\_metadata

Check metadata for loc is unlocked

Check metadata for loc is not greater than ReadVersion

Append loc to ReadSet

return value

#### **Commit:**

for all (loc, value) ∈ WriteSet do

lock metadata for loc, using bounded spinning to avoid deadlock

Atomically increment GlobalClock by 2, setting WriteVersion to post-increment value

**for all** loc ∈ ReadSet **do**

check metadata for loc is less than or equal to ReadVersion

**for all** (loc, value) ∈ WriteSet in order **do**

set location loc to value

**for all** (loc, value) ∈ WriteSet in order **do**

unlock metadata for loc setting it to WriteVersion

applied "mechanically" through the insertion of read and write "barriers" without requiring extensive data structure changes that would have been necessitated by Ennals' or previous non-blocking proposals. TL2 is also the basis for the STM design I present in this dissertation and hence I discuss the operation of the TL2 STM in some detail.

TL2 uses an out-of-band array of locks and associates each location in memory with a lock in the array, using a straightforward hash function. Each lock is a simple counter that acts both as a version number and a write lock: if the least significant bit is set then the lock is held. The rest of the bits represent the version number. The other globally shared entity is a "timestamp counter" incremented every time a transaction commits. The timestamp counter is used to ensure that speculating transactions see a consistent view of memory. This is referred to as a global clock in the TL2 design. The key steps involved in executing a transaction are listed in Algorithm 1 (if any of the checks listed at any stage fail, the transaction is aborted). Each thread maintains a local read-set of addresses loaded and a local write-set of address-value pairs.

The transaction begins by calling TransactionBegin. Writes within the transaction call TransactionalWrite while reads within the transaction call TransactionalRead. At the end of the transaction Commit is called in order to commit changes back to shared memory, atomically with respect to other transactions.

A number of optimisations are possible to TL2's basic algorithm. Dice et al. themselves proposed a few. For example, checking the local write-set for bypassing values to reads can be done by first checking a bloom filter to filter out the common case where a read does not read any previous write. A number of optimisations are also possible to reduce contention for the global clock. Dice et al. pointed out that incrementing the global clock was unnecessary for transactions that did not perform any writes. A more extensive analysis of commit sequences where an expensive CAS to the globally shared clock could be avoided has also been done [ZBS08].

Another important set of variations to the basic TL2 design can be obtained by changing the point at which locks on written locations are acquired. TL2 followed a lazy approach: locks are acquired only at commit time. An alternative is eager or encounter time locking. In such such a scheme, the lock is acquired when the first write to a location is encountered and writes are performed directly to shared memory. Reads thus no longer need to indirect into the writeset. There is also no need to acquire locks in the commit phase although locks do need to be released. However with an eager scheme it is necessary to maintain an undo log where the old value of locations are logged. On a transaction abort, the old values are restored from the undo log.

The multi-core runtime STM (McRT-STM) [SATH+06] incorporates both eager and lazy locking but Saha et al. conclude that the eager approach performs better than the lazy one. On the flip side, evaluation of both an eager as well as the original lazy versions of the original TL2 algorithm [CMCKO08] reveals that the lazy version can outperform the eager version on some benchmarks. This is because the eager version is more prone to livelock between competing transactions while the lazy version often allows one of the conflicting transactions to finish, thus reducing the amount of wasted work. Other work has shown that an eager STM suffers more in high conflict scenarios due to the cost of applying the undo-log in order to roll back transactions [DS07]. There is thus no clear consensus on which approach is better, with the accepted conclusion being that no one size fits all benchmarks. Hence, considerations other than pure performance typically drive the decision to pick between the approaches.

## 2.2.4 Word-based and object-based STMs

An important differentiator between STMs of both the non-blocking and lock-based variety is whether they are word-based or object-based. Word-based STMs divide memory into fixed-size chunks and associate external STM metadata with each chunk using a hash function. In contrast, object-based STMs treat memory as composed of variable sized objects with the metadata either

embedded in an object or placed externally and associated with the base address of the object. Fraser [Fra03] proposed both object-based and word-based non-blocking designs in his thesis. RSTM [MSH+06] on the other hand is exclusively object-based. TL2 [DSS06] is a word-based STM while McRT-STM [SATH+06] incorporates both an object-based and word-based STM.

Object-based STMs present both advantages and disadvantages over word-based STMs. A key advantage is that the amount of STM metadata manipulated by a transaction decreases if multiple fields of the same object are accessed. On the other hand, object-based STMs require a precise mapping of field accesses to their containing objects. This is not possible when automatically inserting STM calls in code generated from unmanaged environments such as C/C++ unless there is some amount of source code information present to be taken into consideration by the instrumentation system. In general word-based STMs are preferred in such unmanaged environments.

There have been STM designs that try to combine the properties of word-based and object-based STMs. Riegel et al. [RBdB08] proposed a data structure analysis (DSA) pass in their compiler, which could automatically identify object boundaries in compiled code. They then used this information to associate external metadata with object bases rather than with individual fields. Roy et al. [RHH09b] proposed a word-based STM with variable word size. Their proposal however depended on the programmer specifying the object size and base address to their library-based STM.

## 2.3 STM instrumentation

A key problem with practically applying software transactional memory at scale is that of instrumentation. Using software transactional memory in any program involves at the very least delimiting the start and end of a transaction and, more difficult, indirecting every shared memory access to the STM runtime system. There are two prevalent approaches to the problem. The first uses the STM runtime system as a library and inserts appropriate calls to it directly in the source. The second approach makes use of an STM compiler and depends on annotations in the code to delimit transactions; the compiler can then automatically insert instrumentation for shared memory accesses. A third (not so widely used) option is to insert instrumentation at runtime using a dynamic binary rewriting engine. I discuss these three alternatives next.

# **2.3.1** Library

Library-based STMs expose an API to the programmer to insert calls at the start and end of a transaction, as well as calls at every shared memory access. For example, Figure 2.3 shows how the linked list example looks when using the TL2 STM API. The start and end of transactions

```

typedef struct node_st {

int value;

struct node_st *next;

} node_t;

node t * head;

void add_node(node_t * new)

{

node_t **pcur;

node_t *cur;

TxStart(...); // TransactionBegin

pcur = \&head;

while(1) {

cur = TXLoad(..., pcur); // TransactionalRead

if(cur == NULL) {

TxStore(..., pcur, new); // TransactionalWrite

break;

}

if(TxLoad(..., &cur->value) >= new->value) {

new->next = cur;

TxStore(pcur, new);

break;

pcur = &cur->next;

TxCommit(...); // Commit

}

```

Figure 2.3: Linked list using the TL2 library

are delimited by TxStart and TxCommit calls while shared memory loads and stores are indirected through TxLoad and TxStore calls respectively.

Most of the early STM implementations were made available as library-based STMs (since the alternative of compilers was yet to mature). Library-based STMs suffer from two key problems. The first is the large amount of tedious instrumentation that must be inserted by hand. This can often be a source of errors that negates much of the supposed simplicity of using transactional memory. The second problem with library-based STMs is of rolling back aborted transactions. Library-based STMs use setjmp and longjmp calls in order to checkpoint and restore state. While this restores registers, it does not restore variables on stack that are known to be thread-private and not instrumented by the programmer. In Figure 2.3 for example, the pcur and cur variables are changed in the transaction but are not restored on an abort. The programmer is required to ensure that there are no live variables when entering the transaction that are not indirected through the STM.

On the plus side however, library-based STMs empower the programmer to tweak and optimise the instrumentation. For example, the programmer can avoid STM calls for data that is known to be thread-private and not live when entering the transaction. The STAMP benchmark suite [CMCKO08] contains a number of examples of such "programmer-driven optimisation". In Chapter 6 I discuss techniques by which some of the gap between automatically generated instrumentation and this kind of optimised instrumentation can be closed.

## 2.3.2 Compiler

Compiler-based software transactional memory uses the compiler to insert STM instrumentation into programs.

Harris et al. were the first to integrate transactional memory support in a Java compiler [HF03]. Subsequently, Adl-Tabatabai et al. implemented transactional memory support in a Java compiler [ATLM+06] using the McRT-STM (discussed before). Their solution provides language extensions to Java that allowed the programmer to delimit transactions. They used a compiler toolkit that translated these language extensions to library calls into their STM. In the JIT phase, they generated a transactional and a non-transactional version of each method and operated with the guarantee that the transactional version would be called only within a transaction. The transactional version had STM-related instrumentation. An interesting aspect of their instrumentation was that they allowed both object-based and word-based software transactional memory to be used on a type-by-type basis.

Harris at al. [HPST06] presented an STM compiler for the Common Intermediate Language (CIL), meant to execute in a managed runtime similar to .NET. Their implementation was for Bartok, an experimental compiler for CIL. The crucial focus of that work was in optimising memory transactions. They showed that by properly decomposing the STM interface it was possible to perform significant optimisations over a naive insertion of STM calls. For example, with their object-based STM, opening an object for writing could be hoisted out of a loop, while leaving the actual updates to object fields within the body of the loop.

Tanger is a transactifying compiler for C/C++ developed by Felber et al. [FFM+07]. Tanger is a not a compiler by itself but rather a pass in the LLVM [LA04] compiler infrastructure. It instruments code in transactions to use a word-based STM. They showed that the compiler was able to insert and optimise STM instrumentation to a level that was equivalent to hand instrumented code, a major step in terms of automation from library based STMs.

Wang et al. [WCW<sup>+</sup>07] presented an optimising compiler for C/C++ code that supported transactions. They used a variant of the McRT-STM and presented various optimisations that can be done to mitigate the overhead of the STM. A key contribution of Wang et al.'s work however is their focus on *safety*. They showed that integrating an STM into an unmanaged environment such as C/C++ that allowed pointer arithmetic and did not guarantee type safety is extremely

challenging. Some of the problems they pointed out, such as the added difficulties in supporting a programming construct called privatisation are also relevant to this dissertation. I return to these problems later in this chapter.

### 2.3.3 Binary rewriting

A key problem with the compiler-based approach is that it is ineffective when source code is not available. Such a situation occurs, for example, when a transaction calls a legacy library function that has not been 'transactified'. An alternative to compiler-based instrumentation is to start with compiled code and insert instrumentation directly at the machine code level. Some of the early work in using binary rewriting focused on *supporting* STM compilers.

Felber et al. [FFM<sup>+</sup>07] proposed using a static binary rewriting scheme to instrument such legacy x86 libraries using a tool they called Tarifa (their LLVM module was called Tanger). Tarifa uses a static rewriting scheme (along the lines of ATOM [SE94]) where the legacy library is first disassembled, instrumentation is inserted and finally the instrumented assembly code is assembled back into machine code. Their conclusion was that, while using binary instrumentation did not introduce any fundamental scalability limits, nevertheless it added significant overhead to code generated and optimised by Tanger.

Wang et al. [WYW08] developed a tool called LDBTOM (Lightweight Dynamic Binary Translation and Optimization Module) to allow legacy x86 code to be called within a transaction compiled with an STM capable compiler. LDBTOM was developed to complement the STM compiler developed by the same authors. Wang et al. also report a significant overhead over compiler generated code.

Olszewski et al. [OCS07] developed JudoSTM on top of their binary rewriting engine, Judo. JudoSTM depended on marker functions being inserted in the source code to delimit transactions and inserted transactional barriers automatically. Interesting aspects of their STM included the use of value-based validation and generation of transaction-instance-specific commit sequences – sequences of x86 instructions for each executed transaction – specific to the read and write set. They obtained extremely efficient commit in return for the instruction cache miss costs. JudoSTM reported comparable performance to RSTM (manually instrumented) for counter, linked list and hash table benchmarks.

# 2.4 Atomicity specifications

Transactional memory is a way to execute sections of code atomically. While the previous sections have surveyed *mechanisms* to execute transactionally this section focuses on *policy* i.e. atomicity related synchronisation constructs used in programs. There have been two primary constructs that assist programmers in specifying synchronisation using transactional memory.

```

typedef struct node_st {

int value;

struct node_st *next;

} node_t;

node t *head;

void add_node(node_t * new)

{

node_t **pcur;

node_t *cur;

atomic {

pcur = &head;

while(1) {

cur = *pcur;

if(cur == NULL) {

*pcur = new;

break;

}

if(cur->value >= new->value) {

new->next = cur;

*pcur = new;

break;

pcur = &cur->next;

}

}

}

```

Figure 2.4: Sorted linked list using atomic blocks

#### 2.4.1 Atomic block

The notion of building language-level atomic blocks using transactional memory was introduced by Harris et al. [HF03] in the context of the Java programming language. They advocated the atomic block for declarative concurrency control as a first class language feature.

Although Harris et al.'s original proposal for atomic blocks was in the context of Java, atomic blocks are a popular means for expressing synchronisation when using transactional memory. Both library-based STMs such as TL2 as well as compilers for unmanaged environments such as Wang et al.'s compiler chose to expose transactional memory to the programmer through atomic blocks. Figure 2.4 shows how the sorted linked list example of this chapter can be expressed using atomic blocks.

Atomic blocks have the key advantage of composability when compared to the more imperative style of expressing synchronisation using locks. Consider the problem of removing a node from

```

int x=0

// Thread 1

// Thread 2

lock(11);

do {

lock(12);

lock(12);

x = 100;

t2 = x;

unlock(12);

unlock(12);

\} while (t2 != 100);

do {

lock(12);

lock(12);

t1 = x;

x = 200;

unlock(12);

unlock(12);

\} while (t1 != 200);

unlock(11);

```

Figure 2.5: A barrier for two threads

a sorted linked list and reinserting the node into another, while making the operation appear atomic. A concurrent thread searching both lists for the node (value) should be guaranteed to find it. Thread-safe building blocks for the individual operations are available either using atomic blocks or locks.

Using atomic blocks the solution would simply involve enclosing both operations in a larger atomic block<sup>2</sup>, thereby *composing* the smaller fragments into a larger one. Using locks protecting the individual lists on the other hand, one would have to worry about lock acquisition order to avoid deadlock.

#### 2.4.2 Lock elision

Despite the popularity of atomic blocks as a language level interface to transactional memory, researchers have explored lock elision as an alternative. Lock elision assumes that locks continue to be the method of synchronisation. Transactional memory provides a best effort execution of the enclosed critical section by eliding (not acquiring) the lock and hence not waiting for it. If execution of the critical section using the lock fails for some reason, it can be re-executed with the lock held, without using transactional memory. Lock elision has three important advantages over atomic blocks.

The first advantage is that existing synchronisation constructs that use locks need not necessarily have a straightforward transformation to atomic blocks. Starting from legacy code, one might be tempted to simply remove the lock and unlock calls and instead enclose critical sections in atomic blocks. This is not always correct. Consider a barrier between two threads, as shown in Figure 2.5. The lock 12 protects the shared variable x that is used for synchronisation

<sup>&</sup>lt;sup>2</sup>Atomic blocks allow themselves to be nested.

between the threads. In the case of Thread 1 the entire barrier code is executed while holding lock 11. If the locks were to be replaced with (nested) atomic blocks in a straightforward transformation, no forward progress is possible since the atomic blocks cannot be serialised in a way that allows forward progress<sup>3</sup>. On the other hand, the commonly used Single Lock Atomicity (SLA) semantics of atomic blocks can be simulated with a single process-wide recursive lock.

The second reason is legacy code. In spite of much research focus on atomic blocks, locks continue to be the most popular method of synchronisation for programmers. Lock elision allows the scalability benefits of transactional memory to be obtained for legacy code without requiring it to be be rewritten using atomic blocks. Even with an STM compiler and rewritten source code, legacy libraries become a problem if they acquire locks.