# Modelling energy efficiency for computation

## Charles Reams

University of Cambridge

Computer Laboratory

Clare College

April 2012

This dissertation is submitted for the degree of Doctor of Philosophy

## Declaration

This dissertation is the result of my own work and includes nothing that is the outcome of work done in collaboration except where specifically indicated in the text. This dissertation does not exceed the regulation length of 60 000 words, including tables and footnotes.

#### Work done in collaboration

Chapter 3 of this thesis comprises an extended revision of an article co-authored with David Brown, which appeared in the Communications of the ACM [Brown and Reams, 2010]. The remaining work is my sole undertaking.

#### Summary

In the last decade, efficient use of energy has become a topic of global significance, touching almost every area of modern life, including computing. From mobile to desktop to server, energy efficiency concerns are now ubiquitous. However, approaches to the energy problem are often piecemeal and focus on only one area for improvement.

I argue that the strands of the energy problem are inextricably entangled and cannot be solved in isolation. I offer a high-level view of the problem and, building from it, explore a selection of subproblems within the field. I approach these with various levels of formality, and demonstrate techniques to make improvements on all levels. The original contributions are as follows.

Chapter 3 frames the energy problem as one of *optimisation with constraints*, and explores the impact of this perspective for current commodity products. This includes considerations of the hardware, software and operating system. I summarise the current situation in these respects and propose directions in which they could be improved to better support energy management.

Chapter 4 presents mathematical techniques to compute energy-optimal schedules for long-running computations. This work reflects the server-domain concern with *energy cost*, producing schedules that exploit fluctuations in power cost over time to minimise expenditure rather than raw energy. This assumes certain idealised models of power, performance, cost, and workload, and draws precise formal conclusions from them.

Chapter 5 considers techniques to implement energy-efficient real-time streaming. Two classes of problem are considered: first, hard real-time streaming with fixed, predictable frame characteristics; second, soft real-time streaming with a quality-of-service guarantee and probabilistic descriptions of per-frame workload. Efficient algorithms are developed for scheduling frame execution in an energy-efficient way while still guaranteeing hard real-time deadlines. These schedules determine appropriate values for power-relevant parameters, such as dynamic voltage—frequency scaling.

A key challenge for future work will be unifying these diverse approaches into one "Theory of Energy" for computing. The progress towards this is summarised in Chapter 6. The thesis concludes by sketching future work towards this Theory of Energy.

#### Acknowledgements

First I would like to thank my supervisor Prof. Alan Mycroft, whose faith in my ability to complete this work always exceeded my own. I hope I have repaid the trust and freedom he has granted me over the last three and a half years.

I must also thank my family, who unknowingly put me on the road to this PhD twenty years ago when they would allow me to play on my Game Boy until (the agony!) the batteries ran out. I would also like to thank Emma Seaber, who tolerated the long and difficult labour that birthed this thesis with exceptional grace, and feigned interest in Pareto frontiers far beyond the call of duty. There are not enough Nutrageouses to repay you.

Many more people deserve a mention than this space will allow, but to select a few: Michael Wallace, Miloš Puzović, and Greg Chadwick for making it so much more than the work, and David Brown, who on many occasions showed me the light at the end of the tunnel. Thank you all.

My final thanks belong to Clare College, whose Domestic Research Scholarship supported me throughout my studies.

This thesis is dedicated to the memory of my late grandfather, Jim Burnett, who lived to see the first words of this thesis but not the last. As the more mathematical chapters demonstrate, I have inherited his enthusiasm for brackets.

# Contents

| 1 | Intr | oducti                  | on                                              | 13 |  |  |

|---|------|-------------------------|-------------------------------------------------|----|--|--|

|   | 1.1  | Centra                  | al thesis                                       | 14 |  |  |

|   | 1.2  | Contri                  | ibutions                                        | 15 |  |  |

|   | 1.3  | Chapt                   | er plan                                         | 15 |  |  |

| 2 | Sur  | Survey of previous work |                                                 |    |  |  |

|   | 2.1  | The m                   | neaning of energy awareness                     | 17 |  |  |

|   | 2.2  | Energy                  | y-aware hardware                                | 18 |  |  |

|   |      | 2.2.1                   | Historical trends in hardware energy efficiency | 20 |  |  |

|   |      | 2.2.2                   | Future tends in hardware energy efficiency      | 23 |  |  |

|   |      | 2.2.3                   | Energy characteristics at sub-peak performance  | 26 |  |  |

|   | 2.3  | Energy                  | y-aware operating systems                       | 29 |  |  |

|   | 2.4  | Energy                  | y-aware protocols                               | 30 |  |  |

|   |      | 2.4.1                   | Energy-aware data protocols                     | 30 |  |  |

|   |      | 2.4.2                   | Energy management protocols                     | 32 |  |  |

|   | 2.5  | Energy                  | y-aware software                                | 33 |  |  |

|   | 2.6  | Summ                    | ary of related work                             | 35 |  |  |

| 3 | Tow  | vards e                 | energy-efficient computing                      | 37 |  |  |

|   | 3.1  | Energy                  | y in the computing space                        | 38 |  |  |

|   | 3.2  | Moder                   | n power management                              | 41 |  |  |

CONTENTS

|   |     | 3.2.1    | ACPI                                            | 43         |

|---|-----|----------|-------------------------------------------------|------------|

|   | 3.3 | Energ    | y efficiency in computing                       | 43         |

|   |     | 3.3.1    | Maintenance of required performance             | 44         |

|   |     | 3.3.2    | Response to changes in demand                   | 45         |

|   |     | 3.3.3    | Power capping                                   | 46         |

|   |     | 3.3.4    | Summary of constraints                          | 46         |

|   | 3.4 | Direct   | ions toward a solution                          | 47         |

|   |     | 3.4.1    | Power model                                     | 47         |

|   |     | 3.4.2    | Workload constraints and performance assessment | 48         |

|   |     | 3.4.3    | Energy optimisation by the system               | 49         |

|   | 3.5 | Route    | s towards energy efficiency                     | 51         |

|   |     | 3.5.1    | Considerations for the operating system         | 51         |

|   |     | 3.5.2    | The evolution of application software           | 56         |

|   | 3.6 | Conclu   | ısion                                           | 57         |

| 4 | Cos | t optir  | nisation for power-aware computing              | <b>5</b> 9 |

|   | 4.1 | Motiva   | ation                                           | 59         |

|   | 4.2 | Relate   | d work                                          | 61         |

|   |     | 4.2.1    | Dynamic voltage–frequency scaling               | 62         |

|   |     | 4.2.2    | Other formal methods                            | 65         |

|   | 4.3 | Defini   | tion of terms                                   | 65         |

|   | 4.4 | Proble   | em statement                                    | 66         |

|   | 4.5 | Forma    | l model                                         | 66         |

|   |     | 4.5.1    | Assumptions and justification                   | 68         |

|   | 4.6 | Solution | ons for specific cost models                    | 70         |

|   |     |          | Constant cost                                   | 70         |

| CONTENTS |

|----------|

|          |

|   |     | 4.6.2   | General discrete variable cost           | <b>'</b> 5     |

|---|-----|---------|------------------------------------------|----------------|

|   |     | 4.6.3   | Real-world example                       | 7              |

|   |     | 4.6.4   | Exponential cost                         | 30             |

|   |     | 4.6.5   | Generalised time intervals               | 31             |

|   |     | 4.6.6   | Summary of cost model-specific solutions | 34             |

|   | 4.7 | Gener   | al methods                               | 35             |

|   |     | 4.7.1   | Monotonic cost functions                 | 35             |

|   |     | 4.7.2   | Constant spending                        | 37             |

|   | 4.8 | Conclu  | ısion                                    | 38             |

| 5 | Ene | rgy-efl | ficient real-time streaming 9            | 3              |

|   | 5.1 | Introd  | uction                                   | )3             |

|   |     | 5.1.1   | Definition of an operating point         | <del>)</del> 6 |

|   |     | 5.1.2   | Assumptions regarding operating points   | )7             |

|   | 5.2 | Proble  | em statement                             | )9             |

|   | 5.3 | Relate  | ed work                                  | )2             |

|   | 5.4 | Algori  | thm description                          | )5             |

|   |     | 5.4.1   | Dominated points                         | )7             |

|   |     | 5.4.2   | Downscaling                              | .0             |

|   | 5.5 | Evalua  | ation                                    | .1             |

|   |     | 5.5.1   | Diminishing returns                      | . 1            |

|   |     | 5.5.2   | Simulation                               | .3             |

|   |     | 5.5.3   | Heuristic improvements                   | .6             |

|   |     | 5.5.4   | Evaluation of domination                 | .6             |

|   | 5.6 | Proba   | bilistic generalisation                  | .7             |

|   |     | 5.6.1   | Probabilistic model                      | 17             |

| CONTENTS | CONTENT |

|----------|---------|

| CONTENTS | CONTEIN |

|              |       | 5.6.2  | Suitability for practical soft real-time problems       | . 119 |

|--------------|-------|--------|---------------------------------------------------------|-------|

|              |       | 5.6.3  | Assumption of normality                                 | . 120 |

|              |       | 5.6.4  | Probabilistic manifestation                             | . 121 |

|              |       | 5.6.5  | Probabilistic algorithm                                 | . 122 |

|              |       | 5.6.6  | Generalised domination                                  | . 124 |

|              |       | 5.6.7  | Probabilistic evaluation                                | . 126 |

|              |       | 5.6.8  | Probabilistic summary                                   | . 130 |

|              | 5.7   | Conclu | asion                                                   | . 130 |

| 6            | Con   | clusio | ns                                                      | 135   |

|              | 6.1   | Conclu | uding argument                                          | . 135 |

|              | 6.2   | Future | e directions                                            | . 137 |

|              |       | 6.2.1  | Future work on the theory of energy-efficient computing | . 138 |

|              |       | 6.2.2  | Future work on cost-efficient computing                 | . 139 |

|              |       | 6.2.3  | Future work on energy-efficient streaming               | . 140 |

| Aı           | ppen  | dices  |                                                         | 141   |

| $\mathbf{A}$ | Fut   | ure wo | rk: online learning in hard real-time                   | 141   |

|              | A.1   | Introd | uction                                                  | . 141 |

|              | A.2   | Motiva | ation                                                   | . 141 |

|              | A.3   | Proble | em outline                                              | . 143 |

|              | A.4   | Propos | sed methodology                                         | . 144 |

|              | A.5   | Challe | enges                                                   | . 144 |

|              | A.6   | Relate | ed work                                                 | . 146 |

| Bi           | bliog | graphy |                                                         | 149   |

Glossary

# List of Figures

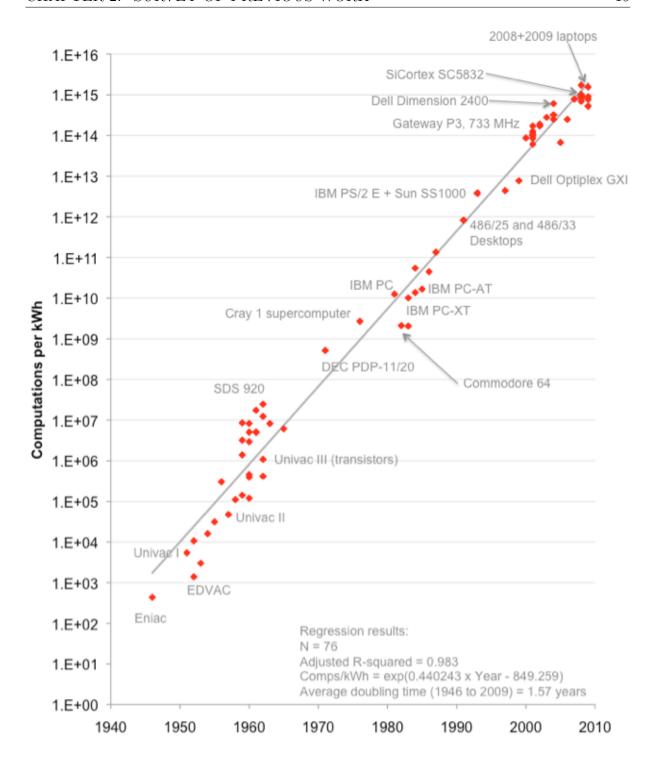

| 2.1 | Graph of computations per unit energy through history, in support of Koomey's Law. Reproduced from [Koomey et al., 2011]                                                                                       | 19 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

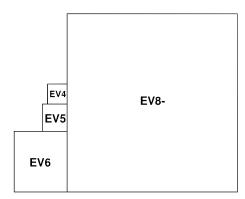

| 2.2 | Size comparison of a set of DEC Alpha cores from a heterogeneous multi-<br>core chip; each core is labelled with the single-core chip in which it originally<br>appeared. Reproduced from [Kumar et al., 2003] |    |

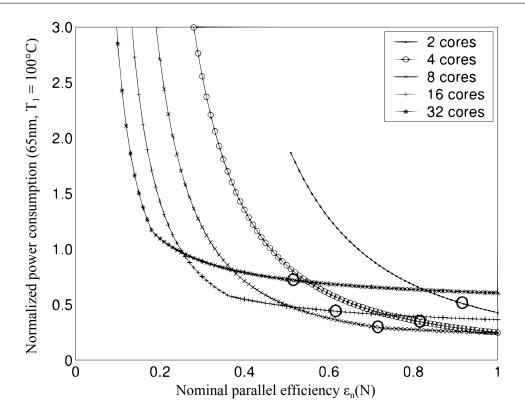

| 2.3 | Plot of power consumption against nominal parallel efficiency for various numbers of cores. Reproduced from [Li and Martínez, 2005]                                                                            | 24 |

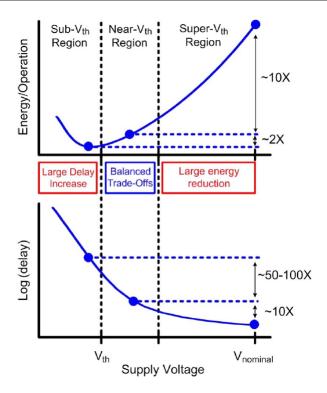

| 2.4 | Transistor behaviour in sub-, near-, and super-threshold operating voltage regions. Reproduced from [Dreslinski et al., 2010]                                                                                  | 28 |

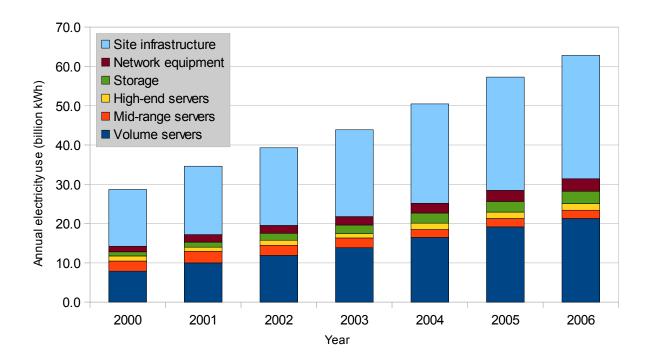

| 3.1 | Energy usage breakdown by equipment type in United States, from 2000 to 2006                                                                                                                                   | 39 |

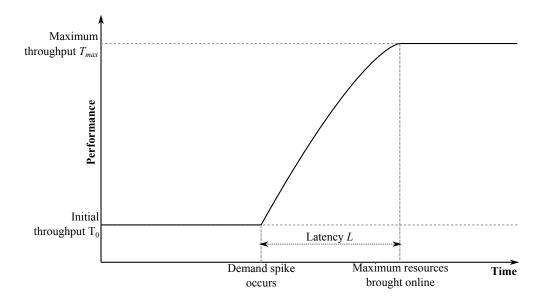

| 3.2 | Time-throughput diagram showing latency to reach maximum performance.                                                                                                                                          | 46 |

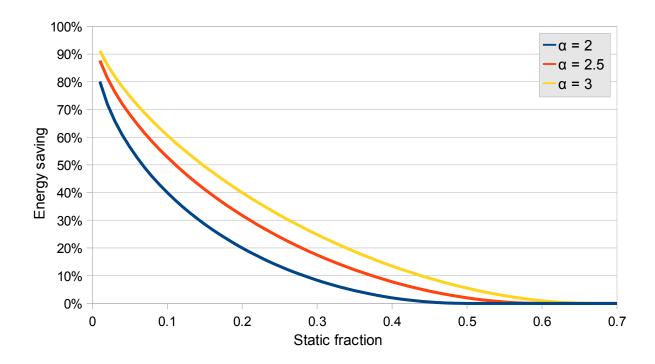

| 4.1 | Potential cost saving $\lambda$ , as a percentage, against static fraction $\mu$ , for some realistic $\alpha$ values                                                                                          | 74 |

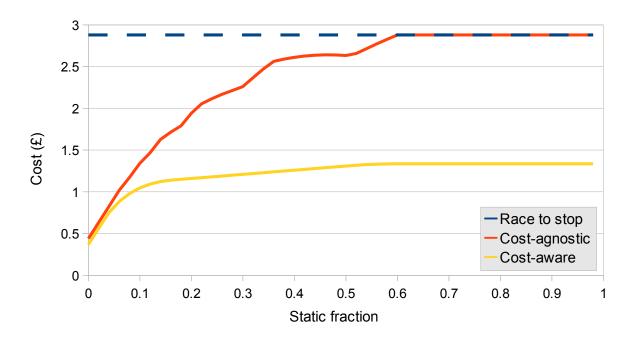

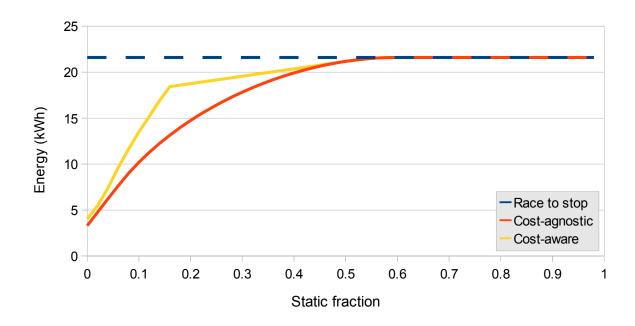

| 4.2 | Cost incurred to perform a long-running computation, for various ratios of static to dynamic power                                                                                                             | 78 |

| 4.3 | Energy required to perform a long-running computation, for various ratios of static to dynamic power                                                                                                           | 79 |

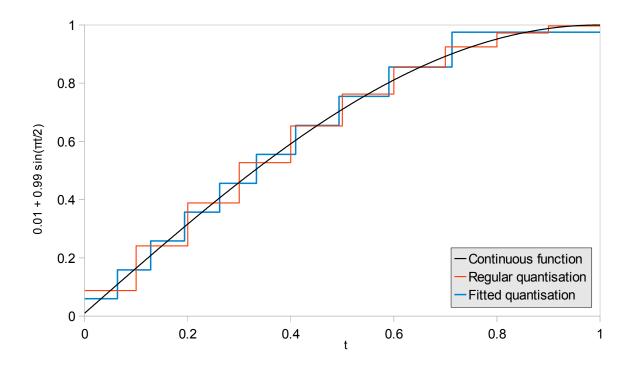

| 4.4 | A continuous cost function and two different methods of discretising it into ten steps                                                                                                                         | 82 |

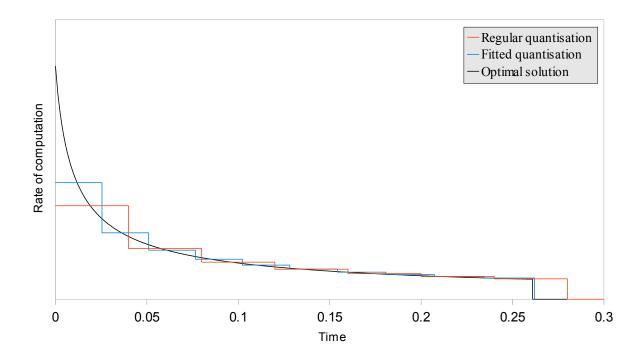

| 4.5  | Schedules for two different quantised approximations to the same continu-             |

|------|---------------------------------------------------------------------------------------|

|      | ous cost function. Arbitrary units of rate                                            |

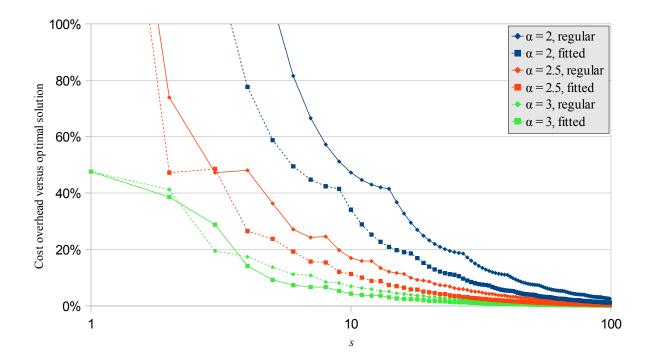

| 4.6  | Comparison of cost overheads incurred by regular and fitted quantisations             |

|      | for several values of $\alpha$ . Horizontal axis is on a logarithmic scale 84         |

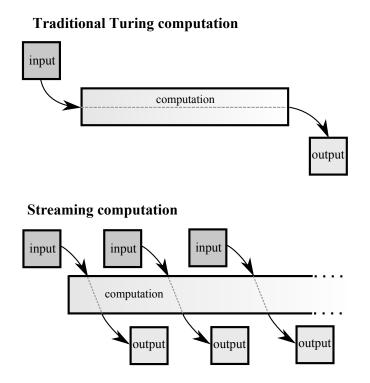

| 5.1  | Comparison of the traditional Turing model and streaming computation 94               |

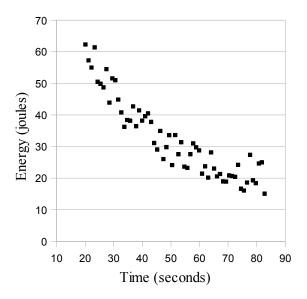

| 5.2  | Example set of operating points                                                       |

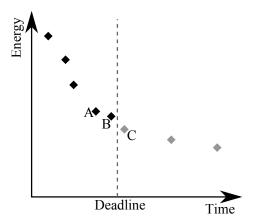

| 5.3  | An example set of operating points and a per-frame deadline shown in                  |

|      | energy—time space                                                                     |

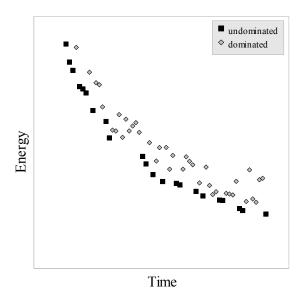

| 5.4  | Example set of operating points, showing dominated and undominated                    |

|      | points, arbitrary units                                                               |

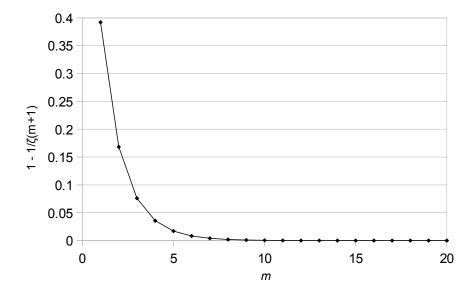

| 5.5  | Probability that integer time values generated uniformly at random have               |

|      | a common factor, as a function of $m$ , the number of values                          |

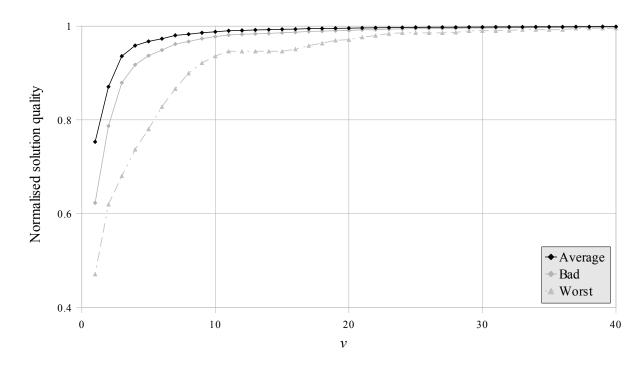

| 5.6  | $q_{\nu}$ for increasing values of $\nu$ , averaged over one hundred random examples. |

|      | Note that the vertical axis starts at 0.4                                             |

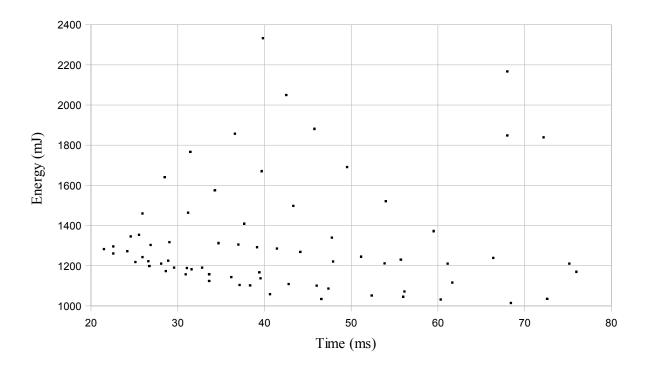

| 5.7  | Energy-time diagram for real BSOM operating points                                    |

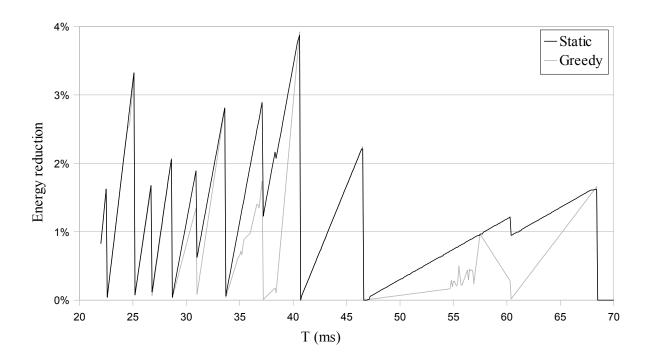

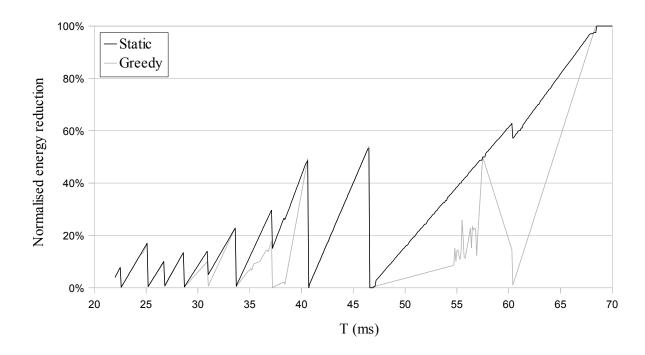

| 5.8  | Comparison of the per-frame energy reduction achieved by my static algo-              |

|      | rithm and a dynamic greedy algorithm                                                  |

| 5.9  | Comparison of the per-frame energy reduction achieved, as a fraction of               |

|      | the available maximum                                                                 |

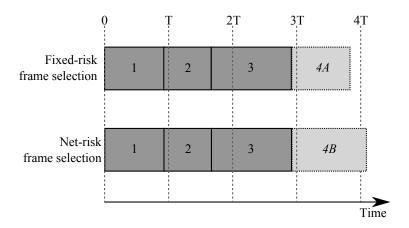

| 5.10 | Diagram showing the variable deadline encountered by the dynamic frame                |

|      | scheduling algorithm                                                                  |

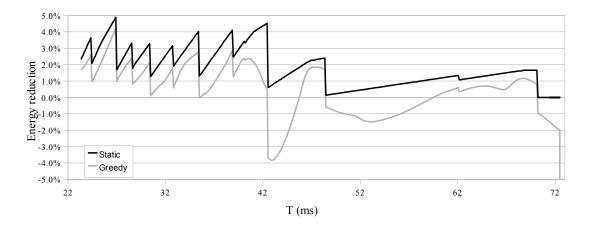

| 5.11 | Comparison of the energy reduction achieved by my static algorithm and                |

|      | a dynamic greedy algorithm for normally distributed execution times $128$             |

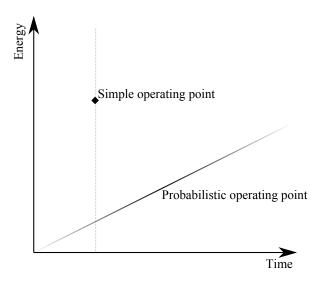

| 5.12 | Two different forms of operating point energy–time description, represented           |

|      | graphically                                                                           |

# List of Tables

| 3.1 | Energy usage breakdown for computing equipment in the United States.  |     |

|-----|-----------------------------------------------------------------------|-----|

|     | Energy figures are in billions of kWh                                 | 40  |

|     |                                                                       |     |

| 5.1 | Average solution time                                                 | 116 |

| 5.2 | Point counts for BSOM data, and comparison to heuristic estimates     | 117 |

| 5.3 | Power reductions measured for the BSOM benchmark. For meaning of col- |     |

|     | umn headings see text                                                 | 120 |

# List of Algorithms

| 1 | Dynamic programming algorithm to find minimal energy which meets the     |

|---|--------------------------------------------------------------------------|

|   | throughput requirement                                                   |

| 2 | Algorithm to find undominated operating points                           |

| 3 | Brute-force algorithm to find frequencies which minimise expected energy |

|   | and meet the probabilistic timing constraint                             |

## Chapter 1

## Introduction

Many fields of computing are currently experiencing a new or renewed interest in energy efficiency. In desktop computing, ecological concerns are forcing hardware designers to refine their traditional assumption that mains electricity is an unlimited source of power. In the server space, energy demands over the lifetime of the hardware are rapidly increasing and may come to dominate the cost of the hardware itself [Barroso and Hölzle, 2007]. In both contexts, reducing power demand from electronic components also reduces the power demand of the cooling subsystem, so savings are multiplied. And of course any form of mobile computing, a huge growth area in the last decade, must consider power efficiency; most obviously from the perspective of maximising battery life, and additionally from the complication of cooling in a mobile context.

The energy problem has diversified considerably in recent years. The range of use cases and attendant hardware and software, from servers to desktops to laptops to tablets to mobile telephones to embedded devices and so on, is now so vast that it is infeasible to attempt to approach all of them simultaneously. This is particularly true if one seeks analytic rather than heuristic solutions, as will generally be the case in this thesis. One might compare the situation to that of physics in the 19th Century; the great breakthrough of James Clerk Maxwell's unification of electricity and magnetism was not possible until the two phenomena were individually well-understood.

In recognition of these difficulties, I make a two-part argument in this thesis: on the one hand, we should not be too hurried to solve all the problems of energy-efficient computing, since such a solution is clearly intractable with our current understanding; on the other hand, we should remain aware of the larger picture as we advance the subproblems, so that opportunities to unify and generalise can be uncovered as they come within reach.

Furthermore, with the central argument in mind, I make headway on some of these particular problems: power cost management and real-time streaming. My intention is that these pieces will ultimately be fitted into a "grand unified theory" of energy-efficient computing.

In power cost management, I generalise traditional notions of energy efficiency to include energy cost efficiency, and argue that these concerns are connected but not identical and that cost optimisation presents an interface to economic reality that is not available if one simply "counts joules". I present formal models connecting power, performance, and cost, and show formal optimisation methods for them. I then investigate whether these optimisations present adequate efficiency savings to justify their deployment in practice.

In real-time streaming, I develop a framework in which tasks in a (potentially infinite) stream can be processed energy-efficiently while still meeting hard real-time dead-lines. This framework includes an abstraction from the particular characteristics of the workload—hardware or software—and, on this platform, presents a generalisation of traditional energy-efficient scheduling techniques such as voltage dithering. I also present algorithms to find these schedules, and explore whether it is possible to compute them in a time- and space-efficient manner. Again, the results of the schedules are tested by simulation against existing approaches, and the energy differential measured.

I conclude with a discussion of what is still to be done towards a unified theory of energy-efficient computing.

#### 1.1 Central thesis

My central thesis is that the subproblems of the energy problem as it pertains to computing are deeply interrelated, and it is necessary to consider the whole before addressing the parts. To support this argument, I survey and discuss the state of the field, and in later chapters, make headway on certain parts—in particular, power cost management and real-time streaming—and relate these back to the problem as a whole.

#### 1.2 Contributions

My contributions to the field are as follows:

- An extensive description of the current situation "on the ground" with regards to energy efficiency, across the server, desktop and mobile sectors.

- The proposal of energy cost as the true metric of optimisation in energy-aware computing.

- Formal methods for solving energy cost problems under realistic cost and performance models.

- The proposal of the *operating point* as a clean abstraction of execution details (in both hardware and software), suitable for general-purpose energy-aware modelling.

- The description of precise algorithms for solving operating point problems in energyefficient streaming, and their time and space characteristics.

## 1.3 Chapter plan

Following this chapter, the chapter structure of this thesis is as follows:

- Chapter 2 surveys various strands in the field of energy-aware computing.

- Chapter 3 presents a large-scale view of several pragmatic levels on which the energy problem might be approached, with a particular emphasis on the view from industry.

- Chapter 4 introduces the concept of energy cost minimisation, describes mathematical techniques by which such minimisation may be achieved, and measures the utility of these techniques.

- Chapter 5 defines the "operating point" and develops a framework for energyefficient hard real-time streaming, based on the concept of operating point dithering.

- Chapter 6 synthesises the results of previous chapters into a single argument, making the final demonstration of the central thesis.

## Chapter 2

## Survey of previous work

Given the diversity of the topics considered in this document, this survey of prior work does not attempt to introduce all of the detailed context immediately; instead, much of the relevant material will be introduced directly in the appropriate chapter. Rather, this chapter serves as a general summary of the state of the art in energy-aware computing, and thereby puts the specific work of later chapters in broader context. Of course, it makes no pretension to cover every area, and is necessarily highly selective in those that are covered, but nevertheless its purpose is the provision of an adequate foundation for the details of what follows.

## 2.1 The meaning of energy awareness

The phrase "energy-aware computing" is carefully chosen, because there are many possible interactions between computation and the energy it requires. For example, in a battery-operated device, the usual objective is to minimise the total energy of a computation; that is, the integral of power with respect to time over the whole computation. In other devices, peak instantaneous power is the more pressing constraint. Some machines, such as spacecraft, may combine solar power with battery back-up, and so are subject to both constraints. Other constraints might include a thermal dissipation limit imposing a maximum average power over a given period of time. Additionally, there are various classes of problem depending on which performance, energy, power and so forth are to be optimised and which are constrained. To further complicate matters, batteries require

quite specific usage profiles to give optimal performance, as described below. Moreover, the machine may not be intended for energy efficiency at all, but pure energy awareness, simply measuring its own energy usage and displaying this to the user or relaying it to an external reporting service. In practical systems, resolving these requires a different approach in each case, so this survey presents as broad coverage of these areas as possible. To recapitulate, my central thesis is that the different parts of the energy problem are closely related and must be considered as one. Consequently, while this chapter catalogues the related work according to the particular area that it targets—hardware, operating system, protocols, and software—this taxonomy does not quite carve nature at the joints,

and so the chapter concludes with a discussion of some interdisciplinary work.

### 2.2 Energy-aware hardware

To call hardware energy-aware seems almost tautological, since hardware is definitionally composed of physical objects subject to the usual laws of thermodynamics. However there is still a distinction to be drawn between three areas of work: techniques by which the hardware itself is made more energy-efficient; mechanisms for monitoring and communicating power and energy values to higher levels; and hardware features that these higher levels may use to further improve the energy profile, closing the loop.

In fact, the historical trend of increasing performance closely tracks increases in energy efficiency, and this is encapsulated in an analogue of Moore's Law known as Koomey's Law [Koomey et al., 2011]. Moore stated that the number of components (latterly transistors) per chip doubled every two years; Koomey observed that computation per kilowatthour has followed a similarly exponential trend, doubling every 1.57 years. This trend is seen to hold throughout the history of computing, from the 1946 ENIAC to the most recent laptop and desktop machines, as shown in Figure 2.1. It has been said that "in 1978, a commercial flight between New York and Paris cost \$900 and took seven hours. If the principles of Moore's Law were applied to the airline industry, that flight would now cost about a penny and take less than one second" [Semiconductor Industry Association, 2005]. If Koomey's Law were applied analogously, the aircraft would now require less than 27 milligrams of fuel<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>This assumes a Boeing 777 at its maximum 150 MW power output and BP Avgas 80 fuel producing

Figure 2.1: Graph of computations per unit energy through history, in support of Koomey's Law. Reproduced from [Koomey et al., 2011].

Koomey's Law is an empirical observation about machines operating at peak performance 44.5 MJ/kg, considered independently from the reduction in flight time. Values taken from the BP Handbook of Products, 2000. http://www.bp.com/liveassets/bp\_internet/aviation/air\_bp/STAGING/local\_assets/downloads\_pdfs/a/air\_bp\_products\_handbook\_04004\_1.pdf

and consequently maximum power consumption. This suggests a neat partition of the existing work on hardware power-awareness into three parts: how such reductions have actually been achieved historically; to what extent this trend can be expected to continue into the future; and, how machines behave when operating at less-than-peak performance.

#### 2.2.1 Historical trends in hardware energy efficiency

Koomey's central collection of evidence is presented in Figure 2.1. The trend is clear to the naked eye, and is borne out by the line of best fit, with an  $\overline{R^2}$  value of 0.983.<sup>2</sup> Furthermore, since Koomey's observation is more recent, it is less vulnerable than Moore's Law to the criticism that it is a self-fulfilling prophecy, with the semiconductor industry adjusting its goals to meet the predictions. Therefore one can be reasonably confident of its robustness.

First, I address the historical explanation of Koomey's observation. There are several salient features of Figure 2.1. The leap seen in the early 1960s is explained by the transition from vacuum tube computing to the transistor, and progress through the 1970s can be attributed to the adoption and eventual dominance of CMOS, but since then progress has been steadier. The continued reductions can be understood by consideration of the three main ways in which energy is expended in a CMOS circuit: leakage, direct-path short-circuiting, and switching [Chandrakasan et al., 1995].

Leakage power is given by  $I_{leakage}V_{dd}$ , where  $I_{leakage}$  is the leakage current and  $V_{dd}$  the supply voltage. Traditionally neglected, leakage current is determined primarily by the CMOS fabrication technology, and has increasingly become a limitation in modern chip design since its reduction has been rather slower than that of other factors [Roy et al., 2003]. Only in the last decade has it been a significant explanatory factor in Koomey's Law, and its future is discussed below.

Direct-path short circuiting occurs when the N- and P-transistors of a CMOS unit are both activated at once, briefly connecting the supply to ground, and is given by  $P_{sc} = I_{sc}V_{dd}$ ; again  $I_{sc}$  is another hardware-determined constant, typically small in well-designed circuits.

<sup>&</sup>lt;sup>2</sup>The traditional coefficient of determination  $R^2$  can only increase as more variables are added, encouraging over-fitting.  $\overline{R^2}$ , or adjusted  $R^2$ , is a modification that penalises models for each additional variable they introduce. Koomey's model is bivariate so the adjustment is very slight.

Finally, the switching power is given by perhaps the most important equation in the field:

$$P_{switch} = \alpha C_L V_{dd}^2 f \tag{2.1}$$

where  $P_{switch}$  is the switching power expended,  $\alpha$  the switching activity,  $C_L$  the load capacitance, and f the clock frequency. Historically, switching power has been the dominant contributor to total power in CMOS, and prior work has targeted all four of these factors.

The switching activity  $0 \le \alpha \le 1$  is a constant denoting the fraction of clock cycles on which a transition occurs; CMOS consumes little power except during such a transition. Some techniques addressing  $\alpha$  occur at the compiler or ISA design level, addressed below, but other work targets hardware components directly. For example, the Bus-Invert method reduces the switching factor on an I/O bus by sending data inverted if this would produce fewer state switches; this inversion must itself be signalled, which may require an additional switching event. This trade-off is in fact a profitable one, as empirical results show that Bus-Invert produces a mean reduction of 25% in average power and 50% in peak power [Stan and Burleson, 1995]. Address buses are another attractive target, since they follow naturally long paths within and across the chip boundary, and carry fairly predictable data; for example, adjacent instructions are usually accessed sequentially, and therefore the instruction addresses tend to be consecutive or nearby integers. This suggests that use of a Gray code for instruction addresses might substantially reduce the expected number of transitions on the bus; indeed, in simulations a 58% reduction in  $\alpha$  was observed by use of this technique [Su et al., 1994b].

Load capacitance is a physical characteristic determined by the chip's wiring. Modern place-and-route tools seek (among many competing objectives) to minimise the total routed wire-length (RWL), and in particular to shorten long wires, which are the main culprits for high  $C_L$  values [Alpert et al., 2010]. One simple optimisation, typically performed as one of the last phases in place-and-route, is to insert additional repeaters into long wires off the critical path, transforming the path into multiple shorter wires [Alpert et al., 2010, p. 9]. Capacitance also scales up with increasing wire diameter, and of course wider wires are more difficult to route and (like repeaters) increase delay [Li et al., 2008]. More recently, the advent of three-dimensional integrated circuits has allowed substantial reductions in RWL. The extra dimension afforded by stacking multiple planes of transistors on top of one another, while presenting many new challenges in design and

manufacturing, is known to afford remarkable improvements in overall routing quality; in a typical set-up, it was shown to reduce the RWL by 28–51% and the length of the longest wire by 31–56% [Das et al., 2003].

The supply voltage is the most obvious target in Equation 2.1 due to its quadratic proportion to the switching power. Miniaturisation of MOSFETs, and the consequent shrinkage of CMOS, naturally allows lower supply voltages. Modern chip designs often permit the supply voltage to be varied dynamically, at the cost of some performance, but this discussion is left for Section 2.2.3.

Clock frequency is primarily determined by the delay of the critical path, although clock distribution imposes additional limitations. Frequency has become something of a controversial issue in the last twenty years, as frequency became a quotable marketing point for competing processor manufacturers. Some retailers promoted the notion that a higher number simply denoted better performance: the so-called "megahertz myth". While this is typically true for a given architecture, the comparison between architectures is a good deal more complex. While Intel's design focused on maximising clock speed, rival manufacturer AMD explored some of the techniques by which comparable performance can be achieved with a lower clock speed; in particular, superior superscalability and reduced memory latency [Matsui, 2006]. As discussed below, varying the clock frequency dynamically is also a well-explored field.

It is worth noting, finally, that the rate of improvement in battery technology has been very modest in comparison with the explosive trend of Koomey's Law, and that we therefore cannot rely on increasing the total energy available in order to lengthen time between charges. Also, modern batteries do not simply provide a fixed amount of energy; rather, their efficiency depends on the current drawn, which should ideally be low [Pedram and Wu, 1999]. In other words, doubling the current drawn by a device would reduce the battery life by substantially more than half. The variability of the current over time also has an impact, with more stable currents correlating with higher efficiency. This complication is rarely considered in the literature to date.

<sup>&</sup>lt;sup>3</sup>The origin of the term "megahertz myth" is unknown, but it had been adopted by the main-stream press by the early 2000s, for example http://www.guardian.co.uk/technology/2002/feb/28/onlinesupplement3.

#### 2.2.2 Future tends in hardware energy efficiency

Early transistor improvements were driven by so-called "Dennard scaling": ever-improving miniaturisation, with attendant improvements to supply voltage and clock speed [Dennard et al., 1974]. Pure Dennard scaling ended around the year 2000 with the 130 nm CMOS process; since then, other techniques have been required to keep pace with Moore's Law [Kuhn, 2009]. The International Technology Roadmap for Semiconductors<sup>4</sup> estimates that the current 22 nm CMOS production process will be reduced to 16 nm by 2013 and 11 nm by 2015. However, the majority of the future improvements will have to lie elsewhere.

Figure 2.2: Size comparison of a set of DEC Alpha cores from a heterogeneous multicore chip; each core is labelled with the single-core chip in which it originally appeared. Reproduced from [Kumar et al., 2003].

On the general rate of energy reduction, Koomey notes cheerfully that "we fully expect those improvements to continue in coming years" [Koomey et al., 2009]. Indeed, work is underway in many areas that are expected to yield further increases in computations per unit energy irrespective of miniaturisation. It is now widely agreed that the future of processing lies in more cores per chip—the so-called "chip multi-processor" (CMP) era—for the following reasons. As mentioned above, leakage current is now a significant factor of total power, and this can be controlled effectively by disabling individual cores. Another motivation is Pollack's Rule, which states that [Borkar, 2007]

performance

$$\propto \sqrt{\text{complexity}}$$

(2.2)

<sup>&</sup>lt;sup>4</sup>International Technology Roadmap for Semiconductors, 2011 Edition. http://www.itrs.net/Links/2011ITRS/Home2011.htm

Figure 2.3: Plot of power consumption against nominal parallel efficiency for various numbers of cores. Reproduced from [Li and Martínez, 2005].

and this mitigates against very large-area cores; therefore, it is better to invest the die area in a larger number of small-area cores. Options more flexible than completely disabling cores are available. One approach is use of heterogeneous multi-core architectures, with each core (or set of cores) placed at a different point in the power-performance trade-off; workloads are then assigned to an appropriate core dynamically. Tests show that, for an example set of DEC Alpha cores running the SPEC benchmarks, one can reduce total energy by an average of 39% while increasing execution time by just 3% [Kumar et al., 2003]. This particular configuration, in which various generations of the same processor family are loaded onto a single die, has multiple benefits: first, the die size is kept manageable, since the most recent generation is typically at least as large as the previous generations combined, as shown in Figure 2.2; second, the design and verification is more straightforward since the components already exist and are known to work. So we can expect to see more such designs in the future.

For applications that exhibit a high degree of internal parallelism (as opposed to the external parallelism of multiple applications running independently), multicore offers another

opportunity for energy saving. Define the nominal parallel efficiency  $\epsilon_n(N)$  of such an application when run on N processors as

$$\epsilon_n(N) = \frac{C_1}{NC_N} \tag{2.3}$$

where  $C_i$  is the number of cycles the program will consume when executed on i cores. (Note that in general,  $C_i > C_1$  for i > 1 because the program must perform extra work to communicate data and synchronise control flow between the threads.) Existing work shows that, for certain values of  $\epsilon_n(N)$ , a higher value of N may produce the same performance for less energy [Li and Martínez, 2005]. Tests were conducted on an example program running on a typical 65 nm processor; Figure 2.3 plots its power consumption against  $\epsilon_n(N)$  for a given performance requirement; the plot shows the power for N = 2, 4, 8, 16 and 32, normalised by the power required for the same program on a single core. Evidently, for  $\epsilon_n(N) \gtrsim 0.25$ , energy can be saved by deploying more cores, although the optimal number of cores bears a complex relationship with the value of  $\epsilon_n(N)$ . Even for values close to one (denoting perfect linear speedup), it is not necessarily optimal to enable as many cores as possible. This demonstrates that savings can also be made on homogeneous systems.

#### Theoretical limits to computational energy

One might reasonably ask how long Koomey's Law can continue to hold before some theoretical bound is reached. In fact, the question of computational energy bounds has been explored since well before the formulation of Koomey's Law, and wide-ranging arguments have been made on the subject for several decades [Bennett and Landauer, 1985]. In 1985, Richard Feynman estimated that the amount of electricity per unit computation might be reduced by a factor of 10<sup>11</sup> [Koomey et al., 2011]. Improvements since then amount to around 10<sup>5</sup>, and if Koomey's Law continues, such a limit would be reached sometime in the year 2041.

More fundamentally still, Landauer's Principle gives a thermodynamic lower bound on the amount of energy expended in changing a single bit of information in any physical representation [Landauer, 1961]. This Landauer limit is  $kT \ln 2$ , where k is the Boltzmann constant and T is the absolute temperature of the relevant physical object. Let us assume, very optimistically, that a computation required only a single bit change and occurred at the background temperature of the universe, the lowest temperature one can reach without expending further energy on cooling. In this case, T = 2.725 K and a computation could be performed in  $7.2 \times 10^{-33}$  kilowatt-hours. This limiting value is the efficiency predicted by Koomey's Law for the year 2098.

In fact, one can go further still, by application of reversible computing, a mode of computing in which information is not destroyed and therefore Landauer's entropic argument can be sidestepped [Bennett, 1973]. Although it is not possible to build a computer that preserves information perfectly in its state transitions, there is, in our current understanding of physics, no limit to how closely one might approach this limit. So, at least in theory, we may see Koomey's Law upheld for some time yet. Neatly enough, the promising field of quantum computing, a form of reversible computing, also originates with Feynman [Feynman, 1982].

#### 2.2.3 Energy characteristics at sub-peak performance

Koomey's Law addresses the efficiency of a computer running at peak performance. However, machines often allow a much wider range of dynamic performance-power trade-offs. This is discussed in greater detail in Chapter 3, but some points are of general relevance. Many devices now provide low-power idle states, in which they are not usable but must instead be transitioned back to the active state. (Of course the transition itself also requires some time and energy.) Modern CPUs are among the most dynamic of these. For much of their history, CPUs simply executed no-ops when they had no useful work to perform. This was the basis for many of the early "crowdsourcing" computational projects, such as the Great Internet Mersenne Prime Search<sup>5</sup>, SETI@home<sup>6</sup>, and distributed.net<sup>7</sup>, since these cycles would otherwise have been wasted. More recent designs allow CPUs to transition between various idle states, among other power-saving measures, such as dynamic voltage-frequency switching.

<sup>&</sup>lt;sup>5</sup>http://www.mersenne.org

<sup>6</sup>http://setiathome.berkeley.edu

<sup>&</sup>lt;sup>7</sup>http://www.distributed.net

#### Dynamic voltage-frequency scaling

Equation 2.1 demonstrates the relationship between supply voltage and switching power, the latter of which has until recently accounted for the majority of the processor's power consumption. Many modern designs allow dynamic voltage scaling (DVS), in which the operating voltage of a processor can be adjusted on-the-fly so as to trade performance for power. However, the circuit delay also varies with the operational voltage, according to the equation

$$t \propto \frac{V_{DD}}{(V_{DD} - V_T)^{\alpha}} \tag{2.4}$$

where  $V_{DD}$  is the operational voltage,  $V_T$  the threshold voltage, and  $\alpha$  the so-called velocity saturation index [Taur and Ning, 1998, pp. 269–271]. (The latter two are parameters of the CMOS technology.) Since the maximum clock frequency is in turn limited by the circuit delay, one typically scales frequency and voltage in concert: dynamic voltage-frequency scaling (DVFS). Since the power is reduced quadratically while the performance degrades only linearly, there is a net linear saving in total energy. Therefore, at least in the region for which the switching power is the dominant contributor to total power, we can expect approximately linear energy savings as the time allowed for computation increases. Of course, DVFS is not without its drawbacks. Changing the supply voltage often requires a processor stall, incurring a time delay of 10–100  $\mu s$  [Von Kaenel et al., 1990]. The energy savings will therefore be obliterated by the overhead of changing voltages unless the system can make accurate predictions about the future performance requirements on the order of milliseconds. Recent work has explored techniques for reducing this delay to the nanosecond range, but there are many complications and this is not yet widely deployed in practice [Kim et al., 2008]. A further disadvantage is that the thermal variation induced by varying the voltage may cause microscopic damage to the device and ultimately reduce its lifespan [Lee, 2000]. Notwithstanding these limitations, later chapters discuss the many and varied ways in which DVFS can be leveraged to save energy.

#### Near-threshold computing

An exciting development at the extremes of the power-performance trade-off is nearthreshold computing (NTC). The model embodied by Equation 2.4 does not apply to operating voltages below the threshold voltage, in which region the behaviour of the tran-

Figure 2.4: Transistor behaviour in sub-, near-, and super-threshold operating voltage regions. Reproduced from [Dreslinski et al., 2010].

sistor is slower, more complex, and vastly more erratic; see Figure 2.4. Sub-threshold computing, although certainly low-power, has therefore never found widespread applicability, while traditional computing has reserved itself to operating voltages safely in excess of the threshold. However, NTC operates in the region at which  $V_{DD} \approx V_T$ , which offers significant energy benefits and only a subset of the difficulties faced in the sub-threshold region: in comparison to normal super-threshold operation, the circuit experiences an order of magnitude reduction in performance; five orders of magnitude increase in memory failures; a fivefold increase in inter-device variability with regards to performance; and doubled increase in sensitivity to operating temperature [Dreslinski et al., 2010]. Recent work has made significant developments in managing the impact of these limitations; in particular, the introduction of highly parallel architectures to ameliorate the loss of performance and device stability, and the use of transistors and SRAM blocks designed for sub-threshold reliability. Further experiments have justified other enhancements, such as the use of dual operating voltages, both in the near-threshold range, to offset a significant fraction of the performance penalty [Kakoee et al., 2010]. On the theoretical side, recent circuit models describe near-threshold behaviour much more precisely than was possible with earlier approximations [Harris et al., 2010]. Superior understanding of the underlying behavioural properties will inevitably lead to improvements in the practicality of NTC, and practical NTC-purposed cores have now been constructed; for example, the Phoenix processor, which operates in the near-threshold region (among many other optimisations), requires only 2.8 pJ per cycle when executing at full speed [Seok et al., 2008]. Including its on-die battery, the Phoenix occupies less than one cubic millimetre and, in a sensor network (its intended environment) can run on this battery for over a year. All of this suggests that NTC may soon find real-world deployment in particularly energy-sensitive devices.

### 2.3 Energy-aware operating systems

The operating system makes multiple important contributions to the overall picture of an energy-aware system. First, while the hardware can address some power concerns directly, it can also provide facilities for higher layers to exploit; for example, DVS simply allows performance to be traded for power, and it is the task of the operating system to set the proportions of this trade-off in order to achieve actual savings. Making these decisions is the motivating problem for the area of energy-aware scheduling, and a full description of this work is left for Chapter 4 where it is more pertinent. Such decisions may theoretically be made in hardware, but in general there are typically some features that are better handled by a higher level.

A second factor in the operating system's contribution to energy-awareness is that the kernel is itself a process that must be executed and therefore requires energy. In the future we may see operating systems optimised for energy as any other piece of software might be. However, the operating system presents some unique opportunities. One particular example is the recent development of a "tickless kernel", detailed in Section 3.5.1, which dispenses with the traditional polling-based implementation of thread preemption. Similar re-examination of fundamental operating system constructs has been considered in other operating systems, such as OpenSolaris' Tesla Project.<sup>8</sup>

<sup>&</sup>lt;sup>8</sup>The Tesla Project is no longer active, although it did make some lasting contributions such as the PowerTOP power monitoring tool, http://hub.opensolaris.org/bin/view/Community+Group+pm/powertop.

### 2.4 Energy-aware protocols

Computing is a world of protocols, but in reference to energy-awareness, one usually means networking protocols; there has been little research on energy usage for internal protocols such as APIs at the operating-system level. Network protocol design is an important field: 1997 figures suggest that around 18% of a laptop's power is expended in the wireless card, and, while there is a dearth of comparable measurements for modern hardware, the current figure is perhaps higher, since the hardware improvements of Section 2.2 do not substantially impact the cost of radio broadcast itself [Stemm and Katz, 1997]. Within networking protocols, one can distinguish two independent strands of work: on the one hand, energy concerns in communication protocols, which typically means modifying the existing protocol stack to improve energy efficiency; on the other hand, creation of new protocols intended for energy management per se. This section describes each in turn.

#### 2.4.1 Energy-aware data protocols

Wireless networks are typically taxonomised into *infrastructure* networks, in which wireless devices communicate with a wired base station in a single hop, and *ad hoc* networks, in which multiple mobile devices communicate amongst each other, and may be completely isolated from any non-mobile power source. Clearly these pose quite different challenges from an energy perspective. When a fixed device transmits to a mobile device, it is worth expending a substantial amount of power in the transmitter to save power in the receiver, and similarly when the mobile device is to transmit, *mutatis mutandis*. On the other hand, when communication is mobile-to-mobile, interacting concerns of efficiency and fairness arise. This summary will mainly consider infrastructure networks since this is the underlying assumption of later chapters. The Open Systems Interconnection (OSI) model is the standard characterisation of the layers of the network stack, so this summary categorises the relevant work according to these layers [Zimmermann, 1980].

The challenges of the physical layer are well-known, such as hidden and exposed terminals and frequency-band collisions. No more will be said about these directly, although the tight layer integration requires close consideration of the physical layer in what follows.

At the data link layer, the focus is on reducing the overhead of retransmissions. Two tech-

niques dominate: forward error correction (FEC) and automatic repeat request (ARQ). FEC extends packets with redundant information such that, up to some maximum number of bit errors, the original information can be recovered even if some of the data is damaged in transit. Clearly this redundancy is a data overhead in itself, and the optimal trade-off depends on the expected fidelity of the connection. Modern "turbo codes" can very closely approach the Shannon limit, the theoretical maximum for data transmission over a noisy channel [Berrou et al., 1993]. Resultant work also exists on decoding these turbo codes in an energy-efficient manner [Leung et al., 1999]. In ARQ, intermediate nodes in the network detect dropped packets without explicit notification from the end-point and request retransmission immediately, thereby reducing latency and eliminating the need for some metadata packets from the receiver. ARQ may hook directly into the physical layer, suggesting the optimal transmission power, which must balance the obvious trade-off between energy required per packet and the probability of a retransmission being required; existing work suggests that this may well be a profitable approach, although empirical measurements are hard to obtain [Arulselvan and Berry, 2002]. There is a similar trade-off with packet size versus retransmission probability, which has been analysed in an energyaware context [Modiano, 1999]. The optimal packet size is relatively straightforward to derive given an accurate model of the channel, and surprisingly an adequate model can be learnt relatively quickly, in perhaps 10<sup>4</sup> bits of transmission. These results illustrate the general principle that close integration of layers in the network stack is often necessary for optimisation, and this is no less true for energy than for other performance metrics.

Further illustrating the principle, system designers frequently coalesce the network and transport layers in energy-aware devices, following observations on the substantial energy benefits this can bring [Raisinghani and Iyer, 2004]. In almost all cases this means "TCP/IP"; the Transmission Control Protocol<sup>9</sup> at the transport layer, above the Internet Protocol<sup>10</sup> at the network layer. Early results indicated that none of the basic variants of TCP performed particularly satisfactorily from an energy standpoint, with TCP Tahoe being generally the least bad among them [Tsaoussidis et al., 2000]. This motivated the development of more suitable TCP variants. Energy-efficient TCP (E<sup>2</sup>TCP) was proposed

<sup>&</sup>lt;sup>9</sup>See RFC 793, Transmission Control Protocol: Darpa Internet Program: Protocol Specification, http://www.ietf.org/rfc/rfc793.txt.

<sup>&</sup>lt;sup>10</sup>See RFC 791, Internal Protocol: Darpa Internet Program: Protocol Specification, http://tools.ietf.org/html/rfc791.

soon afterwards, with several refinements [Donckers et al., 2002]. To reduce data overhead, E<sup>2</sup>TCP uses header compression, and supports selective acknowledgements to minimise retransmitted data. Furthermore, while traditional TCP attributes all dropped packets to congestion and consequently backs off rapidly, E<sup>2</sup>TCP recognises the distinct problem of burst errors (from, say, wireless interference) as essentially transient, and handles this situation differently. In tests, E<sup>2</sup>TCP was shown to have slightly superior data efficiency but vastly superior time efficiency, allowing the wireless card to be placed into a lowpower state earlier and to remain so for longer. In tests, the two protocols were used to support real-time streaming of the kind explored in Chapter 5. The energy overhead of each protocol was then calculated by reference to the theoretical minimum energy for transmission. When the channel entered a "bad" state (indicating high probability of bit errors) for two seconds for every twenty seconds of clean transmission, E<sup>2</sup>TCP incurred 2\% energy overhead to Tahoe's 5\%; with more frequent cycling, such as 0.1 seconds of bad transmission for every second of clear transmission, E<sup>2</sup>TCP required 6% overhead and Tahoe 10%. This demonstrates not only the amount of energy improvement available for traditional TCP variants but also the headroom for further improvement on E<sup>2</sup>TCP.

Higher layers in the OSI model (session, presentation, and application) are addressed in Section 2.5.

#### 2.4.2 Energy management protocols

A newer area is the development of protocols to manage and coordinate power directly. This area emerged in ad hoc wireless networks, where it is a fundamental concern, but now has applications more relevant to this document, such as web server management. For example, consider the following: a modern web service typically adopts a multi-tiered architecture, such as a Web interface to business logic with a database back-end. Each tier is run on a separate machine or set of machines. Therefore, depending on the demands of each tier, the performance of each one may be traded off differently for energy, subject to (for example) a latency constraint on the whole stack. Previous work has developed a protocol based on the "Weighted Feedback DVS" algorithm, by which the tiers may communicate to coordinate the performance-power points selected [Horvath et al., 2007]. In tests, a Linux implementation of the protocol was shown to reduce energy consumption

by up to 30% compared to the native power-saving mode. Further developments extend the control loop to include virtualised servers, in which it is not so straightforward to power down or scale back hardware components [Wang et al., 2008]. Empirical evidence in this case suggests that such an approach can reduce average power from 240 W to around 205 W for an example system, while still maintaining adequate average response time. Future work may explore the coordination of other hardware and software configuration choices.

## 2.5 Energy-aware software

Energy efficiency at the higher layers of the OSI stack—the session, presentation, and application layers—is naturally a highly domain-specific problem and therefore the focus has been on providing developers with tools to profile their own implementations and improve performance directly. An early contribution to this area was PowerScope [Flinn and Satyanarayanan, 1999]. PowerScope is analogous to a traditional profiler, but measures the energy rather than the time and space demanded by each point in the call stack; then, as with CPU or memory profiling, the programmer can direct his or her efforts towards improving the most energy-intensive parts of the application. In an example given by the authors, such analysis and improvement allowed a 46% reduction in the energy consumption of a certain video decoding program. A measure of the success of this work is that most mobile device manufacturers now produce their own tools to measure the power usage of various hardware components, such as Nokia's Energy Profiler<sup>11</sup>.

Another general approach targeting the software layer is energy-aware compilation. Typical compiler techniques are manipulations intended to improve the energy efficiency of the program with little or no loss in performance, and therefore they form part of the general literature of optimising compilers, albeit with a novel metric of optimisation. One approach is based on profile-driven compilation, in which measurements of the program's behaviour are taken on representative input data during compilation and used to optimise various code features for that data. For example, one example system looks for regions that are mostly memory-bound and, using DVFS, slows the CPU in these regions [Hsu and

<sup>11</sup>http://www.developer.nokia.com/Resources/Tools\_and\_downloads/Other/Nokia\_Energy\_

Profiler/

Kremer, 2003]. This system is carefully designed for practical use, allowing for non-CPU static power, transition time and energy penalties, battery discharge characteristics, and other details. Consequently, when measured on a real laptop, it produces energy reductions for various benchmarks averaging 11%, reaching 28% in the most favourable cases although with essentially no benefit in the hardest cases; performance is only reduced by a few per cent. An alternative approach, requiring more programmer intervention, is to insert "checkpoints" at the beginning of every basic block, and require annotations describing the maximum time that execution may take to make all possible transitions between these checkpoints; in other words, to ascribe maximum time values to every arc in the control flow graph [Azevedo et al., 2002]. A run-time system, again using DVFS, adjusts the performance within each block to meet these values in a best-effort fashion; it is shown empirically that a good heuristic for estimating the frequencies is the minimum time between the checkpoints. This is shown to reduce the energy of the processor by up to 82%, although whole-system values are not provided.

Register allocation has been another popular mechanism to address. Traditional metrics, such as minimising register spillage, certainly correlate positively with energy efficiency, but more can be done. For example, successive reads of a register allocated to the same variable are not relevant to traditional liveness analysis, which defines the lifetime of a variable as spanning from its first write to its final read; however, each of these reads incurs an energy cost, which must be factored in to the total analysis. At the register allocation phase, one can also employ a detailed model of register and main-memory energy consumption, including the benefits of locality of reference in main memory. One implementation of this technique was able to reduce the energy consumption of the memory hierarchy by 87–90%, under the assumption that a memory access requires about thirty times as much power as a register access [Zhang et al., 2002]. However, this was only evaluated against small example programs, although the compilation technique is efficient enough computationally to attack larger examples.

There are numerous other strands of work in this area. For example, one might aim to reduce register spills (even with a large L1 cache) or to reduce the activity factor [Tiwari et al., 1994, Su et al., 1994a]. As seen in Equation 2.1, the leakage energy is another relevant factor, and an increasingly significant one in modern architectures. Leakage can be reduced by disabling unused functional units within the CPU. A compiler implementa-

tion has been presented that inserts explicit enable/disable instructions into basic blocks according to which units are required, subject to the competing consideration of the units' start-up latencies, and was able to reduce average leakage by 45.4% over various examples from the MediaBench and Spec benchmark suites [Zhang et al., 2003]. This is particularly beneficial on complex architectures, which provide various subunits such as a floating-point co-processor, which, while vital for some applications, are largely irrelevant for others, and can be disabled completely.

This document will not consider compilation techniques much further, but rather assumes that the software is provided as-is in binary form, and primarily targets techniques that could be provided by the operating system rather than the application programmer. This is motivated by the argument that software engineers are already overwhelmed with competing considerations, and would be unlikely to extend their development cycles in pursuit of reducing an energy bill incurred, for the most part, by someone else (their customers). This is discussed further in Chapter 3.

## 2.6 Summary of related work

Evidently, a vast range of work has been undertaken on the energy problem, and there is much more to come. At the hardware level, Koomey's Law continues to drive up the number of computations per unit energy, and to provide new features for exploitation by higher layers. In the operating system, the multicore era creates highly complex scheduling problems which must still be solved quickly if they are to remain essentially transparent to the user. Energy-aware protocols impact more and more devices as Internet connectivity becomes expected on ever-smaller and more portable devices. And software engineers, already challenged by the demands of highly parallel programming, now face a second front from the demands for energy-efficient operation at every level of the execution stack. Furthermore, beyond the four-piece taxonomy used above lie many interactions between these areas; for example, the shift to a large number of simple cores may ultimately reduce the necessity of kernel quiescence, since waking one core among thousands is a much less significant event than waking a single monolithic processor. To give another example, the low voltage of near-threshold computing offsets some of the difficulties of power dissipation in three-dimensional circuit integration. And there are further issues external to the

taxonomy given here; for example, power generation, while certainly outside the scope of computer science, impacts the way in which power can be used within a computing context. However, these details are rather specific and are left for the relevant chapters.

This document does not, of course, attempt to tackle all of these problems at once, but rather argues that to improve on certain details it is valuable to understand the full picture. In my own contributions, I generally take the hardware as a given, representing an immutable background above which other optimisations take place. The protocol stack is significant firstly because it suggests the sort of devices that will be expected to be networked in the future (which is to say: all of them) and secondly because it gives an idea of the performance and characteristics of networking on those devices; the latter is of particular significance in Chapter 5. I also generally consider the software layer to be out of reach, because the diversity of software energy challenges is too great to describe completely general methods for them; also, as discussed, the pressures on modern software engineers are already substantial, and therefore techniques making further demands on them (such as annotation) are unlikely to gain traction in industry. Instead, my focus lies primarily in the middle: in deciding how the hardware's features may be best used to improve the energy of the system, which decisions the operating system can make transparently, and, contrariwise, which features the system might expose directly to the software layer. This is the topic of the succeeding chapters.

# Chapter 3

# Towards energy-efficient computing

The majority opinion in both corporate and academic circles is that the "energy problem" is now real and pressing; humanity's primary sources of energy are running out while the demand for energy in commercial and domestic environments is increasing, and the side-effects of energy use have important environmental considerations on a global scale. The emission of greenhouse gases such as  $CO_2$ , now seen by most climatologists to be linked to global warming, is only one issue.

World leaders and pre-eminent scientists are perhaps most focused on a strategic solution: the need to develop new sources of clean and renewable energy if humanity is to ultimately overcome its energy problem. Lord Rees, president of the Royal Society, emphasised its urgency in an annual address delivered in 2008, saying<sup>1</sup>

"At this year's G8 summit, in Japan, the member nations formally espoused the goal of reducing global CO<sub>2</sub> emissions, by 2050, to half the 1990 level. ... Realistically, there is no chance of reaching this target, nor of achieving real energy security, without new technologies."

However, the realisation of new sources of sustainable energy is expected to be at least three decades away. Steve Chu, director of the Lawrence Berkeley National Laboratory prior to his appointment as United States' Secretary of Energy, placed this in context, saying<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>Quoted from Lord Martin Rees of Ludlow's Anniversary Address to the Royal Society, 2008, http://royalsociety.org/uploadedFiles/Royal\_Society\_Content/about-us/history/Anniversary\_Address\_2008.pdf.

<sup>&</sup>lt;sup>2</sup>Quoted from The energy problem and Lawrence Berkeley National Laboratory, talk given to the

"A dual strategy is needed to solve the energy problem:

- 1. Maximise energy efficiency and decrease energy use.

- 2. Develop new sources of clean energy.

Number 1 will remain the lowest-hanging fruit for the next few decades."

# 3.1 Energy in the computing space

Energy is an inescapable problem in computing. Even if future improvements in power efficiency adhere to Koomey's Law and increase the available energy for computation beyond our current imagination, as discussed in Section 2.2.2, there are fundamental limits to what can be computed with a given amount of energy. More currently, power distribution and cooling is already a significant challenge in the data centre, and future hardware refinements are only likely to exacerbate this [Fan et al., 2007]. Put simply, the conclusion of thermodynamics is that energy is the ultimate limited resource in the universe.

In August 2007, the Environmental Protection Agency (EPA) issued a report to the U.S. Congress on the energy efficiency of servers and data centres [U.S. Environmental Protection Agency, 2010]. Some key findings from the report include:

- Servers and data centres consumed 61 billion kilowatt-hours of energy in 2006.

- This was 1.5% of total U.S. electricity consumption that year, amounting to \$4.5 billion in electricity costs, which is equivalent to 5.8 million average U.S. households.

- Electricity use in this sector doubled between 2000 and 2006, a trend that is expected to continue.

- Infrastructure systems necessary to support the operation of IT equipment (such as power delivery and cooling systems) also consumed a significant amount of energy, comprising 50% of annual IT electricity use.

Figure 3.1: Energy usage breakdown by equipment type in United States, from 2000 to 2006.

Excerpts from the EPA report are shown in Figure 3.1 and Table 3.1. There are two particularly notable points in the data. The first is that as much energy is being consumed by site infrastructure as by the computing equipment itself. This infrastructure primarily represents HVAC (heating, ventilation, and air-conditioning) equipment, as well as that used to convert and transmit power and to maintain its continuity; this includes transformers and in-building power-switching and transmission equipment, as well as power-conditioning and sustaining equipment such as uninterruptible power supplies. This factor is of great consequence because it suggests that energy savings at the computing level would have an attendant impact on HVAC as well.

Within the computing equipment itself, however, is the second point of interest. Of the five types of IT equipment studied, volume servers alone were responsible for the majority (68%) of the electricity used. Assuming that the 17% combined annual growth rate of volume servers continues, this suggests that they are the prime targets for energy reduction in the server space. The 20% growth rate of storage devices shown here—a rate that more recent data suggests is accelerating—indicates another significant trend.

If the exponential growth of data-centre computing equipment revealed by this study

| Component           | Energy (2000) | % Total | Energy (2006) | % Total | CAGR |

|---------------------|---------------|---------|---------------|---------|------|

| Site infrastructure | 14.1          | 50%     | 30.7          | 50%     | 14%  |

| Network equipment   | 1.4           | 5%      | 3.0           | 5%      | 14%  |

| Storage             | 1.1           | 4%      | 3.2           | 5%      | 20%  |

| High-end servers    | 1.1           | 4%      | 3.2           | 5%      | 20%  |

| Mid-range servers   | 2.5           | 9%      | 2.2           | 4%      | -2%  |

| Volume servers      | 8.0           | 29%     | 20.9          | 34%     | 17%  |

| Total               | 28.2          | _       | 61.4          | _       | 14%  |

Table 3.1: Energy usage breakdown for computing equipment in the United States. Energy figures are in billions of kWh.

continues, the demand for electricity in data centres seen in 2006 is expected to have roughly doubled by the time of writing. This poses challenges beyond the obvious economic ones. For example, peak instantaneous demand is expected to have risen from 7 gigawatts in 2006 to 12 gigawatts in 2011, and ten new base-level power plants would be needed to meet such a demand.

Physical limitations on power availability are already a constraint for data centres in some areas; a managing director of IT for Morgan Stanley observed in 2009 that the company is now physically unable to source the power needed for a new data centre in Manhattan. The seriousness of the situation is demonstrated by the zeal with which corporations such as eBay, Google, Amazon, Microsoft, and Yahoo have pursued suitable locations in which the data centres required to run their contemporary Web applications and services can be constructed [Katz, 2009]. A number of these companies have already negotiated with certain states in the U.S., as well as internationally, to construct these facilities along with the power plants necessary to supply them. In 2006, Google triggered a "multibillion-dollar face-off" after situating a new facility along the Columbia River in Washington [Markoff and Hansell, 2006]. The combined benefits of lower land cost, lower external ambient temperature, and the availability of running water for cooling and hydroelectric power generation are intended to provide relief for Google's acute energy-availability and energy-cost problems.

The U.S. Energy Information Administration showed in their report to Congress<sup>3</sup> that in

<sup>&</sup>lt;sup>3</sup>Energy Information Administration Residential Energy Consumption Surveys 2001, http://www.

2001, PCs and printers in American households consumed 23.1 terawatt-hours of energy; the figures were similar in 2006 [Roth and McKenney, 2007]. This suggests that the amount of energy consumed by mobile and desktop computing equipment is of roughly the same magnitude as that used by servers in data centres, although there is no correspondingly comprehensive and authoritative current study to refer to. The EPA data presented here provides some detailed perspective on where the energy goes in the important and growing server segment of the computing landscape. Also, some groundwork has already been laid in the mobile and desktop computing space as a result of the earlier focus of the EPA's EnergyStar program on consumer electronics, which includes computer systems.

# 3.2 Modern power management