# High-K materials and Metal Gates for CMOS applications

John Robertson

Engineering Department, Cambridge University, Cambridge CB2 1PZ, UK

Robert M. Wallace

Materials Science and Engineering, University of Texas at Dallas, Richardson, TX 75080, USA

#### **Abstract**

The scaling of complementary metal oxide semiconductor (CMOS) transistors has led to the silicon dioxide layer used as a gate dielectric becoming so thin that the gate leakage current becomes too large. This led to the replacement of SiO<sub>2</sub> by a physically thicker layer of a higher dielectric constant or 'high-K' oxide such as hafnium oxide. Intensive research was carried out to develop these oxides into high quality electronic materials. In addition, the incorporation of Ge in the CMOS transistor structure has been employed to enable higher carrier mobility and performance. This review covers both scientific and technological issues related to the high-K gate stack - the choice of oxides, their deposition, their structural and metallurgical behaviour, atomic diffusion, interface structure, their electronic structure, band offsets, electronic defects, charge trapping and conduction mechanisms, reliability, mobility degradation and oxygen scavenging to achieve the thinnest oxide thicknesses. The high K oxides were implemented in conjunction with a replacement of polcryslliane Si gate electrodes with metal gates. The strong metallurgical interactions between the gate electrodes and the HfO2 which resulted an unstable gate threshold voltage resulted in the use of the lower temperature 'gate last' process flow, in addition to the standard 'gate first' approach. Work function control by metal gate electrodes and by oxide dipole layers is discussed. The problems associated with high K oxides on Ge channels are also discussed.

ALD atomic layer deposition

CB conduction band

CBO conduction band offset

CMOS complimentary metal oxide semiconductor

CNL charge neutrality level

CV capacitance voltage

CVD chemical vapour deposition

DB dangling bond

DOS density of states

EA electron affinity

ECT equivalent capacitance thickness

EOT equivalent oxide thickness

ESR electron spin resonance

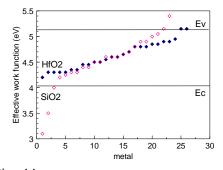

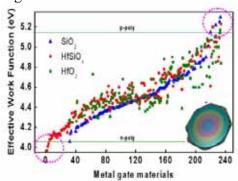

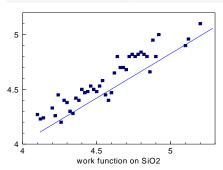

EWF effective work function

FET field effect transistor

GGA generalised gradient approximation

LDA local density approximation

medium energy ion scattering MEIS

MIGS metal induced gap states

MOCVD metla organic chemical vapour deposition

MOS metal oxide semiconductor

MOSFET metal oxide semiconductor field effect transistor

MO<sub>x</sub> arbitrary metal oxide

NMOS n-type MOS

PMOS p-type MOS

RCS remote Coulombic scattering

RPS remote phonon scattering

SBH Schottky barrier height

TAT trap assisted tunnelling

T<sub>inv</sub> inversion thickness

Vt threshold voltage (of FET)

Vfb flat band voltage

VB valence band

VBO valence band offset

WF work function

#### 1 Introduction

The incorporation of high-K dielectrics with metal gates into a manufacturable, high volume transistor process is the result of tremendous ingenuity and effort by many scientists and engineers [1]. We review that progress in this article, with an emphasis on the key developments in the high-K/metal gate stack process. We also summarize recent results on incorporation of Ge in the transistor, which appears to provide a viable route to higher performance technology.

It is more than a decade since high-K gate dielectric research for Si-based transistor technology was first reviewed [2,3]. We begin this review with a brief summary of the scaling issues that drove the incorporation of high-K dielectrics and metal gate technologies. We then discuss the materials chemistry of the high-K dielectrics employed in transistor fabrication. This is followed by a review of the current understanding of the high-K/semiconductor interfacial bonding. Defects, which play an important role in high-K dielectrics, are then discussed. Of course, the electrical performance of the transistor is paramount, and we review the recent developments, including work function control for the transistor gate stack.

### 1.1 Scaling and gate capacitance

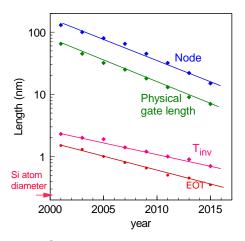

The complementary metal oxide semiconductor (CMOS) field effect transistor (FET) made from silicon is the most important electronic device. This has arisen because of its low power consumption and its continuing performance improvement over forty years following Moore's Law of scaling. This "law" notes that the number of devices on an integrated circuit increases exponentially, doubling every 2-3 years. The minimum feature size in a transistor decreases exponentially each year (Fig. 1).

Until recently the materials and elements used in CMOS technology were very few – Si, O, P, Al, B, H and N. Now the situation has reversed. New materials are being introduced in many areas, from Cu instead of Al for interconnects, low dielectric constant materials such as SiOCH for inter-metal dielectrics, silicides as contact metals, and diffusion barrier materials such as TiN.

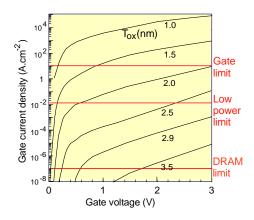

The  $SiO_2$  layer used as the gate dielectric is now so thin ( $\sim$ 1.2 nm) that the gate leakage current due to direct tunnelling of electrons through the  $SiO_2$  becomes too high, exceeding 1 A/cm<sup>2</sup> at 1 V (Fig. 2). This means that the static power dissipation would be unacceptable [2-13]. In addition it becomes increasingly difficult to make such thin films, and they become increasingly unreliable. Thus,  $SiO_2$  had to be replaced.

An FET is a capacitance-operated device, where the FET source-drain current depends on the gate capacitance, which is most simply expressed as

$$C = \frac{\varepsilon_0 KA}{t} \tag{1}$$

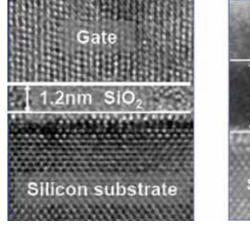

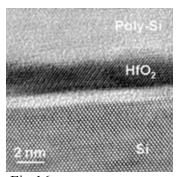

where  $\varepsilon_0$  is the permittivity of free space, K is the relative dielectric constant, A is the area and t is the oxide thickness. Tunnelling currents decrease exponentially with increasing distance. Hence, the solution to the tunnelling problem is to replace  $SiO_2$  with a physically thicker layer of new material of higher K, as shown in transmission electron microscope images Fig 3. This will keep the same capacitance, but decrease the tunnelling current. These new gate oxides are called 'high K oxides'.

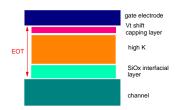

For a device designer, as the precise material does not matter, it is convenient to define an electrical thickness of a new oxide in terms of its equivalent silicon dioxide thickness or 'equivalent oxide thickness' (EOT)

$$t_{ox} = EOT = (3.9/K) t_{HiK}$$

(2)

Here, 3.9 is the static dielectric constant of SiO<sub>2</sub>. The objective is to develop high K oxides to allow scaling to continue to very low EOT values.

The gate leakage problem has been apparent since the late 1990's [14], but the criteria for choosing the oxide were unclear. In about 2001, the choice of oxide had narrowed to  $HfO_2$ , but the problems of making  $HfO_2$  into a successful electronic material were great. Nevertheless, the increasing importance the low-power electronics in cell-phones, lap-tops, and portable electronics mean that the problem had to be solved. Low standby power CMOS requires a leakage current of below  $1.5 \times 10^{-2}$  A/cm<sup>2</sup> rather than just 1 A/cm<sup>2</sup>. There were many difficulties in manufacturing high K oxides /metal-gate stacks but these were gradually overcome. Intel now manufactures the chips with second generation of high K/metal K stacks [1,15] and have now implemented high K for FINFET structures as well.

The second critical issue was the realisation that metallurgical problems would limit the introduction of the high K/metal gate stack in an exact replica of the SiO<sub>2</sub> gate process (gate first) [16], and that instead a 'replacement gate', 'dummy gate', or 'gate last' process [15] would need to be used, to limit the exposure of high K/ metal gate interface to high temperatures.

In a key early paper, Gusev et al [17] identified four key problems for successful introduction of high K oxides -

- (1) be able to continue scaling to lower EOTs,

- (2) stop the gate threshold instabilities caused by the high defect densities,

- (3) limit the loss of carrier mobility in the Si channel when using high K oxides,

- (4) control the gate threshold voltage, which resulted in the need for metal gates.

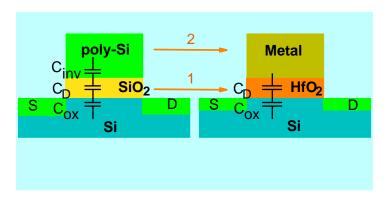

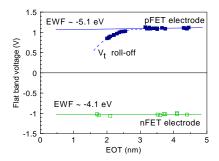

# 1.2 Metal gates and Effective Capacitance Thickness (ECT)

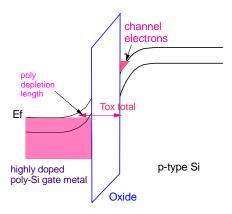

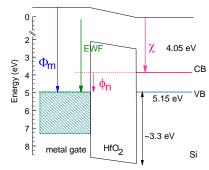

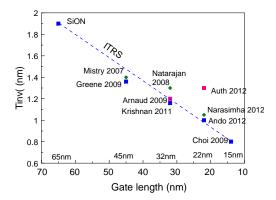

Viewing the Si – gate stack band diagram of a MOSFET (Fig. 4), the gate capacitance is the series combination of three terms, the oxide capacitance, the depletion capacitance of the gate electrode, and the capacitance of the Si channel carriers. These three capacitances add as (Fig 5)

$$1/C = 1/C_{ox} + 1/C_{D} + 1/C_{Si}$$

(3)

As C varies as 1/t, capacitors in series combine as a sum of effective distances. Thus we can define an 'effective capacitance thickness' ECT of the whole gate stack as

$$ECT = t_{inv} = EOT + t_{gate} + t_{Si}$$

(4)

ECT is also known as the inversion thickness  $t_{inv}$ .

The channel capacitance  $C_{Si}$  arises because the 2-dimensional electron gas of carriers in the channel cannot lie infinitely close to its surface, but delocalises a few Angstroms into the Si. This capacitance contribution is intrinsic and cannot easily be changed. High-k dielectric materials are often first evaluated using a MOS capacitor structure, and sunsequently utilizing a transistor structure measuring the substrate (depletion) and source/drain (inversion) capacitance ("Split CV") independently [18,19].

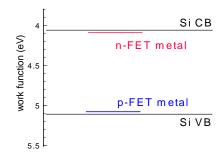

Previously, the gate electrode was made out of degenerately doped polycrystalline silicon (poly-Si). This is stable at high temperatures and compatible with  $SiO_2$ . Poly-Si is a reasonable metal, but it is not a good enough metal as its relatively low carrier density gives a depletion depth of a few Å. In contrast, a good metal has a much higher carrier density and a depletion depth of only 0.5 Å. This depletion effect is removed by replacing poly-Si with a normal metal. The effect on ECT of the replacement of  $SiO_2$  by a high K oxide and poly-Si gate electrode by a metal is shown schematically in Fig. 5. As noted below, the work function of the metal is a critical property to enable proper NMOS or PMOS FET operation.

The ECT is the only thickness that can be measured directly, by capacitance-voltage (CV) methods. On the other hand, EOT can only be estimated by, for example, electron microscopy measurements of oxide thickness, or by back calculating from ECT. EOT is useful, but is not a direct electrical parameter.

A metal gate material must also be carefully chosen. It is chosen primarily for its work function and its thermal robustness, as discussed in detail in section 6.

# 2 Choice of High K oxide

Silicon dioxide is the main reason that microelectronics uses Si technology and not another semiconductor. As a semiconductor, Si has average performance, but in most respects  $SiO_2$  is an excellent insulator.  $SiO_2$  has the key advantage that it can be made from Si simply by thermal oxidation, whereas every other semiconductor (Ge, GaAs, GaN, SiC...) has a poor native oxide or poor interface with its oxide.  $SiO_2$  is amorphous, has very few electronic defects and forms an excellent, abrupt interface with Si. (The abruptness of the interface is seen by the absence of intermediate valence states in the Si photoemission core spectra.)  $SiO_2$  can be etched and patterned to a nanometer scale. Its only problem is that it is possible to tunnel across it when very thin. Hence, we must loose these advantages of  $SiO_2$  and start to use a new high K oxide. We can in principle choose it from a large part of the Periodic Table.

The requirements of a new oxide are six-fold [2,5,9];

- 1. Its K value must be high enough to use economically for a reasonable number of scaling nodes.

- 2. The oxide is in very close contact to the Si channel, so it must be thermodynamically stable with it.

- 3. It must act as an insulator, by having band offsets with Si of over 1 eV to minimise carrier injection into its bands [20]

- 4. It must be kinetically stable, and able to be processed at 1000°C for 5 seconds (in gate first flow).

- 5. It must form a good electrical interface with Si.

- 6. It must have few electrically active defects.

Interestingly, once SiO<sub>2</sub> is replaced as the dielectric, a key performance advantage of Si is lost, so other semiconductors such as Ge or III-Vs can now be considered for use as the channel. Silicon continues to provide very useful mechanical properties however, and such properties must be considered in the course of fabrication with automatic-loading tools. Other semiconductors are less abundant and have poor (brittle) mechanical properties. Moreover, as the industry is tooled for large area Si wafers with diameters expected to be at least 450mm in the next decade, it will remain a dominant material for integrated circuit manufacturing in all aspects until the end of the technology roadmap.

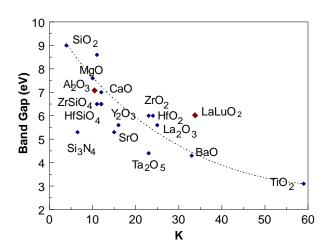

# 2.1 K value

The first key requirement is that the oxide's K value should be over 12, preferably 25-35. There is a trade-off between K value and the band-offset condition, which requires a reasonably large band gap. Table 1 and Fig. 6 shows that an oxide's K value tends to vary inversely with its band gap, so we must accept a relatively low K value [20]. There are numerous oxides with very large K, such as Ta<sub>2</sub>O<sub>5</sub> or SrTiO<sub>3</sub>, which were candidates for DRAM capacitor dielectrics, but their band gaps are too small.

The static dielectric constant is the sum of the electronic and lattice contributions,  $\kappa = \kappa_e + \kappa_{lattice}$ . The electronic component  $\kappa_e$  is also the optical dielectric constant  $\epsilon_{\infty}$  and it equals the square of the refractive index,  $n - \kappa_e = \epsilon_{\infty} = n^2$ .  $\epsilon_{\infty}$  values are typically in the range 4-5 for the wide gap oxides of interest. Thus they are *not* the main source of the high K. The large static dielectric constant arises from the lattice contribution,

$$\kappa - n^2 = \sum \frac{Ne^2 Z *_T^2}{m\omega_{TO}^2}$$

(5)

Here, N is the number of ions per unit volume, e is the electronic charge,  $Z_T^*$  is the ion's transverse effective charge, m is the reduced ion mass,  $\omega_{TO}$  is the frequency of the transverse optical phonon

and the sum is over the ions. Large values of  $\kappa_l$  occur when  $Z^*$  is large and/or the frequency of a polar optical mode  $\omega_{TO}$  is small. It often arises in materials that are incipient ferroelectrics.

# 2.2 Thermodynamic Stability

The second requirement arises from the condition that the oxide must not react with Si to form either SiO<sub>2</sub> or a silicide by the reactions,

$$MO_2 + Si = M + SiO_2 \tag{6}$$

$$MO_2 + 2 Si = MSi + SiO_2$$

(7)

This is because any SiO<sub>2</sub> layer increases the EOT and negates the effect of the new oxide, while silicides formed by (7) are metallic and would short circuit the channel.

This condition requires that the oxide have a higher heat of formation (per O atom) than  $SiO_2$  itself as noted by Hubbard and Schlom [21] and Schlom and Haeni [22] found that this restricts choices to very few oxides, from columns II, III and IV of the Periodic Table. These oxides are SrO, CaO, BaO,  $Al_2O_3$ ,  $ZrO_2$ ,  $HfO_2$ ,  $Y_2O_3$ ,  $La_2O_3$  and the lanthanides. It excludes some otherwise useful oxides such as  $Ta_2O_5$ ,  $TiO_2$  and the titanates  $SrTiO_3$  and  $BaTiO_3$ . The group II oxides SrO etc are less useful as they have rather low K values. Hence this leaves us with  $Al_2O_3$ ,  $ZrO_2$ ,  $HfO_2$ ,  $Y_2O_3$ ,  $La_2O_3$ ,  $Sc_2O_3$  and some lanthanides such as  $Pr_2O_3$ ,  $Gd_2O_3$  and  $Lu_2O_3$ .

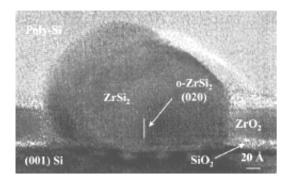

Zr and Hf are both from column IV and are generally believed to be two very similar elements. However, it was subsequently found that ZrO<sub>2</sub> is slightly more reactive with Si [23,24] and can form the silicide, ZrSi<sub>2</sub>. An example is shown in Fig. 7. For this reason, HfO<sub>2</sub> was preferred over ZrO<sub>2</sub>, particulary for the higher thermal budget gate-last case.

Of the other binaries,  $La_2O_3$  has a slightly higher K than  $HfO_2$ , but is hygroscopic.  $Al_2O_3$  has a rather low K value and high defect density.  $Y_2O_3$  and  $Lu_2O_3$  have a lower K than  $La_2O_3$ . The other lanthanides  $Pr_2O_3$ ,  $Gd_2O_3$  etc are comparable to La [25-28] but have no particular advantage.

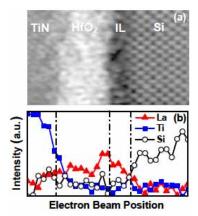

The interface between  $HfO_2$  and the Si substrate has undergone considerable scrutiny in the last decade. Thermodynamically, one anticipates  $HfO_2$  to be stable on direct contact with Si, but kinetic effects can alter the interface, potentially resulting in a compositionally graded interface somewhat representative of a silicate [2,29]. The composition of such an interface has spawned some controversy over the years, with some workers indicating that the interface after  $HfO_2$  deposition is purely  $SiO_2$ , [30-34] while others indicating the presence of significant amounts of Hf near at the interface [35-38], depending upon the deposition and thermal treatment details.

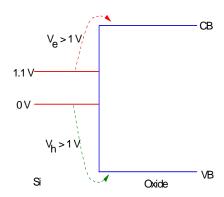

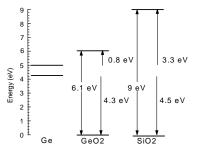

#### 2.3 Band offsets

The high K oxide must act as an insulator. This requires that the potential barrier at each band must be over 1 eV in order to inhibit conduction by the Schottky emission of electrons or holes into the oxide bands [20,39], as shown in Fig 8. SiO<sub>2</sub> has a wide gap of 9 eV, so it has large barriers for both electrons and holes. However, for oxides with a narrower band gap like SrTiO<sub>3</sub> (3.3 eV), their bands must be aligned almost symmetrically with respect to those of Si for both barriers to be over 1 eV. In practice, the conduction band offset is smaller than the valence band offset. This limits the choice of oxide to those with band gaps over 5 eV. The oxides that satisfy this criterion are Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub> La<sub>2</sub>O<sub>3</sub> and various lanthanides, and their silicates and aluminates [20]. It is interesting that these are the *same* oxides that pass the thermal stability criterion. This is because a high heat of formation correlates with a wide band gap. On the other hand, the conduction band offset of SrTiO<sub>3</sub> is essentially zero [20,40], so this oxide is unsuitable.

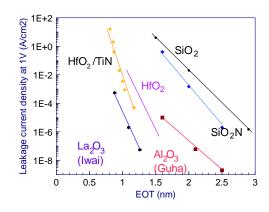

The early leakage current data for various high K oxides are plotted as a function of EOT in Fig. 8 for typical high K oxides, HfO<sub>2</sub> from [17], for ZrO<sub>2</sub> from Gusev et al [41], for Al<sub>2</sub>O<sub>3</sub> of Gusev [17] and Guha [42,43], for La<sub>2</sub>O<sub>3</sub> from Iwai [26] and data for HfO<sub>2</sub> films with poly-Si electrodes and HfO<sub>2</sub> with TiN electrodes, from Tsai [44].

Device scaling will require the use of ever-smaller EOTs. Yeo [45] defined a Figure of Merit, k, for direct tunnelling, which combines the barrier height  $\phi$ , tunnelling mass m\* and dielectric constant K,

$$J = J_0 \exp(-2k.t)$$

$$k = (2m*\phi)^{1/2} (K/3.9)$$

(8)

where *t* is the EOT. Lanthanides have the lowest leakage in Fig 9 and the highest figure of merit because they have the largest conduction band (CB) offset. Hf alloys are presently preferred because lanthanides are hygroscopic and because they give low gate threshold voltages for both FET polarities, nFET and pFET.

# 2.4 Kinetic Stability

The fourth condition is kinetic stability, that in a gate-first process the oxide must withstand the dopant activation anneal for 5 secs at  $1000^{0}$ C. We must choose to use a crystalline or amorphous oxide. If an amorphous oxide is desired, this is a strenuous condition as most high K oxides are not good glass formers, unlike SiO<sub>2</sub>. In particular, HfO<sub>2</sub> and ZrO<sub>2</sub> crystallise at lower temperatures (400C) and, would be nano-crystalline in use.

The crystallisation problem can be circumvented by alloying the oxide with a glass former  $- SiO_2$  or  $Al_2O_3$  – giving either a silicate or an aluminate [29,46]. This retains a stability against crystallisation up to nearly  $1000^{0}$ C. However, silicates have significantly smaller K values. The addition of nitrogen is beneficial as it further lowers diffusion rates and raises crystallisation temperatures, so that Hf silicates can then pass this criterion [47].

The arguments against poly-crystalline oxides are that its grain boundaries might cause higher leakage currents, act as dopant diffusion paths, and lead to fluctuating K values from grain to grain. On the other hand, Lee [48] and Kim [49] found that leakage currents of amorphous and nanocrystalline HfO<sub>2</sub> are similar, so there was no specific conduction along grain boundaries.

There have been extensive measurements of the atomic diffusion rates of Hf, O, B and P in  $HfO_2$  and Hf silicate by secondary ion mass spectroscopy (SIMS), Medium Energy Ion Scattering (MEIS) and nuclear reaction profiling [50-55]. The addiotn of nitrgoen to  $HfO_2$  or Hf silicate is also very effective in reducing diffusion rates and also increasing crystallisation temperatures. Nitrogen has other benefits on the electrical properties that are covered in section 5.3.

# 2.4 Interface Quality and Defects

The high electrical quality of the  $Si:SiO_2$  interface was the key advantage of Si as a semiconductor. The interface is essentially atomically abrupt with few sites with intermediate valence; the Si atoms are either in Si or in  $SiO_2$  as seen by XPS core level spectra [56,57]. The interface roughness consists of atomic steps spaced apart by 20 nm in the highest quality oxide.

The electrical quality of the Si: high K interface must be of the highest quality in terms of roughness and absence of defects in order to avoid scattering cariers. Electrically active defects are defined as atomic configurations which give rise to electronic states in the oxide band gap which can trap carriers. Typically, these are sites of excess or deficit of oxygen or impurities. They can be at the interface or in the oxide layer.

Defects are undesirable for four reasons. Firstly, charges trapped in defects shift the gate threshold voltage of the transistor,  $V_T$ , the voltage at which it turns on. Secondly, the trapped charge changes with

time so  $V_T$  shifts with time, leading to instability of operating characteristics. Thirdly, trapped charge scatters carriers in the channel and lowers the carrier mobility. Fourthly, defects cause unreliability; they are the starting point for electrical failure and oxide breakdown.

$SiO_2$  is an almost ideal insulating oxide, having a low concentration of defects which give rise to states in the gap. This is fundamentally because of its low coordination number, so that its bonding can relax and re-bond any broken bonds at possible defect sites. Most of the remaining defects are readily passivated by hydrogen, as seen in electron spin resonance [58-61].

The high K oxides differ from  $SiO_2$  in that they are not intrinsically low defect density materials. Whereas  $SiO_2$  has a random network which can relax to heal defect sites,  $HfO_2$  and  $ZrO_2$  come from a family of fast ion conductors, with potentially large O vacancy concentrations. Hence, much of present-day engineering consists of pragmatic strategies to reduce oxide defect densities by process control and annealing.

On the other hand, the interface between Si and the high K oxide always has an  $SiO_2$ -rich interfacial layer, it is not an abrupt interface. This allows lower interfacial defect densities to exist in practice. However, after 6 years of further scaling, EOT is reaching values below 0.7 nm, and near-abrupt interfaces are close to being used.

### 2.5 Metal gate vs poly-silicon gate

While the effective capacitance thickness (eqn 4) indicated that scaling would eventually require the replacement of  $SiO_2$  by a high K oxide, and of the poly-Si gate by a metal gate, it was expected that the two technological changes could occur separately. However, it became clear that there was a reaction between Si and high K oxide. It was found that the reducing ambient during the CVD deposition poly-Si from silane causes a gross reduction of the  $ZrO_2$  or  $HfO_2$ , leading to silicide formation [23,62,63], as in Fig 7. It was realised that high K gate oxides and metal gates must be introduced simultaneously.

The second factor was 'Fermi level pinning' which will be described later, and was initially attributed to the formation of Hf-Si bonds at the HfO<sub>2</sub> /poly-Si gate interface [64-66]. Thus, it was decided to introduce high K oxies and metal gate simultaneously [1].

#### 2.6 Gate First/Gate Last Process

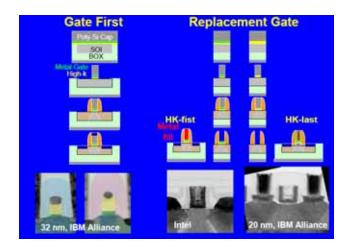

The interface between the gate electrode and the gate oxide is at least as critical to the FET performance as that between channel and the oxide. This interface sets the gate threshold voltage  $V_t$ , the turn-on voltage of the FET. Whereas the poly-Si gate electrode is refractory and compatible with  $SiO_2$ , the atoms in  $HfO_2$  diffuse much more easily and reactions with metal gates occur at lower temperatures. The details are covered later, but the realisation that such reactions will make the  $V_t$  very difficult to control led to the decision to develop a 'gate last' process.

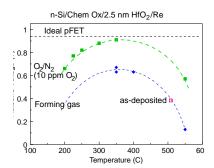

The gate first process (Fig 10a) follows the same process flow as with a  $SiO_2$  gate oxide [62]. In gate first, we sequentially deposit a gate oxide layer, gate work function tuning layer, and gate metal. The source and drain doping implants are carried out, and the dopant activation anneal to 1000C is carried out. This annealling temperature is too high for many gate stacks.

In the gate last process, (Fig 10b), the gate oxide is deposited followed by a poly-Si dummy gate [15,67]. The source drain dopant implants are carried out, followed by the dopant activation anneal. An interlayer dielectric is deposited for mechanical stability. This is then planarised by chemical mechanical polishing (CMP) down to the level of the top of the dummy gate. The dummy gate is then etched out, and the metal gate layers are then deposited into this hole, followed by an Al fill. An anneal to 500C is applied. In this way, the gate metal is not exposed to the 1000C temperature anneal.

Variant 2 of the gate-last process etches off both the dummy gate and a 'dummy gate oxide', and replaces both with new gate oxide and gate metal.

# 3 Materials Chemistry of high K oxides

# 3.1 Atomic Layer Deposition

The great advantage of  $SiO_2$  was that it can be grown by high temperature thermal oxidation of the Si substrate. In contrast, high K oxides must be deposited. Previously, deposited oxides were never as good as  $SiO_2$  thermal oxides, but they now have sufficient reliability to be used in transistor technology.

Several deposition methods have been employed in researching high-k dielectrics [68-70]. Sputtering is a physical vapour deposition (PVD) method. Its advantage is that it is broadly available and can produce pure oxides. A disadvantage is that oxides are insulators, so that sputtered oxides will have plasma-induced damage. Also, PVD is line of sight, so it does not give good conformal coverage. A first metal layer can be used to limit the interfacial layer formation and stop over-oxidation. Sputtered films are often used to initially examine dielectric properties prior to further work using CVD or ALD techniques as specialized precurosors are not required.

Another method to produce high purity thin oxides is to deposit metal by electron beam evaporation, which is controllable to small thickness, and then oxidise the metal by ozone or UV assisted oxidation. The advantage is that this produces less damage than oxide sputtering. Ideally, the oxygen partial pressure should be controlled to oxidise just the metal, but not the Si [71,72].

The preferred methods are chemical vapour deposition (CVD) and atomic layer deposition (ALD). CVD uses a volatile metal compound as a precursor, which is introduced into the chamber and oxidised during deposition onto the substrate. The advantages of CVD are that it is already widely used in the electronics industry for insulator deposition, it gives conformal coverage over complex shapes, and the growth rate is controllable. The conformality property is particularly valuable, as it allows deposition even on complex geometries such as the FinFET.

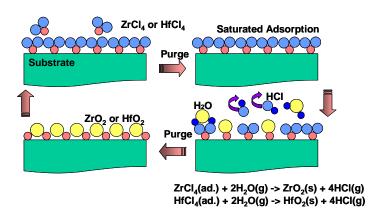

The most preferred deposition method is ALD. It is a method of cyclic deposition and oxidation [73-76]. It was first developed to produce conformal, pin-hole free insulating films for electroluminescent displays. Fig 11 shows the chemical reactions schematically for the precursor  $ZrCl_4$ . The surface is exposed to the precursor  $ZrCl_4$ , which is absorbed as a saturated monolayer. The excess precursor is then purged from the chamber by an Ar or nitrogen pulse. A pulse of oxidant such as  $H_2O_2$  or ozone is then introduced which fully oxidises the adsorbed precursor layer into  $MO_2$  and a volatile by-product such as HCl. The excess oxidant is then purged by another Ar pulse, and the cycle is repeated.

The effective chemical reactions are

$$ZrCl_4 + 2 OH_{surface} = ZrCl_2O_2 + 2 HCl$$

(9)

$$ZrCl_2O_2 + 2 H_2O = ZrO_2(OH)_2 \text{ surface} + 2 HCl$$

(10)

The existing  $ZrO_2$  surface is assumed to be terminated by OH groups at about  $300^{\circ}$ C. The  $ZrCl_4$  chemisorbs exothermically onto the OH sites by the exothermic elimination of HCl to form  $ZrCl_2O_2$ . In the second stage, water reacts with  $ZrCl_2O_2$  so that Cl atoms are eliminated via formation of HCl, leaving a layer of  $ZrO_2$  on the surface. It is noted that such precursors are C-free, which may improve insulator properties and reliability.

Each cycle of ALD adds a layer of oxide, which is usually much less than an atomic layer thick, despite its name. The precursor absorption saturates at less than one monolayer because of steric hindrance. This is not a significant disadvantage, it just takes more cycles to grow a certain thickness.

The precursor is designed so that both steps of absorption and oxidation are exothermic. The precursor must undergo self-limiting adsorption, be volatile, high purity, non-toxic, have no gas phase reactions, no self-decomposition, and no etching of the existing oxide. The first precursors for  $ZrO_2$  and  $HfO_2$  were their chlorides. However, these have a low volatility and tended to clog. They are preferred by industry as they avoid carbon impurities, and industry can handle the corrosive exhaust gases.

A wide range of organic ALD precursors has now been developed to allow high volatility and less corrosive exhausts [73-76]

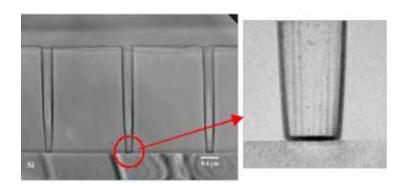

The main advantage of ALD is that it can grow the thinnest films of any method, and the most conformal films for step coverage or into deep trenches (Fig 12), but the growth rate is very low. Furthermore, a disadvantage of ALD and MOCVD is that they can introduce impurities such as C, H or Cl into the oxides, depending on the precursor. Post-deposition annealing is needed to densify ALD oxides and remove the impurities.

An early problem with ALD was nucleation. The most inert surface of Si is the H-terminated surface formed by HF-last cleaning. It was found that ALD using HfCl<sub>4</sub> or many organic precursors did not nucleate properly on HF-last Si surfaces [77,78]. This meant that oxide films even 3 ML thick were not fully 'closed' but islanded. Nucleation occurred more readily on a slightly pre-oxidised Si surface. Thus, ALD was carried out on a 'chemical oxide' (SiO<sub>2</sub>) surface formed by ozone or oxidative cleaning of Si. The nucleation problems on Si-H terminated surfaces were removed by using more sophisticated precursors [79,80].

The various types of ALD precursor are listed in Table 2. The precursors are designed to have the desired volatility, reactivity and stability [73-76,81-84]. The molecules are formed by adding organic ligands. The ligands create the volatility. Volatility is aided by using monomer ligands, which do not pack so easily in the solid state. The metal valence is satisfied by polar bonds from N or O atoms. These bonds define the stability and reactivity.

The alkoxides and diketonates are commercially available oxygen containing precursors, of reasonable reactivity. The nitrogen-based ligands are becoming more favoured. It turns out that amido compounds have the desired reactivity to give ALD on oxide surfacers and also to nucleate on Si-H terminated surfaces. Beta-diketonates are useful for lanthanide oxides. ALD can also produce metal nitrides for electrodes or diffusion barriers [83].

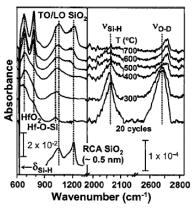

Ho et al [35] followed the progress of the ALD deposition of HfO<sub>2</sub> films over a number of ALD cycles by FTIR, see Fig 13. The film was grown from tetrakis ethyl- methyl amino hafnium (TEMAH) or Hf(N(CH<sub>3</sub>).(C<sub>2</sub>H<sub>5</sub>))<sub>4</sub> at 100C with water as oxidant on an H terminated Si surface. First, the infra-red spectrum showed that there is an abrupt interface during growth, with Hf-O-Si bonds gradually replacing Si-H bonds. The HfO<sub>2</sub> growth progress can be seen from the Hf-O modes. The continuing presence of Si-H shows that there is still some island growth even after growing 3 ML of oxide. A separate broadened and red-shifted Si-H mode occurs as the Si-H group becomes surrounded by HfO<sub>2</sub>. The reaction of the precursor, not the oxidant, is thus crucial.

The film was then subjected to thermal annealing. The film had O-D modes (D=deuterium) from the  $D_2O$  oxidant. The post-deposition anneal is used to densify the film and remove contaminants such as organics, water, etc. It is found that at 400-500C, the O-H modes disappear and Si-O modes appear. An interfacial  $SiO_2$  layer 0.9 nm thick has grown. It turns out that ALD leaves an oxygen-rich film. When the oxidant is water, the film contains -OH groups. Annealing should evolve these as  $H_2O$  molecules. However, as the film densifies,  $H_2O$  molecules are too large to escape. It is only possible for H to diffuse either as  $H^+$  ions or  $H_2$  molecules, desorbing as  $H_2$ . Further annealing to higher temperatures expels the excess oxygen, and this creates the interfacial  $SiO_2$  layer by oxidising the underlying Si. There is no interfacial layer *during* growth itself.

Recent advances in ALD have been the ability to deposit LaAlO<sub>3</sub> using tris(N,N0-diisopropylformamidinate)—lanthanum and trimethyl aluminium and the epitaxial growth of oxides on Ge and III-Vs [84].

# 3.2 Alloy Crystallisation

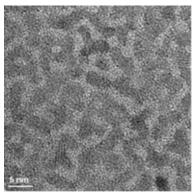

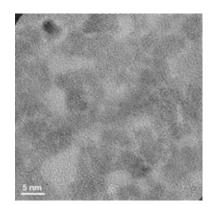

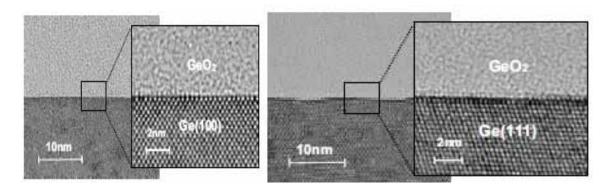

Silicate and aluminate alloys of Zr, Hf and La oxides are often used instead of the pure metal oxides due to their higher resistance to crystallisation [29,53,85]. For Zr silicate, crystallisation directly to the crystalline  $ZrSiO_4$  is inhibited by kinetics. Instead, crystallisation occurs by a phase separation into  $ZrO_2$

and SiO<sub>2</sub> phases, followed by a crystallisation of the ZrO<sub>2</sub> component [86]. This can be seen for HfO<sub>2</sub>-SiO<sub>2</sub> alloys in the high-resolution transmission electron microscope images in Fig 14 for two different compositions from Stemmer [87].

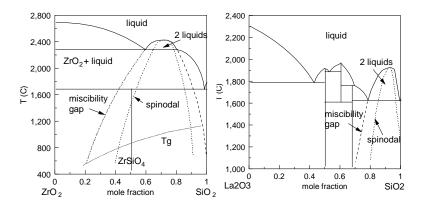

The phase diagram of the ZrO<sub>2</sub>-SiO<sub>2</sub> system is reasonably well known [88], Fig 15(a). That of HfO<sub>2</sub>-SiO<sub>2</sub> is similar. The key factor is that ZrO<sub>2</sub> and SiO<sub>2</sub> liquids are immiscible over a range of composition due to the large ionic charge of Zr. This 'miscibility gap' can be extrapolated to lower temperatures to define a solid phase miscibility gap. It also defines a spinodal region in which the alloy will spontaneously phase separate to lower its free energy [88]. The glass transition temperature is also marked in Fig 15(a). Thus, Zr silicates crystallise by two mechanisms. For 20-60mol% Zr, silicates crystallise by spinodal decomposition followed by crystallisation. This leads to small grain sizes. Silicates with over 60% Zr crystallise by the kinetically limited nucleation and growth of crystalline ZrO<sub>2</sub>. This was confirmed by extensive TEM and x-ray scattering on Hf silicates by Stemmer [89].

The La silicate phase diagram in Fig 15b) [86,90] is somewhat similar to that of  $ZrSiO_4$  except that the two-phase region is further towards  $SiO_2$ . The main difference is that  $La_2O_3$  forms a much more stable silicate, whereas Hf or Zr silicates prefer to phase separate into the parent oxides.

### 3.4 The interfacial layer

An interfacial layer of  $SiO_2$  or silicate usually exists between the Si channel and the high K oxide layer. Fig. 16 shows a cross-sectional of an example [91]. There are advantages and disadvantages to this interfacial layer, as long as its presence and thickness can be controlled. The overall EOT of a layer 1 of  $SiO_2$  and a layer 2 of high K oxide is given by the series capacitance formula,

$$1/C = 1/C_1 + 1/C_2 \tag{11}$$

which becomes

$$EOT = t_{SiO2} + EOT_{hiK}$$

(12)

Thus, an extra  $SiO_2$  layer is undesirable as it increases the total EOT. In fact, the K of  $SiO_2$  (3.9) is so small that an  $SiO_2$  layer will rapidly use up the EOT allocation. It is a severe limitation to scaling of EOT below 1.0 nm.

The  $SiO_2$  layer does not arise from the direct reaction of  $HfO_2$  with Si. It arises from the diffusion of O through the  $HfO_2$  layer to oxidise the Si underneath. The  $SiO_2$  layer usually grows during the post-deposition annealing stage, not during growth [92]. It can arise for ALD oxide, because the oxide is initially O-rich and it looses oxygen to oxidise the underlying Si [35]. It can also occur due to oxygen permeation through the top electrode, if the gate material is porous to oxygen.

There was great advantage in retaining the SiO<sub>2</sub> intelayer in the early development of high K gate stacks, because then the Si interface is still between Si and SiO<sub>2</sub>, and it retains the low defect density and relatively high reliability of this interface [88].

The second reason a SiO<sub>2</sub> layer exists is intentional, for beneficial reasons. For example, a 'chemical oxide' acts as a nucleation layer for ALD growth of HfO<sub>2</sub> [79,80]. The SiO<sub>2</sub> layer is also introduced to improve the overall electrical quality of the Si-oxide interface, see section 7. The Si-SiO<sub>2</sub> interface is well understood and can be processed to be high quality. In principle, it can be made with a very low defect concentration, by annealing. A SiO<sub>2</sub> layer spaces the Si channel from the high K oxide, which can lessen mobility degradation due remote scattering.

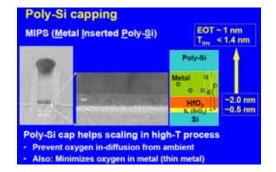

#### 3.5 Metal Inserted Poly-Silicon gates

A number of metals used as gate metals such as W contain oxygen or allow O diffusion. To stop the metal being a source of oxygen, the gate-first process uses a 'metal inserted poly-Si' (MIPS) gate

electrode, which is a thin layer of the metal underneath the poly-Si capping layer, in which the Si acts as a diffusion barrier to oxygen [10].

# 3.6 Oxygen Scavenging

The continued scaling of EOT below 1.0 nm and towards 0.5 nm requires us to either reduce the thickness of the interfacial layer, or increase the K values. In 2006-2010 there was considerable work towards developing 'higher K' oxides than  $HfO_2$ , as described in section 4.3. However, Ando et al [93] pointed out that the contribution of the  $SiO_2$  based interlayer to EOT is so large than higher K would have little effect. Ando et al [93-97] then tried the idea of increasing the K of the interlayer, for example by alloying it with lanthanides. However, there are disadvantages to adding La, as it affects the gate threshold voltage.

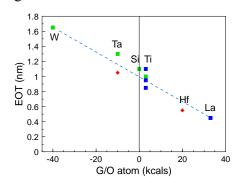

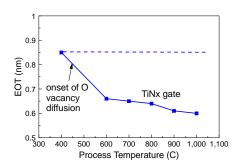

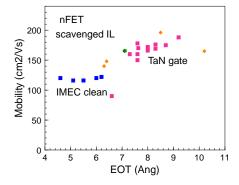

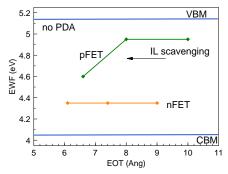

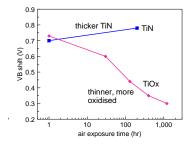

It was decided to reduce the interfacial  $SiO_2$  layer thickness. The  $SiO_2$  can be thinned down by an 'oxide scavenging' process, by placing an oxygen scavenging metal layer such as Ti or Hf above the  $HfO_2$  to 'suck' out the O through the  $HfO_2$  by annealing [98-102]. The scavenger metal should have an oxide heat of formation per O atom than is greater than that of  $SiO_2$  (Fig 11). Ando [95] and Frank et al [96] have carried out extensive work on this process. This is described in more detail in section 7.3.

# 4 Bonding and electronic structure

# 4.1 Nature of Bonding in high K oxides

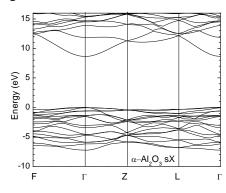

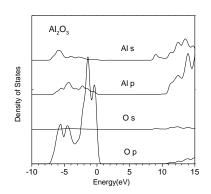

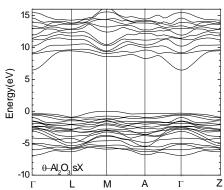

The high K oxides of interest, except for  $Al_2O_3$ , are closed shell transition metal oxides [103,104].  $Al_2O_3$  is an s,p bonded oxide. Fig 17(a,b) show the density of states (DOS) anm screened exchange band structure of corundum  $Al_2O_3$  the most stable crystalline phase. The top of the valence band lies at 0 eV and the band gap lies from 0 to 8.8 eV [105]. The bonding in  $Al_2O_3$  is more ionic than in  $SiO_2$ , and its atoms have ionic coordinations of 6 for Al and 4 for O. However, its electronic DOS does resemble that of  $SiO_2$ . Its valence band consists mainly of O p states and a conduction band of mainly Al s,p states.

The actual phase of  $Al_2O_3$  used in gate stacks is amorphous, with lower mass density and a lower coordination of ~4.5 for Al and 3 for O [106,107]. This reduces the band gap of the  $Al_2O_3$  to about 6.2-6.6 eV [108]. It is possible to model the amorphous phase with one of the lower density, lower symmetry phases such as  $\theta$ -  $Al_2O_3$  whose band structure is shown in Fig 17(c) [109].

The other high K oxides are closed shell (fully ionised) transition metal oxides. While many transition metal oxides are notable for their mixed valence, here we only deal with fully ionised metal ions. This means the oxides are wide band gap, and do not suffer from the correlation effects.

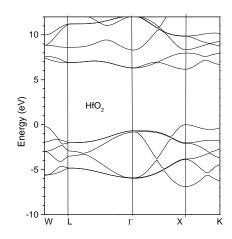

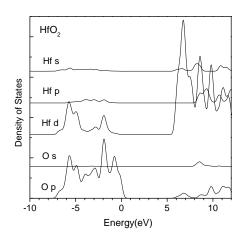

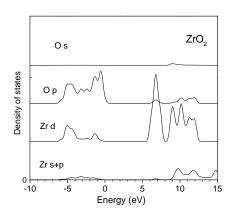

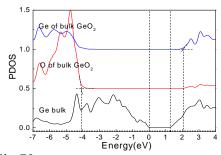

The most important high K oxide is  $HfO_2$ .  $HfO_2$ , like  $ZrO_2$ , has three phases, cubic, tetragonal and monoclinic [110,111]. The different metal coordinations of these phases are shown in Fig. 18. For large grain sizes, monoclinic is the most stable phase, and cubic the least stable phase. Fig. 19 shows the band structure of cubic  $HfO_2$  and the partial density of states (PDOS) [103]. This phase has an indirect band gap with a maximum at X formed from O p states. The conduction band minimum is a  $\Gamma_{12}$  state of Hf 5d orbitals. The valence band is 6 eV wide. The conduction band PDOS is split by the crystal field field into a lower band of e states and an upper band of  $t_2$  states 5 eV higher.

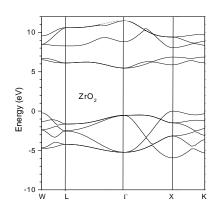

The electronic structure of the ZrO<sub>2</sub> phases is very similar to that of HfO<sub>2</sub> except that the crystal splitting of the Zr 4d states in the conduction band is smaller than in ZrO<sub>2</sub> (Fig 20) [103].

$TiO_2$  is another group IV oxide which has various structures including rutile. Its gap is much narrower than that of  $HfO_2$  or  $ZrO_2$  at about 3.3 eV [112].

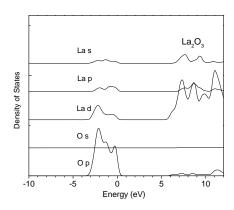

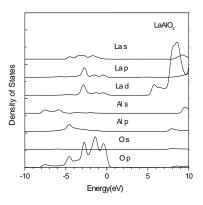

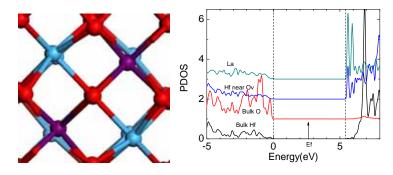

Crystalline  $La_2O_3$ , has a hexagonal structure in which La is 7-fold coordinated, with 4 short bonds and 3 longer bonds. The DOS of  $La_2O_3$  in Fig. 21 shows that the valence band is strongly localised on the O p states and the conduction band is on La d states with some La s,p states starting at 8 eV [103]. The band gap is indirect and 6 eV. The valence band is now only 3.5 eV wide, narrower than for  $ZrO_2$ . The ionicity is higher than in  $ZrO_2$ .

Of the other group IIIA metal oxides,  $Y_2O_3$  has the cubic bixbyite (defect spinel) structure. This has a large 56 atom unit cell in which there are two types of Y sites, both 7-fold coordinated. This structure occurs because Y has a smaller ionic radius than La. The band gap of  $Y_2O_3$  is direct and is about 6 eV. The valence band is again only 3 eV wide. The partial DOS shows the valence band is largely O p states. The conduction band minimum has mixed Y d,s character. The other lanthanides adopt either the La<sub>2</sub>O<sub>3</sub> or bixbyite structure.

In all these transition metal oxides, the conduction band minimum at  $\Gamma$  lies at the metal d energy, while the top of the valence band are non-bonding O 2p states lying at the O 2p energy. Thus the band gap is a pure ionic gap between O 2p and metal d states. The band gap is proportional to the metal atomic d orbital energy [1113].

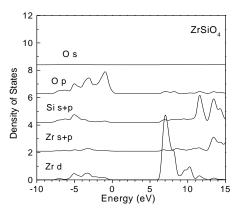

ZrSiO<sub>4</sub> is typical of the transition metal silicates. Crystalline ZrSiO<sub>4</sub> (zircon) has the body-centred tetragonal structure. Each Zr atom has eight O neighbours. Each Si has four O neighbours in a tetrahedral arrangement, and each O has three neighbours, two Hf and one Si. These coordinations may carry over to the amorphous phases and amorphous alloys. Its partial DOS is shown in Fig 22. The band gap is about 6.5 eV [103]. The valence band is about 7 eV wide [114-116]. The conduction bands form two blocks. The lower conduction band is due to Zr d states and lies between 6.5 eV and 8 eV, and a second conduction band due to Si-O antibonding states lie above 9 eV.

The extended x-ray fine structure spectrum [117] suggest that the coordinations in Zr silicate alloys do not follow the zircon structure, but are locally more like in pure ZrO<sub>2</sub> or pure SiO<sub>2</sub>. This implies local phase separation as noted by Pignedoli [118].

It is an important general rule that the conduction band of Zr silicates forms two non-mixing  $ZrO_2$ -like and  $SiO_2$ -like bands. The states do not mix because the Si s,p states and metal d states have different local symmetry. Thus, the CB minimum of the silicates has a Zr d character as long as Zr is present, and the band gap increases only slowly, with very strong bowing below the virtual crystal model. Experiments by Kato [119] confirm this.

Another large class of possible gate oxides are the perovskites like SrTiO<sub>3</sub>. In the ABO<sub>3</sub> structure, the smaller transition metal ion occupies the B site which is octahedrally coordinated by six oxygens. The oxygens are bound to two B ions, while the A ion is surrounded by twelve oxygen ions. The band gap of SrTiO<sub>3</sub> is direct and 3.3 eV wide. Due to this small gap, SrTiO<sub>3</sub> itself is not useful as a gate oxide.

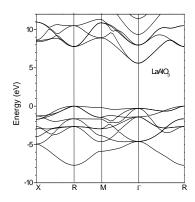

There has recently been considerable work on other perovskites with larger band gap. LaAlO<sub>3</sub> was the first. It is important because it has a large dielectric constant, and a close lattice match to Si. It is unusual in that the transition metal La occupies the A site and Al occupies the octahedral B site. The partial DOS of LaAlO<sub>3</sub> is shown in Fig. 23 [120]. The band gap is 5.6eV from the spectroscopic ellipsometry of Lim [121]. However, the problem with LaAlO<sub>3</sub> is that it looses some of its high K property when it becomes amorphous.

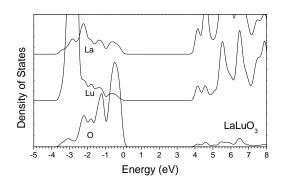

Following this, numerous combinations of rare earths at A and B sites were tried, such as DyScO<sub>3</sub> and LaLuO<sub>3</sub>. They all have band gaps of about 5.6 eV, and have quite high dielectric constants, usually above 25 [122]. Fig. 24 shows the PDOS of LaLuO<sub>3</sub> which includes the filled Lu 4f states in the valence band.

The other type of perovskite is SrHfO<sub>3</sub>. This retains the simple 2-4 valence of SrTiO<sub>3</sub>, but is more useful because it has a band gap of 6.0 eV due to the Hf [123].

These various band structures above have been calculated using the local density approximation (LDA) in the generalised gradient approximation (GGA). The LDA under-estimates the band gap of semiconductors and insulators. Many calculations have since used more advanced methods such as hybrid functionals (HSE or screened exchange) [124-127], or by the GW approximation [128,129]. These give calculated band gaps close to the experimental values.

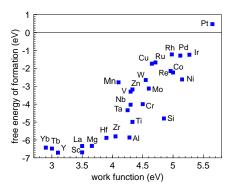

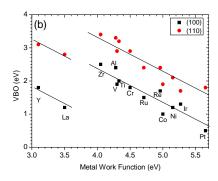

The high K oxides all have a very large heat of formation, they are very exothermic oxides. This is seen if we plot theoxide's heat of formation against the work function of the parent metal, as in Fig 25. The oxide heat of formation is equivalent to the Ellingham diagram at  $0^{0}$ K. The metal work function is related to the Pauling electronegativity of the metal. It is interesting that there is a rough linear correlation of the heat of formation with the work function, until the heat of formation tends to saturate at large work functions.

# 4.2 Dielectric constants

As noted in section 2.1, the high value of dielectric constant arises from the lattice contribution to K, whereas the electronic contribution to K is relatively minor. Thus high K oxides are incipent ferroelectrics. Any desire to increase K must target the lattice contribution.

The dielectric constants have been calculated in the LDA for the various phases of  $HfO_2$  and  $ZrO_2$  [130,131]. This allows us to understand the differences and the anisotropies. Rignanese [131] found that the tetragonal phase has the largest and most anisotropic K, but not by as much as found by Zhao and Vanderbilt [130]. These calculations were extended to lanthanides such as  $Lu_2O_3$  [126].

# 4.3 Higher K and Phase control

The continued scaling of MOSFETs contains high k oxides would appear to require the development of higher K oxides [133,122,145-153]. High K oxides are incipient ferroelectrics. Nevertheless, amorphousness is incompatible with ferroelectricity, as this requires ordered ionic displacements. Thus, huge K values are unlikely.

On the other hand, Shannon [134] observed that ionic polarisabilities were additive, not just the electronic part which might be expected from bonding arguments, but even the ionic part. Thus the K value varies with the ionic density of the oxides, and the component ions.

Amorphous  $HfO_2$  has a lower K value than cubic  $HfO_2$ , as has monoclinic  $HfO_2$ , as both have a lower density than cubic  $HfO_2$ . On the other hand tetragonal  $HfO_2$  has a higher K value than cubic  $HfO_2$ , because of its lower frequency polar lattice modes. There has recently been interest in stabilising these higher K phases.

The first method is to use the ability of Zr itself to stabilise its tetragonal phase, and when alloyed with HfO<sub>2</sub>, as seen by [135-137]. The second method is to dope the oxide with a smaller diameter group IV element such as Si or Ge [138,139]. The key point is that group IV dopants stabilise the tetragonal phase over the monoclinic or cubic phase, while the group III elements like Y stabilise the cubic phase, as used in ceramics and jewelry [140-144]. A doping content of 2-7% is needed.

Many higher K oxides were synthesied by adding rare earths to the perovskites [145-154]. The important aspect of these oxides is that they combine a higher K value with a large conduction band offset, so their overall figure of merit (eqn 7) is high. LaLuO<sub>3</sub> is unusual because it maintains its high K value even in its amorphous phase [122,147,149], unlike LaAlO<sub>3</sub>. These metals are from opposite ends of the lanthanide series and have quite different ionic radii, La is large, Lu is smaller. Fig. 21 shows its density of states [147]. Because of the different ionic radii, LaLuO<sub>3</sub> remains amorphous up to about 900C. This makes it one of the most interesting higher K oxides [147,148]. However, as noted in section 3.6, ultimately the higher K route to scaling is unsuccessful, reducing the interlayer thickenss by scavenging is recognised to be the most promising method.

This brings us to the last aspect of phase control. In the same way that the tetragonal phase has the highest K of the  $HfO_2$  phases, the hexagonal phase of trivalent oxides like  $La_2O_3$  has a much higher K than its bixbyite (cubic) phase [155,156].

#### 4.4 Band Offsets

The band offset between the oxide and Si defines the barrier for injection of electrons or holes into the oxide bands, Fig 26. The conduction band (CB) offset tends to be the smaller of the two. The CB offset is one of the key criteria in the selection of a gate oxide. It must be over 1 eV to give adequately low leakage current [20]. The band offset is measured by methods such as photoemission.

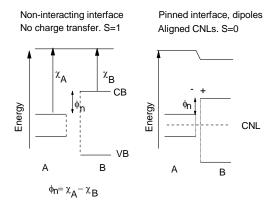

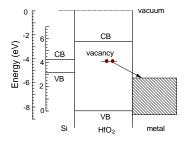

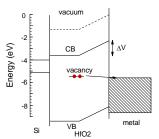

This band alignment at an interface is controlled by any dipole formed by charge transfer across the bonds at the interface. For two non-interacting surfaces, there is no charge transfer, no dipole, and the conduction band line up is given by the difference between the two electron affinities (the energy of the

conduction band edge below the vacuum level) (Fig 26) [20]. This is called the Schottky limit. If the surfaces interact, charge transfer occurs across the interface, and the resulting interface dipole modifies this offset. The charge transfer acts to align a reference energy level in each surface. In the limit of strong coupling, known as the Bardeen limit, these levels are fully aligned. The band offset is then given by the difference of this reference energy level below the two conduction bands, and is independent of the vacuum levels.

The band line up at an interface is controlled by a dipole formed by charge transfer across the interface bonds [157-159]. The dipole consists of two components, a component intrinsic to the bulk oxide and a component that depends on the interface chemical bonding. The intrinsic component is of interest because the specific bonding at the interface is usually not known.

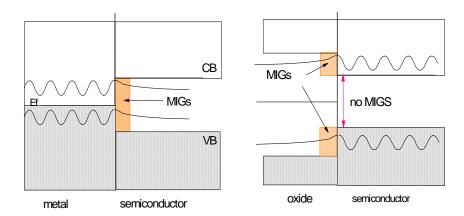

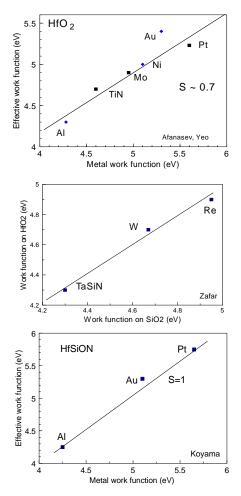

We first consider the intrinsic band offset. First, the oxide-semiconductor interface is just a variant of the interface between two semiconductors, with the oxie treated as a wide bandgap semiconductor. Second, a semiconductor-semiconductor interfaces is treated as a special case of a semiconductor-metal interface (which is known as a Schottky barrier). A particular model of dipoles at a metal-semiconductor interface is the metal induced gap states (MIGS) model [160-162,20]. This model says that in the energy range of the semiconductor band gap, the travelling wave states of a metal decay into the semiconductor as evanescent states called MIGS, Fig 27(a). These states are filled up to some cutoff energy called the charge neutrality level (CNL). In general, the work function of the metal does not equal the CNL energy of the semiconductor, so that when the two systems come into contact, there is a charge transfer between the two which creates an interface dipole. This dipole now tries to align the semiconductor's CNL with the metal Fermi level. The Schottky barrier height, the energy of the semiconductor conduction band above the metal Fermi level, is then given by

$$\phi_{\rm n} = S(\Phi_{\rm M} - \Phi_{\rm S}) + (\Phi_{\rm S} - \chi_{\rm s}) \tag{13}$$

where  $\Phi_M$  is the metal work function,  $\Phi_S$  is the charge neutrality level of the semiconductor measured from the vacuum level, and  $\chi_S$  is the electron affinity (EA) of the semiconductor. S is a dimensionless pinning factor given by S=d $\phi_n$ /d $\Phi_M$  which defines how strongly the MIGS can force this alignment. S is given in the linear approximation by [163]

$$S = \frac{1}{I + \frac{e^2 N\delta}{\varepsilon \varepsilon_0}} \tag{14}$$

where e is the electronic charge,  $\varepsilon_0$  is the permittivity of free space, N is the density of the interface states per unit area and  $\delta$  is their extent into the semiconductor. Strong alignment or pinning corresponds to S=0, while no pinning corresponds to S=0. Large values of N and  $\delta$  give strong pinning.

Monch [160] found empirically that S in (14) varied with the electronic dielectric constant  $\varepsilon_{\infty}$  of the semiconductor as

$$S = \frac{1}{1 + 0.1(\varepsilon_{\infty} - 1)^2} \tag{15}$$

This is an empirical rule, in addition to the basic MIGS model.

The MIGS model is then extended to describe the band offsets between two semiconductors A and B, or an oxide and a semiconductor. Charge transfer tends to align the CNL of the bulk oxide and the CNL of Si. The CB offset is then [20],

$$\phi_{n} = (\chi_{a} - \Phi_{S,a}) - (\chi_{b} - \Phi_{S,b}) + S(\Phi_{S,a} - \Phi_{S,b})$$

(16)

Here,  $\chi_a$  is the electron affinity (EA) of the oxide,  $\chi_b$  is the electron affinity of the semiconductor, and  $\Phi_{S,a}$  and  $\Phi_{S,b}$  are the CNLs of the oxide and semiconductor respectively. All the energies in eqn (15) are measured from the vacuum level, except  $\phi_n$  which is measured from the conduction band edge. S is again the Schottky barrier pinning factor. Note that for two semiconductors, the MIGS only exist where there are band states on one side of the interface, but not where there is a gap on both sides [164], Fig 27(b).

This CNL model is a zeroth-order, but fully parameterised model of band offsets, in which the CNLs are determined by the bulk electronic structure of oxide and Si. The local bonding at the interface does not enter in this model. The CNL acts like the mean electronegativity of the semiconductor [19].

The CNL is an intrinsic property of the bulk semiconductor. It is not a function of the surface chemistry or reconstruction. It is only a function of the bulk band structure [162,20].

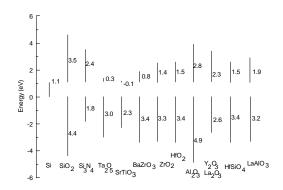

The predicted CB offsets in this model [20,103,165] are given in Fig. 28 for the various oxides. Table 3 compares these to the experimental values measured by photoemission, internal photoemission or barrier tunneling [166-186]. Photoemission measures the VB offset, and this is converted into the CB offset by subtracting the oxide and Si band gaps. Internal photoemission measures the energy from the Si valence band to the oxide's conduction band, or the Si conduction band to the oxide's valence band, depending on the Si doping and of the polarity of the applied voltage.

It is seen that the predicted and experimental offsets generally agree well. Those for HfO<sub>2</sub> and ZrO<sub>2</sub> from photoemission agree well [161,184]. SrTiO<sub>3</sub> indeed has a small CB offset [166]. Data by Hattori [178] for La<sub>2</sub>O<sub>3</sub> that agrees well with the prediction of 2.3 eV. La<sub>2</sub>O<sub>3</sub> and LaAlO<sub>3</sub> have a particularly large CB offsets [178,182]. The experimental and calculated vales for Lu<sub>2</sub>O<sub>3</sub> and Gd<sub>2</sub>O<sub>3</sub> are also in reasonable agreement [180]. There is good agreement for Al<sub>2</sub>O<sub>3</sub> made by oxidation [167,168]. For ALD Al<sub>2</sub>O<sub>3</sub> it is important to use the correct phase [108,170].

It is seen that only Zr, Hf, Al, Y, and La oxides have CB offsets over 1 eV, which is the minimum needed to limit electron injection. The CB offsets decrease in the order of group III, IV, to IV metal oxides. This is because the CNL of the oxide rises in the gap along the sequence group III to V.

The MIGS model predictions have been extended to oxides on Ge and on GaAs [185]. The predictions generally agree fairly well with the experimental values, found by either photoemission or internal photoemission.

### 4.5 Bonding at HfO<sub>2</sub>-Si Interfaces

The simple MIGS model of oxide interfaces is surprisingly successful. Nevertheless, it is useful to have a detailed bonding model for direct Si-oxide interfaces. Firstly, the band offset can depend on the interface bonding. Secondly, imperfect interfaces will have defects which can create gap states which trap charge. Third, the control of work functions in the case of metal gates requires this understanding of interface chemistry.

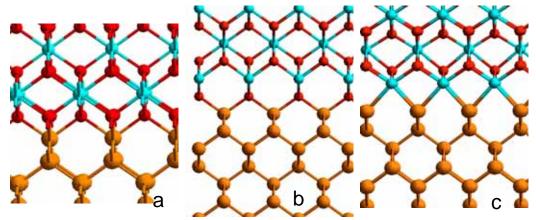

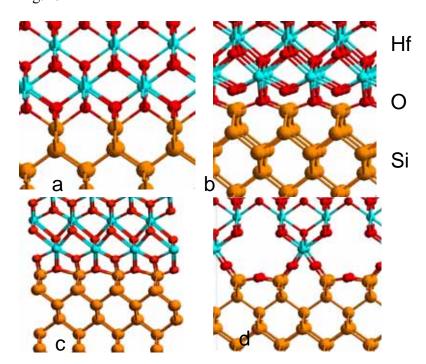

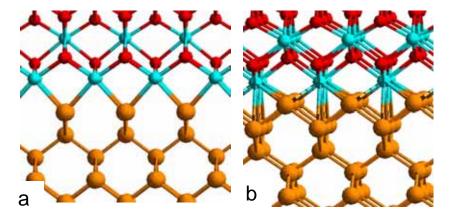

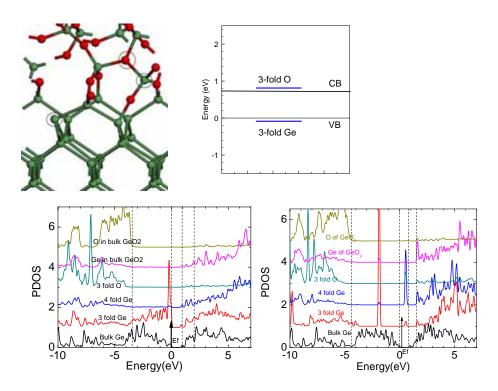

It is necessary to use epitaxial models in order to understand the bonding at these interfaces [187-196]. The Si:HfO<sub>2</sub> system was used as a model, with reasonably a well lattice-matched interface to cubic HfO<sub>2</sub>. The lattice constants of Si and HfO<sub>2</sub> are 5.43Å and 5.12Å respectively. Thus HfO<sub>2</sub> could be grown epitaxially on the Si(100) cube face (as ZrO<sub>2</sub> was [192]), with the HfO<sub>2</sub> cube face lying directly on top of the Si cube face. This is expressed as HfO<sub>2</sub>(100)//Si(100), and with the [001] directions of Si and oxide parallel, that is HfO<sub>2</sub>[001]//Si[001].

The ideal (100) surfaces of  $HfO_2$  are polar, being oxygen terminated. However, we can construct bulk non-polar units of  $HfO_2$  as  $O^2$ - $Hf^{4+}O^{2-}$  (or 'OHfO') units by assigning O's alternately up or down to give non-polar faces [189,190].

The interface should be insulating, with no gap states, otherwise an FET will not work. We can determine which interface configurations are insulating by an electron counting rule. For the ideal Si(100) face (Fig 29b), each Si atom would have two dangling bonds (DBs) [189]. These create states in the gap. If we place a non-polar OHfO unit on this (100)Si face, there will be no reaction, and this will still leave Si DB states in the Si gap. These gap states will create a metallic interface.

If instead we first put an oxygen across the two Si DBs, this forms a Si-O-Si bridge which ties up the DBs and removes their gap states. We can then add non-polar OHfO units on top. A complete HfO<sub>2</sub> lattice can be built up on top of this interface by adding additional non-polar OHfO layers. This interface will have no gap states, and is insulating.

This also works for Hf-termination, Fig 29(c). In this case, the first layer is a HfO unit which is formally Hf<sup>2+</sup>O<sup>2-</sup> and the Hf has two unsatisfied valences. These can make two Hf-Si bonds to the Si DBs. This also gives an insulating interface with all valences satisfied. The two examples show that we can obtain insulating interfaces, if *polar faces* of HfO<sub>2</sub> are used. The three cases of O-rich, non-polar O and Hf terminated interfaces are shown in Fig 29.

Detailed calculations confirm the simplified bonding analysis [190]. Some lower symmetry configurations were also studied. Fig. 30(a) shows the ideal Si:OOHfO interface, with a double oxygen layer at the interface. Here the interfacial oxygens are initially 6-fold coordinated, bonded to two Si's and four Zr's. These interfacial oxygens relax to form the structure shown from two directions in Fig 30(b). Those oxygens lying in the Si-O-Si bridges relax towards the silicon layer. The other two oxygens relax up towards the HfO<sub>2</sub> layer. This interface is denoted the  $O_4$ . Overall, these interfaces have the same number of oxygen atoms at the interface. Another interface denoted  $O_3$  interface is a slightly more stable structure. Finally, an interface shown in Fig 30(c) would be formed by a literal ALD process, but this is less dense and less stable.

The non-polar interface of Fig 29b would be metallic, in a high symmetry configuration. In a doubled unit cell, the interface reconstructs to break symmetry and create a band gap.

For Hf-terminated interfaces, the simplest has 6-fold coordinated Hf<sub>6</sub> sites, as in Fig. 31(a). This structure relaxes so that the interfacial Hf-Si bond becomes longer. This interface is insulating in the full calculation. Fig 31(b) shows another interface in which Hf is 10-fold coordinated,. This bonding is similar to that in  $ZrSi_2$ . This Hf<sub>10</sub> interface is the more stable than the Hf<sub>6</sub> interface by 0.3 eV per interface Si [190].

In summary, the  $O_4$ ,  $O_3$  and  $Hf_6$  interfaces are insulating. They have no states in the Si band gap. The  $Hf_{10}$  interface is metallic, despite formally satisfying the electron counting rule, because it is overcoordinated. Thus, only O-terminated interfaces are useful for devices.

The valence band offsets for the various  $Si:HfO_2$  interface structures can be from the partial density of states of Si and oxide. The conduction band offsets are not given well by the LDA calculations, due to the LDA band gap error. The CB offset is found from the VB offset by adding the experimental band gap. The VB offset for the various O-terminated interfaces of  $ZrO_2$  are found to be similar to the VB offset from from the CNL method. In contrast, the VB offset for Hf-terminated interfaces has a large variation of 0.9 eV between  $Hf_{10}$  and  $Hf_6$ , being much larger for  $Hf_6$ . This is due to a large change in the interface dipole. Summarising, the interface-specific dipole is quite small for the O-terminated interfaces, but large for the Hf-terminated interfaces. These results emphasise how much the interface dipole can depend on termination, and go beyond the MIGS model.

Realistic models of the  $HfO_2:Si(100)$  interface, including interfacial  $SiO_2$  layers, have been created by Gavartin [197], Broqvist [198], and Alkauskas et al [126]. The presence of the  $SiO_2$  does affect the previous band offset values. The Si termination is similar to that expected from ALD reactions.

#### **5** Electronic structure of Defects

# 5.1 HfO<sub>2</sub>

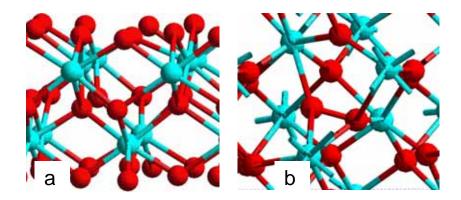

A problem with high K oxides [199] is that they can contain a much higher concentration of defects than in SiO<sub>2</sub>. The two defects in HfO<sub>2</sub> with the lowest formation energy are the oxygen vacancy and the oxygen interstitial, fig 32(a,b), according to Foster et al [200,201]. Metal site defects cost more, because of their higher coordinations.

First, consider the oxygen vacancy in HfO<sub>2</sub>. Recall that the valence band of HfO<sub>2</sub> consists mainly of O p states and the conduction band consists mainly of Hf d states. The electronic structure of the oxygen

vacancy and oxygen interstitial in HfO<sub>2</sub> have been calculated by various groups [200-214, 124,127]. Many used LDA methods. The LDA produces good total energies and structures, but LDA underestimates band gaps, by 30% in the case of HfO<sub>2</sub>. It also gives the wrong localisation of gap states even when filled. To correct for the band gap error, methods which go beyond LDA such as hybrid functional must be used. Xiong [124] used the screened exchange (SX) method to calculate the defect excitation energies for HfO<sub>2</sub> with a 48 atom supercell. The geometry was relaxed in GGA and the energy levels calculated in SX. This was repeated recently for a 96 atom cell. Similar results were later found by Gavartin [211], Broqvist [127], Choi [212] and Lyons [213].

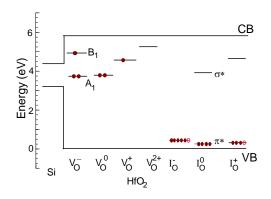

The O vacancy creates singly degenerate gap state of near spherical  $A_1$  symmetry. It is occupied by 2 electrons for the neutral vacancy. The state is strongly localised on the d orbitals of the adjacent Hf ions. In c-HfO<sub>2</sub>, the relaxed neutral vacancy gives a gap state at 3.8 eV above the oxide VB, in Fig 30. The ionic positions do not relax much from their ideal positions in the neutral vacancy, the Hf-Hf distance is 3.59 Å compared to 3.54 Å in bulk HfO<sub>2</sub>.

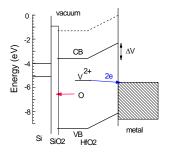

At the positive vacancy,  $V^+$ , the  $A_1$  defect state is now singly occupied. Its net positive charge causes the adjacent  $Hf^{4+}$  ions to relax outwards from the vacancy. The Hf-Hf spacing becomes 3.74 Å. This relaxation causes the defect state to move upwards from 3.2 eV to 4.7 eV, Fig 33. At  $V^{2+}$ , the  $A_1$  state is now empty. The greater positive charge causes further outward relaxation of the Hf ions so the Hf-Hf separation is 3.90 Å and the gap state rises to 5.2 eV.

The vacancy can also trap one or two *electrons* (despite being an anion vacancy). A trapped electron causes the adjacent Hf ions to distort asymmetrically (by the Jahn-Teller effect), pulling down an extra, singly-degenerate state of  $B_1$  symmetry out of the conduction band. It is singly occupied for  $V^2$  and doubly occupied for  $V^2$ . The  $A_1$  state is full in both cases. The complete spectrum of the vacancy levels is summarised in Fig 33.

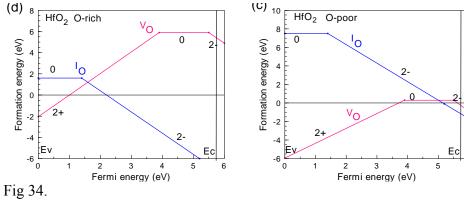

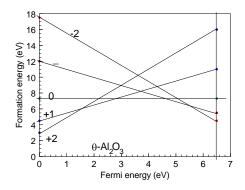

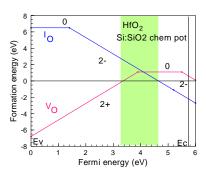

The formation energy of a defect,  $H_q$ , can be calculated as a function of the Fermi energy ( $\Delta E_F$ ) from the valence band edge  $E_V$  and the relative chemical potential ( $\Delta \mu$ ) of element  $\alpha$  [213],

$$H_{q}(E_{F}, \mu) = [E_{q} - E_{H}] + q(E_{V} + \Delta E_{F}) + \sum_{\alpha} n_{\alpha} (\mu_{\alpha}^{0} + \Delta \mu_{\alpha})$$

(17)

where  $(E_q)$  is the total energy for the defect cell with charge q,  $E_H$  is the total energy for the perfect cell,  $q.E_V$  is the change in energy of the Fermi level when charge q is added and  $n_\alpha$  is the number of atoms of species  $\alpha$ . The oxygen chemical potential  $(\mu_O)$  can vary between the O-rich limit which is taken to be that of the  $O_2$  molecule  $\mu_O = 0$  to the O-poor limit which corresponds to the Hf:HfO<sub>2</sub> equilibrium, which is  $\mu(O) = -5.9$  eV, the experimental heat of formation of HfO<sub>2</sub> per O atom [214].

Fig 34(a) shows the defect formation energy of the vacancy vs Fermi energy for the O-rich limit, and for the O-poor limit. At each value of Fermi energy we look for the lowest energy charge state, the most stable. The neutral state is the most stable for  $E_F$  between 3.2 eV and 5.2 eV. Below 3.2 eV, the  $V^{2+}$  is most stable. Above  $E_F = 5.2$  eV, the  $V^{2-}$  and then  $V^{2-}$  become the stable states.

The formation energies for the O-poor limit are simply those for the O-rich limit displaced downwards, Fig 34(b). In the O-poor limit, the cost of an oxygen vacancy is quite small, only 0.8 eV [214]. This is in fact standard. The cost of an O vacancy of any oxide is close to zero in the O-poor limit. The collorary is that the formation energy of an O vacancy in the O rich limit is roughly the bulk heat of formation per O atom.

The other main defect in HfO<sub>2</sub> is the oxygen interstitial [124,201,207,209,214]. It can have various charge states, see Fig 30. The energy levels were calculated using SX [214]. The simplest configuration is the closed shell species  $I^2$ , equivalent to an extra  $O^2$  ion. In this state, the interstitial O is well separated from the other  $O^2$  ions and it adds filled O 2p states to the valence band. At the  $O^2$ , removing 1 electron leaves a hole at the VB edge. This radical anion moves slightly closer to another  $O^2$  without actually forming a full O-O bond, the O-O distance is 2.0Å. The neutral interstitial or  $O^0$  has two holes in the O 2p levels. The two holes allow this interstitial to form a true O-O bond, giving the dumb-bell shaped superoxy anion  $O_2^2$ . The O-O bond length is 1.49Å. This O-O bond creates a filled bonding  $(\sigma)$  orbital at

-6.0 eV just below the main valence band and an empty antibonding ( $\sigma^*$ ) orbital at 4.1 eV in the upper gap region. It also has filled double degenerate  $p\pi$  and  $\pi^*$  orbitals at -3.0 eV in the valence band and at +0.3 eV just above the VB edge (Fig 33). Fig 34 shows the formation energy of the O interstitial for Orich and O-poor conditions.

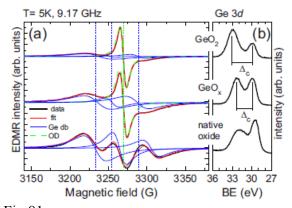

The I<sup>0</sup> could trap a further hole to give the O<sup>+</sup> interstitial, or superoxyl radical. This O<sup>+</sup> ion forms a shorter O-O bond with a O<sup>2-</sup> ion of length 1.39 Å, giving a dumbbell O<sub>2</sub><sup>-</sup> ion. This gives rise to an empty  $\sigma^*$  state in the upper gap at 4.5 eV, (Fig 32). It also has a filled  $\pi$  state and a half-filled  $\pi^*$  state. This O<sub>2</sub><sup>-</sup> ion is called the superoxyl radical. The hole resides in one of the  $\pi^*$  states, breaking their degeneracy. This radical has a characteristic g factor and has been seen by electron spin resonance in HfO<sub>2</sub> thin films [215].

# 5.2 HfO<sub>2</sub> defects: Experimental observations

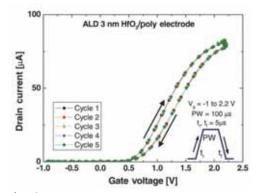

The charge trapping characteristics of  $HfO_2$  defects have been intensively measured. The trapping characteristics follow the same curves on repeated cycles, indicating that traps get filled and emptied, with no new defects created [216,217], Fig 35.

Kerber [218] interpreted the trapping curves as fast trapping and detrapping of electrons in the oxide. and that the trapping data were consistent with an electron trap level lying just above the Si conduction band edge. Using electron detrapping data over a wider temperature range, Mitard [219] gave levels at 0.8 eV and 1.5 eV below the HfO<sub>2</sub> conduction band edge, or more accurately at 0.7 eV and 1.3 eV above the midgap of the underlying Si. Cartier [220] noted that the levels measured by 'amplitude charge pumping' (ACP) agreed well with the calculated energy levels of the O vacancy, and that their density correlated with the oxygen deficiency for variously prepared samples. The energy spectra of the traps can also be derived by inelastic tunnelling spectroscopy [221], charge pumping and CV methods [222]. The density of levels found by ACP correlated linearly with bias stress voltage change measured on differently prepared gate oxides. This indicates that the O vacancy is the primary cause of the charge trapping instability in HfO<sub>2</sub>.

Optically, Takeuchi [223] identified an absorption band at 4.5 eV in spectroscopic ellipsometry on  $HfO_2$  films oxidised to different degrees. They attribute this to transitions from the valence band to an oxygen vacancy level at 4.5 eV. The peak was seen in optical absorption by Nyugen [224]. The transition was seen by cathodo-luminescence in  $HfO_2$  films by Walsh [225]. There was concern that the absorption band might correspond to the E2 absorption of the underlying Si substrate, but the other spectroscopic tools suggest that the identification with the vacancy still holds.

The oxygen vacancy is the main mechanism for oxygen diffusion in HfO<sub>2</sub> and related oxides, so there have been a number of efforts to correlate vacancy concentrations as a function of oxygen partial pressure by Guha [226,227], McIntyre [228], and of oxygen diffusion measurements by Zafar [229].

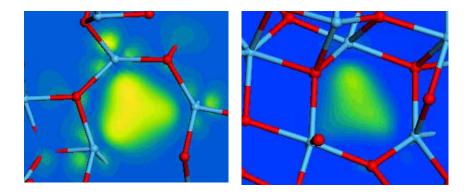

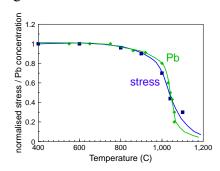

The chemical nature of the traps can usually be determined directly by electron spin resonance (ESR). So far, many of the defects seen by ESR in  $HfO_2$  on Si have been related to the interfacial Si dangling bond, the so-called the  $P_b$  centre [230,231]. Kang [215] identified two paramagnetic defects in bulk  $HfO_2$  produced by ALD; the  $Hf^{3+}$  ion (an electron trapped at  $Hf^{4+}$  or  $V^+$ ) and the superoxy radical. The problem with the ESR data for the O vacancy is that the observed ESR g matrix has an axial symmetry [232] which does not fit the expected spherical symmetry of an  $A_1$  state. However, it is now realised that LDA gives defect wavefunctions that are too delocalised. Fig. 36(a) shows the symmetric wavefunction found by LDA. If hybrid functionals such as B3LYP or SX are used instead, these methods find a more localised wavefunction and lower symmetry defect, as seen in Fig 36(b), and this is now consistent with the experimental ESR signature [233,208].

The conduction processes in insulating thin films can be classified as limited by bulk or interface processes. Bulk processes include hopping through traps (Poole-Frenkel) and space-charge limited current (SCLC). For HfO<sub>2</sub> and ZrO<sub>2</sub>, Poole-Frenkel hopping may be dominant for thicker films, over 4 nm. For thinner films, Houssa [234] attributes conduction to trap-assisted tunnelling (TAT). Tunnelling

should be essentially independent of temperature, hopping T-dependent. The technologically relevant films of  $HfO_2$  tend to be only 2-3 nm thick. In this range, TAT occurs for V<0.5V [48, 235], and direct tunnelling occurs for higher voltages. In all cases, conduction is by electrons, because the CB barrier is lower. The relevant traps are the oxygen vacancy levels.

#### **5.3 Defect Passivation**

The defect densities in  $HfO_2$  can be reduced by passivation. The standard method to passivate dangling bond type defects in covalent semiconductors or  $SiO_2$  is a forming gas anneal in hydrogen. The hydrogen ties off the dangling bond, and moves the states out of the gap.  $HfO_2$  is different, it has ionic bonds and the defects are not dangling bonds. Different strategies are now required.

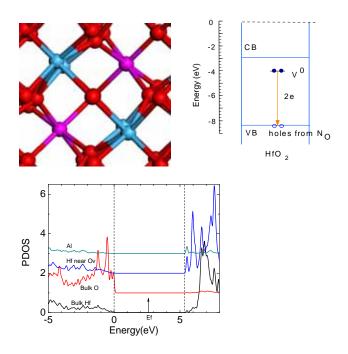

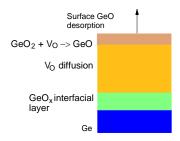

Annealing in ammonia or nitrogen was found to lower leakage currents, which might be realted to lowering the defect density. Umezawa [236] noted a possible mechanism of nitrogen passivation of O vacancies in which two nitrogens substituted for oxygen next to a neutral oxygen vacancy,  $VN_2$ , removed the vacancy–related gap state. The passivation occurs because each substitutional N would leave a hole in the VB (Fig 37b), so the two electrons of  $V^0$  fall into the hole states, making an effective doubly postively charged vacancy [202]. The Hf ions adjacent to the vacancy relax outwards, as in the simple  $V^{2+}$ , but here the relaxation repels the  $A_1$  level completely out of the gap, Fig 37(a). The configuration now has a 'closed shell', so it should not give rise to gap states, Fig 37(c).

Gavartin [237] studied other configurations of N in HfO<sub>2</sub>. These configurations still give gap states, so they are not passivating the defects. Nitrogen introduces N 2p states in the lower gap, which lie above the normal valence band edge [238], so this reduces the local band gap. However, the valence band offset is large, so this does not have a deleterious effect.

The vacancy can also be passivated by the substitution of two Hf sites by a trivalent metal such as La [239,240] (Fig 38). In this case, two La ions are substituting for two Hf ions, next to the O vacancy. The two trivalent La sites lead to two holes in the valence band, into which the two electrons of the neutral vacancy fall. As above for N, this leaves a closed shell and a  $V^{2+}$  vacancy. As in the case of nitrogen above, the relaxed  $V^{2+}$  pushes its  $A_1$  state up out of the gap, into the conduction band. Both these methods can be used to improve the reliability of  $HfO_2$ .

Fluorine passivation has also been found to be beneficial by Tseng [241] and McIntyre [242], probably because F might insert into oxygen vacancies. According to calculations, the F lies in the vacancy, and repels any vacancy states into the oxide conduction band, thereby passivating the vacancy [243] (Fig 34). However, a disadvantage is that too much fluorine will lower K.

It turns out that many inpurirites and defects can be passivated in  $HfO_2$  because of the nature of wide band gap systems [244].

# 5.4 Defects in Al<sub>2</sub>O<sub>3</sub>

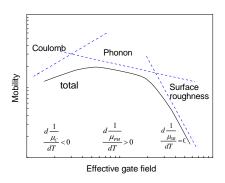

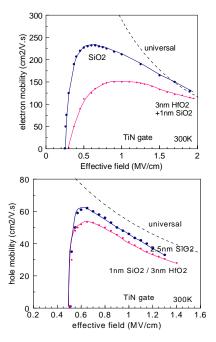

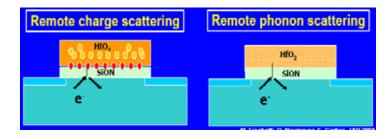

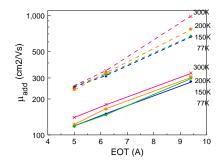

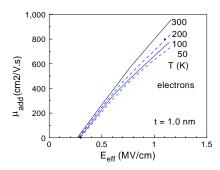

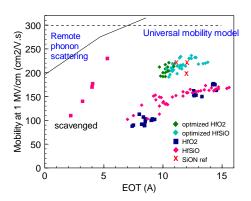

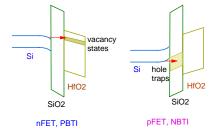

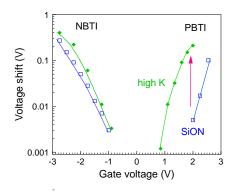

Al<sub>2</sub>O<sub>3</sub> is the other widely used high K oxide. This is partly because of its ability to remain amorphous, and partly because it is a good atomic diffusion barrier. It is widely known to have a fairly high concentration of defect states. This can be advantageous for some memory applications.