# All Ink-Jet Printed Low-Voltage Organic Field-Effect Transistors on Flexible Substrate

Linrun Feng<sup>1,†,§</sup>, Chen Jiang<sup>2,§</sup>, Hanbin Ma<sup>2</sup>, Xiaojun Guo<sup>1\*</sup> and Arokia Nathan<sup>2\*</sup>

<sup>1</sup>National Engineering Lab for TFT-LCD Materials and Technologies, Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, People's Republic of China

<sup>2</sup>Department of Engineering, University of Cambridge, 9 JJ Thomson Avenue, Cambridge CB3 0FA, United Kingdom

<sup>†</sup>Visiting with Department of Engineering, University of Cambridge, 9 JJ Thomson Avenue, Cambridge CB3 0FA, UK

## Abstract

In this work, all ink-jet printed (IJP) low-voltage organic field-effect transistors (OFETs) on flexible substrate are reported. The OFETs use IJP silver (Ag) for source/drain/gate electrodes, poly(4-vinylphenol) (PVP) for gate dielectric, 6,13-bis(triisopropylsilylethynyl)-pentacene (TIPS-pentacene) blended with polystyrene (PS) as the semiconducting layer and CYTOP for encapsulation layer. All the printing processes were carried out in ambient air environment using a single laboratory ink-jet printer Dimatix DMP-2831. The all IJP device presents state-of-the-art performance with low operation voltage down to 3 V, small subthreshold swing (SS) of 0.155 V/decade, mobility of 0.26 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, threshold voltage ( $V_{th}$ ) of -0.17 V and on/off ratio of  $3.1 \times 10^5$ , along with a yield of 62.5%. Through interface engineering and proper process optimization, this work demonstrates a promising low-voltage all IJP device platform for low-cost flexible printed electronics.

### Keywords

Organic field effect transistors (OFETs); all ink-jet printed TFTs; low-voltage operation

§: Linrun Feng and Chen Jiang contributed equally to this work.

\*Corresponding authors E-mail: <u>x.guo@sjtu.edu.cn</u> E-mail: <u>an299@cam.ac.uk</u>

### 1. Introduction

Solution processed organic field-effect transistors (OFETs) have received considerable attention, owing to their attractive features of low-cost printable processes [1]-[2], superior intrinsic mechanical flexibility [3], and sustainable performance improvement [4]. These fascinating features of OFETs make them perfect candidates for applications as sensors [5], radio frequency identification (RFID) tags [6], smart memories [7], point-of-care diagnostic systems [8], flexible display backplanes [9] and wearable systems [10]. In the past few decades, apart from developing high mobility organic semiconductors [11], significant efforts focused on developing low-cost solution-based processes for OFETs [12]-[14], with ink-jet printing as one of the most promising candidates. Its merits include drop-on-demand direct patterning, non-contact mode, material saving and good compatibility with large area flexible substrates [15], all of which are highly desirable for low-cost and high-throughput electronics [16]-[19]. To further reduce the cost and improve the efficiency for OFETs' manufacturing, an all ink-jet printed (IJP) OFET device platform is highly very much in demand. Up to now, there have been very few publications on all IJP-OFETs [20]-[23]. Most demonstrate high operating voltage of typically a few tens of volts, which would be a bottleneck for most mobile or wearable applications where the electronics have to be powered with battery or AC field. Therefore, reducing the operating voltage of all IJP-OFETs has become a key challenge.

To reduce the operating voltage, we can increase the gate dielectric capacitance per unit area ( $C_i$ ) [24] and/or reduce the semiconductor/dielectric interface trap density ( $N_{SS}$ ) [25]. The larger  $C_i$  can be achieved by ultrathin or high-*k* gate dielectric. However, a thin gate dielectric can result in large gate leakage and a high-*k* gate dielectric would suffer from the interface dipole disorder [26], neither of which are compatible in all IJP-OFETs. For an all IJP-OFET, a bottom-gate bottom-contact (BGBC) device architecture is preferred [20]-[23], which prints source/drain electrodes on the dielectric layer rather than the process-sensitive semiconductor layer. In previous work, it has been shown that a reduced  $N_{SS}$  can be achieved with BGBC device architecture by using a blend of small molecule organic semiconductor and polymer binder [25][27]-[30]. Such an approach would be more compatible with ink-jet printing processes, which provides more flexibility on the dielectric thickness and dielectric constant (*k*) of the gate insulator. In addition, a higher mobility of IJP TIPS-pentacene OFET can be also achieved by blending with insulating polymer [31].

In this work, we adopt the approach of reducing  $N_{SS}$  and show that it is effective. Based on a small molecule organic semiconductor blended with polymer dielectric material system, combining with careful process optimization, a low-voltage (< 3 V) all IJP-OFETs on flexible polyethylene naphthalate (PEN) substrate is reported. This work shows the first time through interface engineering and proper process optimization, all IJP low-voltage OFETs on flexible substrate can be achieved in ambient air lab environment.

#### 2. Experimental

(a)

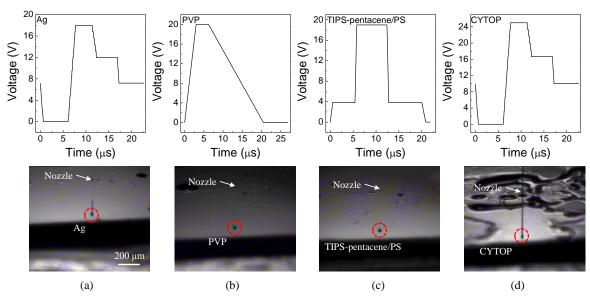

Fig. 2 Controlling voltage waveform for the ink-jet printing process and photograph of the ink-jetted drops from nozzle for (a) Ag, (b) PVP, (c) TIPS-pentacene/PS and (d) CYTOP.

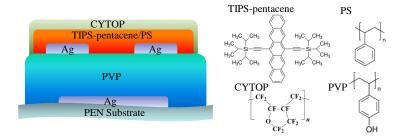

The device structure of the all IJP-OFETs and the chemical structure of the used materials are shown in Fig. 1 (a) and (b), respectively. The BGBC devices were fabricated on a 125-µm-thick PEN substrate from DuPont. The size of the PEN was 4 cm  $\times$  4 cm. The Ag ink (jet-600C) was supplied by Hisense Electronics, Kunshan, China, and the CYTOP (CTL-809M) and its solvent (CT-Solv. 180) were provided by Asahi Glass. All other chemicals were purchased from Sigma-Aldrich. The poly(4-vinylphenol) (PVP) was dissolved in propylene glycol monomethyl ether acetate (PGMEA) at a concentration of 80 mg/mL. Subsequently, the cross-linking reagent poly(melamine-co-formaldehyde) (PMF) was mixed into the solution at a mass ratio of 1:2 to PVP. The mixed solution was then used as ink for the dielectric layer. We used a cross-linkable PVP dielectric as it has been proven to be a suitable gate dielectric for ink-jet printing process, and frequently used in the all IJP-OFETs [20]-[23]. The ink of semiconductor layer was prepared by mixing 6,13-bis(triisopropylsilylethynyl)-pentacene (TIPS-pentacene) and polystyrene (PS) at 10 mg/mL concentration of solids in toluene (3:1 ratio by volume). The blended material system (TIPS-pentacene/PS) appears to reduce  $N_{\rm SS}$  [25]. The CYTOP was diluted with a mass ratio of 1:3 to the CYTOP solvent (CT-Solv. 180), and then used as the ink for the encapsulation layer. By careful optimization of the controlling voltage waveform, nice ink-jetted drops out of the nozzle were achieved, as shown in Fig. 2. During the printing, the temperature of the cartridge for Ag, PVP, TIPS-pentacene/PS and CYTOP were 45°C, 35°C, 40°C and 50°C, respectively. The ink-jetted drops shown in Fig. 2 were the prerequisite for device fabrication. All the ink-jet printing processes were conducted with Dimatix DMP-2831 with 10 pL cartridges. The DMP-11610 cartridge was used for Ag ink, and DMPLCP-11610 cartridges were used for the other inks.

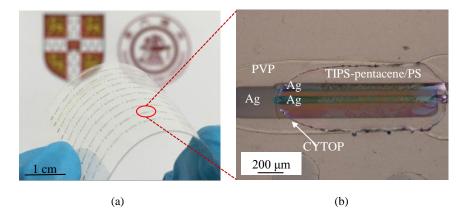

Fig. 3 (a) Photograph of fabricated flexible sample. (b) Polarized optical micrograph of the fabricated device.

The Ag gate electrode was printed onto the PEN substrate at a drop space ( $D_{\rm S}$ ) of 50 µm. The drop frequency  $(D_{\rm F})$  and the drop height  $(D_{\rm H})$  from the cartridge nozzle to the top surface of the substrate were 5 kHz and 1 mm, respectively. In all the ink-jet printing processes, the temperature of the printer plate was kept at 30°C. The IJP-Ag was annealed at 150°C for 15 min to form conductive electrodes. Then the sample was treated by ultraviolet/ozone (UV/O<sub>3</sub>) for 6 min before printing the PVP dielectric. To avoid the interaction between neighboring PVP lines, a single PVP line was used to cover the whole Ag gate electrode by reducing the  $D_{\rm S}$ . The  $D_{\rm S}$ ,  $D_{\rm F}$  and  $D_{\rm H}$  for all-printed PVP were 5  $\mu$ m, 5 kHz and 1 mm, respectively. The PVP dielectric layer was cross-linked at 150°C for 120 min. For the subsequent the source/drain electrode formation, the Ag ink was printed on PVP surface with the same jetting and annealing parameters as the gate electrode. The channel width (W) and length (L) were 1200 µm and 40 µm, respectively. The surfaces of the source/drain electrodes were then treated by immersing the samples into a  $7.5 \times 10^{-3}$  mol/L solution of perfluorobenzenethiol (PFBT) in ethanol for 3 min and then rinsed with ethanol. The PFBT surface treated Ag electrodes were shown to be able to form good contacts with p-type organic semiconductors [32]. The semiconductor layer was then printed with a  $D_{\rm s}$ of 5  $\mu$ m, a  $D_{\rm F}$  of 2 kHz and a  $D_{\rm H}$  of 1 mm, followed by an annealing process at 100 °C for 30 min. Finally, the CYTOP ink was printed as the encapsulation layer. The  $D_{\rm S}$ ,  $D_{\rm F}$  and  $D_{\rm H}$  for CYTOP were 5 μm, 2 kHz and 1 mm, respectively. After the process of printing the encapsulation layer, the sample was heated at 100 C for 30 min before measurements. The photograph of the sample and the polarized optical micrograph of the device are shown in Fig. 3 (a) and (b), respectively.

In this work, all the printing processes and measurement were carried out in a non-cleanroom, ambient-air environment. The electrical properties of the devices were characterized with a Keithley 4200 Semiconductor Characterization System. The surface roughness of the PVP film was recorded with a Veeco EnviroScope atomic force microscope. The thickness was measured with a Dektak surface profilometer. The wetting property of PVP surface was characterized by a video contact-angle analyzer SL200B. The polarized optical micrographs were taken with a Nikon Eclipse ME600. The UV/ $O_3$  treatment was carried out with a Bioforce Nanosciences Procleaner 220.

## 3. Results and discussions

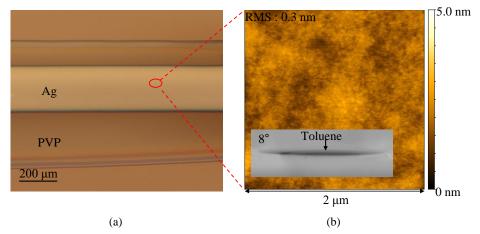

Fig. 4 (a) Optical micrograph of the device with IJP-PVP dielectric on Ag gate electrode. (b) Measured atomic force micrograph (AFM) image of the PVP film. Measured toluene contact angle of the film is shown in inset.

As shown in Fig. 4 (a), the single IJP-PVP line covers the whole Ag gate electrode, which is thought to be beneficial for a smooth surface of dielectric to avoid possible interaction between neighboring PVP lines. The measured atomic force micrograph (AFM) image of the PVP film is shown in Fig. 4 (b). It shows a very smooth surface with a root mean square (RMS) roughness of about 0.3 nm. The smooth surface is very important for forming a high quality semiconductor/dielectric interface. Meanwhile, the strong wetting property of the semiconductor solvent (toluene in this work) on the PVP surface is also essential in bottom-gate OFETs [33], as shown in the inset of Fig. 4 (b). Through careful interface engineering, a high-quality semiconductor/dielectric interface is obtained, which is prerequisite to reduce  $N_{SS}$ .

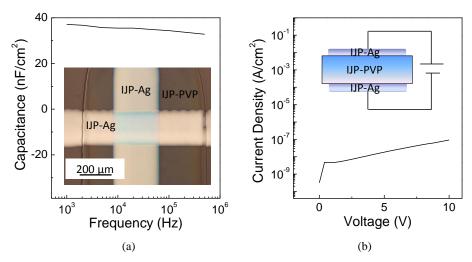

Fig. 5 (a) Measured capacitance as a function of frequency and (b) leakage current density as a function of voltage for the IJP-PVP dielectric. Optical micrograph and schematic diagram of the test structure Ag/PVP/Ag are shown in the insets of (a) and (b), respectively.

The capacitance as a function of frequency for IJP-PVP dielectric is presented in Fig. 5 (a). The  $C_i$  is measured to be 37.0 nF/cm<sup>2</sup> at a frequency of 1 kHz. The measured thickness is 103 nm yielding a dielectric constant *k* of 4.3 at 1 kHz. The leakage current density is shown in Fig. 5 (b), with a value of

$2.3 \times 10^{-7}$  A/cm<sup>2</sup> at a bias voltage of 10 V. The optical micrograph and schematic diagram of the test structure are shown as insets in Fig. 5 (a) and (b), respectively.

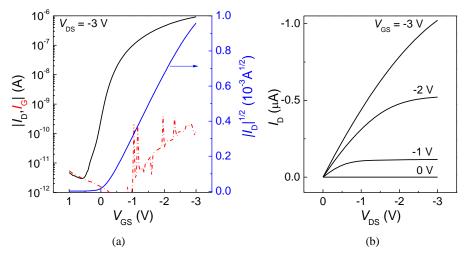

Fig. 6 Measured electrical characteristics of the fabricated OFETs: (a) transfer characteristics ( $I_D$ - $V_{GS}$ ) and (b) output characteristics ( $I_D$ - $V_{DS}$ ).

Figure 6 shows the measured transfer  $(I_{\rm D}-V_{\rm GS})$  and output  $(I_{\rm D}-V_{\rm DS})$  electrical characteristics of the fabricated OFETs. The device presents a threshold voltage  $(V_{\rm th})$  of -0.17 V, mobility of 0.26 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, an on/off ratio of 10<sup>5</sup>-10<sup>6</sup> with a small subthreshold swing (SS) of 0.155 V/decade. The  $V_{\rm th}$  value was estimated through a linear fit of the square root of  $I_{\rm D}$  versus  $V_{\rm GS}$  plot with its intercept on the *x*-axis as illustrated in Fig. 6 (a). The mobility was calculated by fitting the plot of the square root of  $I_{\rm D}$  versus  $V_{\rm GS}$  using the following equation:

$$I_{\rm D} = \frac{\mu C_{\rm i} W}{2 \rm L} (V_{\rm GS} - V_{\rm th})^2$$

(1)

where  $\mu$  is the mobility, L the channel length, W the channel width and  $C_i$  the gate dielectric capacitance per unit area. To the best of our knowledge, this is the first report of low operating voltage for an all IJP-OFET is achieved.

The required voltage swing to switch OFETs is highly dependent on the subthreshold swing (SS), which can be described as [34]:

$$SS = \ln 10 \cdot \frac{k_B T}{q} \cdot \left(1 + \frac{q^2 N_{\rm SS}}{C_{\rm i}}\right) \tag{2}$$

where  $k_{\rm B}$  is Boltzman's constant, T the absolute temperature,  $N_{\rm SS}$  the semiconductor/dielectric interface trap density, q the elementary charge, and  $C_{\rm i}$  the gate dielectric capacitance per unit area. According to equation (2), since  $k_{\rm B}T/q$  is a constant, the required operating voltage for the OFET depends on both the  $C_{\rm i}$  and  $N_{\rm SS}$ . A larger  $C_{\rm i}$  and a lower  $N_{\rm SS}$  are preferred for low-voltage operation.

| other reported all DF-OFE IS. |             |                       |                      |                   |                     |             |            |                       |

|-------------------------------|-------------|-----------------------|----------------------|-------------------|---------------------|-------------|------------|-----------------------|

| Work                          | Substrate   | $C_{\mathrm{i}}$      | Mobility             | $V_{\mathrm{th}}$ | Highest             | Operation   | SS         | N <sub>SS</sub>       |

|                               |             | (nF/cm <sup>2</sup> ) | $(cm^2V^{-1}s^{-1})$ |                   | On/off Ratio        | Voltage (V) | (V/decade) | $(eV^{-1}cm^{-2})$    |

| [20]                          | Polyarylate | 3.8                   | 0.02                 | -1.2              | $10^{4}$            | 60          | 2.52       | $9.80 \times 10^{11}$ |

| [21]                          | PEN         | 2.4                   | 0.02                 | -14.0             | $1.2 \times 10^{2}$ | 30          | N/A        | N/A                   |

| [22]                          | Wafer       | 33.8                  | 0.01                 | -1.5              | $1.4 \times 10^{3}$ | 40          | 4.28       | $1.50 \times 10^{13}$ |

| [23]                          | PEN         | 5.3                   | 0.00025              | -3.5              | $2.0 \times 10^{2}$ | 30          | N/A        | N/A                   |

| Our work                      | PEN         | 37.0                  | 0.26                 | -0.17             | 3.1×10 <sup>5</sup> | 3           | 0.155      | 3.70×10 <sup>11</sup> |

Table 1 Comparison of substrate,  $C_i$ , mobility,  $V_{th}$ , highest on/off ratio, operation voltage, SS and  $N_{SS}$  for this work and other reported all IIP-OFETs

N/A: Not available.

A systematic comparison of extracted device parameters for devices in this work and all IJP-OFETs reported in the literature is shown in Tab. 1. It can be seen that that the overall performance of the devices reported here is very promising. The value of  $N_{\rm SS}$  is calculated to be  $3.70 \times 10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup>, which is also the lowest value reported for all IJP-OFETs. We believe that the reduced  $N_{\rm SS}$  and larger  $C_{\rm i}$  as listed in Tab. 1 are the main reasons for the reduced operating voltage of our OFETs.

In earlier reports on all IJP-OFETs [20]-[23], thick dielectrics were usually used to avoid dielectric breakdown, which yield a small  $C_i$ . Meanwhile, the small-molecule-only semiconductor system used in these papers [20]-[23] suffers from a relatively high  $N_{\rm SS}$  due to the poor crystallization control during the ink-jet printing process. As a result, the operating voltages tend to be very high (>30V). Meanwhile reports have demonstrated that a blend of small molecule organic semiconductor and polymer binder is useful to reduce the  $N_{\rm SS}$  [25][27]-[30], due to the better semiconductor crystallization induced by vertical phase separation [35]. The different solubility parameters between small molecule organic semiconductor and polymer binder is responsible for the vertical phase separation [35]-[36]. This approach for low-voltage operation is more compatible with low-cost printing processes, since there is less strict requirement on the value of  $C_i$ . Moreover, the low-voltage operating property also decreases the likelihood of dielectric breakdown by virtue of lower gate electric field, thus providing a much wider process window of IJP dielectrics. These attributes open up the possibility of realizing low-voltage all IJP-OFETs by reducing the interface state density. To make this approach effective, a smooth surface and proper wetting property of the dielectric are very important. In this work, the strong wetting property of the PVP dielectric shown in the inset of Fig. 4 (b), is consistent with earlier reports [20]-[23]. Moreover, the smooth surface of the PVP dielectric is achieved through the method of single-line printing with a small  $D_s$ , as shown in Fig. 4 (b). A smooth surface is important for low voltage operation since surface/interface roughness hinder charge transport through additional scattering and by increasing defect states at the interface.

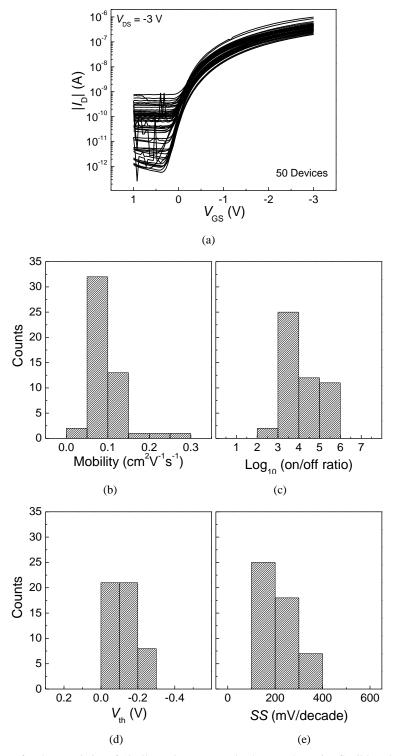

Finally, the transfer characteristics of 50 OFETs are shown in Fig. 7 (a). The devices are classified as failures when the on/off ratio is lower than 500. The yield is 62.5% (i.e. 50 out of 80 functional) for the all IJP-OFETs over 4 cm  $\times$  4 cm size flexible substrate. The histograms of the extracted mobility, on/off ratio,  $V_{th}$  and SS for the 50 OFETs are also shown in Fig. 7. The low on/off ratio of the failed devices is attributed to the printing misalignment, and also the gate leakage. The yield can be improved by using an industry-standard ink-jet printer and a thicker gate dielectric in the future work. Considering that all processes were carried out in a non-cleanroom ambient-air environment using a single Dimatix DMP-2831, the results shown are very encouraging.

Fig. 7 (a) Measured transfer characteristics of 50 all IJP-OFETs over the 4 cm  $\times$  4 cm size flexible substrate. Histograms of 50 all IJP-OFETs over the 4 cm  $\times$  4 cm size flexible substrate: (b) mobility, (c) on/off ratio, (d) threshold voltage and (e) subthreshold swing.

### 4. Conclusion

With proper device architecture, material selection and process optimization, this work demonstrates that low-voltage OFETs can be achieved using low-cost printing processes. The approach of reducing the interface state density at the semiconductor/gate dielectric interface proved to be effective in reducing the OTFTs operating voltage. Since all the processes were carried out in non-cleanroom ambient-air environment using a single laboratory printer (Dimatix DMP-2831), and not exceeding a process temperature of 150°C, this work would open a new route for development of commercially viable printed OFET technology platform for low-cost, low-power, flexible electronics.

#### Acknowledgement

The authors wish to thank the China Scholarship Council for supporting Linrun Feng for a one-year study at the University of Cambridge.

#### Reference

- [1] R. A. Street, Thin-film transistors, Adv. Mater. 21 (2009) 2007-2022.

- [2] H. Klauk, Organic thin-film transistors, Chem. Soc. Rev. 39 (2010) 2643-2666.

- [3] M. Kaltenbrunner, T. Sekitani, J. Reeder, T. Yokota, K. Kuribara, T. Tokuhara, et al., Nature 499 (2013) 458-463.

- [4] H. Sirringhaus, Organic field-effect transistors: The path beyond amorphous silicon, Adv. Mater. 26 (2014) 1319-1335.

- [5] Y. Guo, G. Yu, Y. Liu, Functional organic field-effect transistors, Adv. Mater. 22 (2010) 4427-4447.

- [6] B. K. C. Kjellander, W. T. T. Smaal, K. Myny, J. Genoe, W. Dehaene, P. Heremans, Optimized circuit design for flexible 8-bit RFID transponders with active layer of ink-jet printed small molecule semiconductors, Org. Electron. 14 (2013) 768-774.

- [7] K. Myny, S. Smout, M. Rockele´, A. Bhoolokam, T. H. Ke, S. Steudel, et al., A thin-film microprocessor with inkjet print-programmable memory, Sci. Rep.4 (2014) 7398.

- [8] M. Zhang, C. Liao, C. H. Mark, P. You, C. L. Mark, F. Yan, Highly sensitive glucose sensors based on enzyme-modified whole-graphene solution-gated transistors, Sci. Rep.5 (2015) 8311.

- [9] I. Yagi, N. Hirai, Y. Miyamoto, M. Noda, A. Imaoka, N. Yoneya, et al., A flexible full-color AMOLED display driven by OTFTs, J. Soc. Inf. Display 16 (2008) 15-20.

- [10] B. C. K. Tee, A. Chortos, A. Berndt, A. K. Nguyen, A. Tom, A. McGuire, et al., A skin-inspired organic digital mechanoreceptor, Science 350 (2015) 313-316.

- [11] J. Li, Y. Zhao, H. S. Tan, Y. Guo, C. Di, G. Yu, et al., A stable solution-processed polymer semiconductor with record high-mobility for printed transistors, Sci. Rep.2 (2012) 754.

- [12] S. Hunter, J. W. Ward, M. M. Payne, J. E. Anthony, O. D. Jurchescu, T. D. Anthopoulos, Low-voltage polymer/small-molecule blend organic thin-film transistors and circuits fabricated via spray deposition, Appl. Phys. Lett. 106 (2015) 223304

- [13] A. Pierre, M. Sadeghi, M. M. Payne, A. Facchetti, J. E. Anthony, A. C. Arias, All-printed flexible organic transistors enabled by surface tension-guided blade coating, Adv. Mater. 26 (2014) 5722-5727.

- [14] J. Chang, C. Chi, J. Zhang, J. Wu, Controlled growth of large-area high-performance small-molecule organic single-crystalline transistors by slot-die coating using a mixed solvent system, Adv. Mater. 25 (2013) 6442-6447.

- [15] M. Singh, H. M. Haverinen, P. Dhagat, G. E. Jabbour, Inkjet printing process and its applications, Adv. Mater. 21 (2009) 1-13.

- [16] W. Tang, L. Feng, J. Zhao, Q. Cui, S. Chen, X. Guo, Inkjet printed fine silver electrodes for all solution processed low-voltage organic thin film transistors, J. Mater. Chem. C. 2 (2014) 1995-2000.

- [17] K. Fukuda, Y. Takeda, M. Mizukami, D. Kumaki, S. Tokito, Fully solution processed flexible organic thin film transistor arrays with high mobility and exceptional uniformity, Sci. Rep. 4 (2014) 3947.

- [18] Y.H. Kim, B. Yoo, J.E. Anthony, S.K. Park, Controlled deposition of a high performance small-molecule organic single-crystal transistor array by direct ink-jet printing, Adv. Mater. 24 (2012) 497-502.

- [19] B.K.C. Kjellander, W.T.T. Smaal, J.E. Anthony, G.H. Gelinck, Inkjet printing of TIPS-PEN on soluble polymer insulating films: A route to high-performance thin-film transistors, Adv. Mater. 22 (2010) 4612-4616.

- [20] S. Chung, S.O. Kim, S.K. Kwon, C. Lee, Y. Hong, All-inkjet-printed organic thin film transistor inverter on flexible plastic substrate, IEEE Electron Device Lett. 32 (2011) 1134-1136.

- [21] E. Sowade, K. Y. Mitra, E. Ramon, C. M. Domingo, F. Villani, F. Loffredo, Up-scaling of the manufacturing of all-inkjet-printed organic thin-film transistors: Device performance and manufacturing yield of transistor arrays, Org. Electron. 30 (2016) 237-246.

- [22] H.-Y. Tseng, V. Subramanian, All inkjet-printed, fully self-aligned transistors for low-cost circuit applications, Org. Electron. 12 (2011) 249-256.

- [23] M. Medina-Sanchez, C. Martínez-Domingo, E. Ramon, A. Merkoçi, An inkjet-printed field-effect transistor for label-free biosensing, Adv. Funct. Mater. 24 (2014) 6291-6302.

- [24] J. Li, Z. Sun, F. Yan, Solution processsable low-voltage organic thin film transistors with high-k relaxor ferroelectric polymer as gate insulator, Adv. Mater. 24 (2012) 88-93.

- [25] L. Feng, W. Tang, X. Xu, Q. Cui, X. Guo, Ultralow-voltage solution processed organic transistors with small gate dielectric capacitance, IEEE Electron Device Lett. 34 (2013) 129-131.

- [26] J. Veres, S. D. Ogier, S. W. Leeming, D. C. Cupertino, S. M. Khaffaf, Low-k insulators as the choice of dielectrics in organic field-effect transistors, Adv. Func. Mater. 13(2003) 199–204.

- [27] L. Feng, W. Tang, J. Zhao, R. Yang, W. Hu, Q. Li, et al., Unencapsulated air-stable organic field effect transistors by all solution processes for low power vapor sensing, Sci. Rep. 6 (2016) 20671.

- [28] L. Feng, J. V. Anguita, W. Tang, J. Zhao, X. Guo, S. R. P. Silva, Room temperature grown high-quality polymer-like carbon gate dielectric for organic thin-film transistors, Adv. Electron. Mater. in print (2016).

- [29] W. Tang, L. Feng, P. Yu, J. Zhao, X. Guo, Highly efficient all-solution-processed low-voltage organic transistor with a micrometer-thick low-k polymer gate dielectric layer, Adv. Electron. Mater. in print (2016).

- [30] S. Li, L. Feng, X. Guo, Q. Zhang, Application of thermal azide-alkyne cycloaddition (TAAC) reaction as a low temperature cross-linking method in polymer gate dielectrics for organic field-effect transistors, J. Mater. Chem. C. 2 (2014) 3517-3520.

- [31] X. Li, W. T. T. Smaal, C. Kjellander, B. Van Der Putten, K. Gualandris, E. C. P. Smits, J. Anthony, D. J. Broer, P. W. M. Blom, J. Genoe, G. Gelinck, Charge transport in high-performance ink-jet printed single-droplet organic transistors based on a silylethynyl substituted pentacene/insulating polymer blend, Org. Electron. 12(2011) 1319-1327.

- [32] J. P. Hong, A. Y. Park, S. Lee, J. Kang, N. Shin, D. Y. Yoon, Tuning of Ag work functions by self-assembled monolayers of aromatic thiols for an efficient hole injection for solution processed triisopropylsilylethynyl pentacene organic thin film transistors, Appl. Phys. Lett. 92 (2008) 143311.

- [33] J. A. Lim, W. H. Lee, D. Kwak, K. Cho, Evaporation-induced self-organization of inkjet-printed organic semiconductors on surface-modified dielectrics for high-performance organic transistors, Langmuir 25 (2009) 5404.

- [34] W. L. Kalb, B. Batlogg, Calculating the trap density of states in organic field-effect transistors from experiment: A comparison of different methods, Phys. Rev. B. 81 (2010) 035327.

- [35] J. Kang, N. Shin, D. Y. Jang, V. M. Prabhu, D. Y. Yoon, Structure and properties of small molecule-polymer blend semiconductors for organic thin film transistors, J. Am. Chem. Soc. 130 (2008) 12273-12275.

- [36] S. Y. Cho, J. M. Ko, J. Lim, J. Y. Lee, C. Lee, Inkjet-printed organic thin film transistors based on TIPS-pentacene with insulating polymers, J. Mater. Chem. C. 1 (2013) 914-923.