# A no-thin-air memory model for programming languages

# Jean Yves Alexis Pichon-Pharabod Trinity Hall University of Cambridge

September 2017

This dissertation is submitted for the degree of Doctor of Philosophy

# Declaration

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text.

It is not substantially the same as any that I have submitted, or, is being concurrently submitted for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my dissertation has already been submitted, or, is being concurrently submitted for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text.

This thesis does not exceed 60,000 words.

The introduction is based on Pichon-Pharabod and Sewell [65] and Batty et al. [12]. Chapters 3 and 4 are based on Pichon-Pharabod and Sewell [65]. Chapters 6, 7, 8 and 9 are partly based on it too. The parts of Chapter 8 about testing and common subexpression elimination are based on Frida J. Tveit's Part II project. Examples from Chapter 6 are taken from various sources, as described there. Chapter 11 is based on Pichon-Pharabod and Sewell [65], and discusses other people's work.

# Abstract

Many hardware and compiler optimisations introduced to speed up single-threaded programs also introduce additional, sometimes surprising, behaviours for concurrent programs with shared mutable state. How many of these extra behaviours occur in practice depends on the combination of the hardware, compiler, runtime, etc. that make up the platform. A memory model, which prescribes what values each read of a concurrent program can read, allows programmers to determine whether a program behaves as expected without having to worry about the details of the platform. However, capturing these behaviours in a memory model without also including undesirable "out-of-thin-air" behaviours that do not occur in practice has proved elusive. The memory model of C and C++ allows out-of-thin-air behaviour, while the Java memory model fails to capture some behaviours that are introduced in practice by compiler optimisations.

In this thesis, we propose a memory model that forbids out-of-thin-air behaviour, yet allows the behaviours that do occur. Our memory model follows operational intuitions of how the hardware and compilers operate. We illustrate that it behaves as desired on a series of litmus tests. We show that it captures at least some of the expected behaviours, that it forms an envelope around some common compiler optimisations, and that it is implementable on common hardware using the expected compilation schemes. We also show that it supports some established programming idioms.

# Acknowledgements

My supervisor, Peter Sewell. My examiners, Neel Krishnaswami and Viktor Vafeiadis. My assessors, Alan Mycroft and Andy Pitts. My coauthors, Mark Batty, Lars Birkedal, Kayvan Memarian, Kyndylan Nienhuis, Filip Sieczkowski, Kasper Svendsen, and Frida Tveit. For interesting discussions and remarks, Richard Bornat, Simon Castellan, Ohad Kammar, Robin Morrisset, and Jaroslav Ševčík. My office mates, Shaked Flur and Hannes Mehnert. The PLS group at the Computer Laboratory. For the vector file of the crest of Trinity Hall, Kayvan Memarian. For encouraging me to apply to Cambridge, James Leifer. The administrative staff of the Computer Laboratory, especially Lise Gough. My friends, and my family.

$\mathring{A} M^{me} W.$

# Contents

| 1        | Intr | Introduction 13          |                                                    |          |  |  |  |  |

|----------|------|--------------------------|----------------------------------------------------|----------|--|--|--|--|

|          | 1.1  | Cont                     |                                                    |          |  |  |  |  |

|          | 1.2  |                          | alling the problems                                |          |  |  |  |  |

|          |      | 1.2.1                    | The thin-air problem                               |          |  |  |  |  |

|          |      | 1.2.2                    | Per-candidate-execution semantics does not suffice | 16       |  |  |  |  |

|          |      | 1.2.3                    | Further challenges                                 | 17       |  |  |  |  |

|          |      | 1.2.4                    | The concurrent undefined behaviour problem         | 19       |  |  |  |  |

|          | 1.3  | Thes                     | sis                                                | 19       |  |  |  |  |

| <b>2</b> | Bac  | Background 21            |                                                    |          |  |  |  |  |

|          | 2.1  | _                        | guage                                              | 21       |  |  |  |  |

|          | 2.2  | ~                        | c memory model concepts                            |          |  |  |  |  |

|          | 2.3  |                          | C/C++11 memory model                               |          |  |  |  |  |

|          |      | 2.3.1                    | Description                                        |          |  |  |  |  |

|          |      | 2.3.2                    | Limitations of $C/C++11$                           |          |  |  |  |  |

|          | 2.4  | The                      | Java Memory Model                                  |          |  |  |  |  |

|          |      | 2.4.1                    | Description of the JMM                             |          |  |  |  |  |

|          |      | 2.4.2                    | Limitations of the JMM                             | 35       |  |  |  |  |

|          | 2.5  | Hard                     | lware memory models                                | 35       |  |  |  |  |

|          |      | 2.5.1                    | The Power memory model                             |          |  |  |  |  |

|          |      | 2.5.2                    | The ARMv7 memory model                             | 41       |  |  |  |  |

|          |      | 2.5.3                    | The (revised) ARMv8 model                          |          |  |  |  |  |

|          |      | 2.5.4                    | The x86-TSO memory model                           |          |  |  |  |  |

| 3        | Our  | Our model, informally 45 |                                                    |          |  |  |  |  |

|          |      | 3.1 Thread state         |                                                    |          |  |  |  |  |

|          | 3.2  |                          | amics                                              |          |  |  |  |  |

| 4        | 0117 | modo                     | el, in detail                                      | 53       |  |  |  |  |

| 4        | 4.1  |                          | nory actions                                       |          |  |  |  |  |

|          | 4.1  |                          |                                                    |          |  |  |  |  |

|          | 4.4  | 4.2.1                    | Event structures                                   | 54       |  |  |  |  |

|          |      | 4.2.1                    | Construction of the initial event structure        | 55       |  |  |  |  |

|          |      | 4.2.3                    |                                                    | 55<br>57 |  |  |  |  |

|          | 19   | _                        | Thread and program state                           |          |  |  |  |  |

|          | 4.3  |                          | aced configurations                                | 57       |  |  |  |  |

|          | 4.4  |                          |                                                    | 58<br>50 |  |  |  |  |

|          |      | 4.4.1                    | Outcome                                            | 59       |  |  |  |  |

|          |      | 4.4.2                    | Storage subsystem                                  | 59<br>60 |  |  |  |  |

|          |      | 44.                      | DEIALIVISALIOII                                    | m        |  |  |  |  |

|   |      | 4.4.4          | Execution                                             |     |   | 61         |

|---|------|----------------|-------------------------------------------------------|-----|---|------------|

|   |      | 4.4.5          | SC accesses                                           |     |   | 62         |

|   |      | 4.4.6          | Resumption                                            |     |   |            |

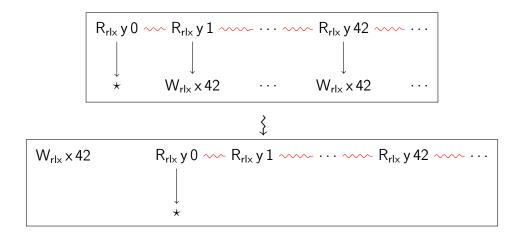

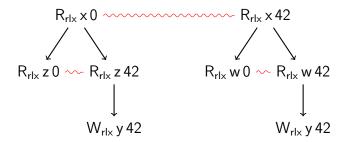

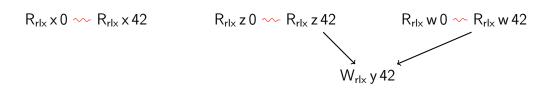

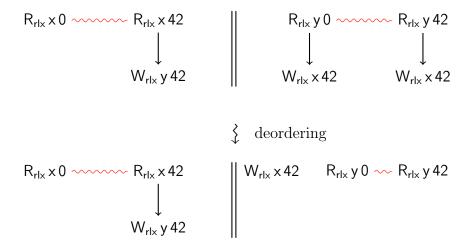

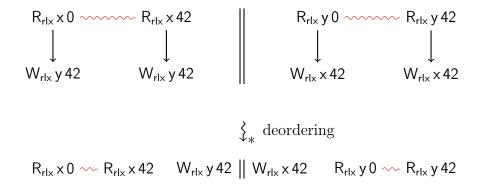

|   |      | 4.4.7          | Deordering                                            |     |   | 63         |

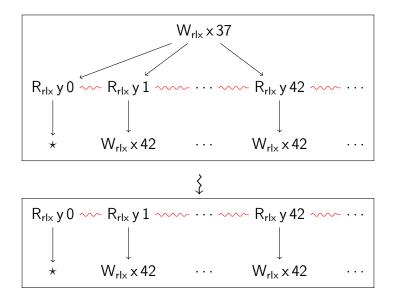

|   |      | 4.4.8          | Merging                                               |     |   | 65         |

|   |      | 4.4.9          | Undefined behaviour                                   |     |   | 67         |

|   |      |                |                                                       |     |   | 68         |

|   |      | 1.1.10         | range speculation                                     | • • | • | 00         |

| 5 | Disc | cussion        | 1                                                     |     |   | 69         |

|   | 5.1  | Desig          | gn choices                                            |     |   | 69         |

|   | 5.2  | Tech           | mical remarks                                         |     |   | 71         |

|   |      | 5.2.1          | Deordering side condition                             |     |   | 71         |

|   |      | 5.2.2          | Deordering graph transformation                       |     |   | 71         |

|   |      | 5.2.3          | SC accesses and merging                               |     |   | 72         |

|   |      | 5.2.4          | No value-range speculation for synchronising reads    |     |   | 72         |

|   | 5.3  | The            | power of value-range speculation                      |     |   | 72         |

|   | 5.4  | _              | es                                                    |     |   |            |

|   |      |                |                                                       |     |   |            |

| 6 | Exa  | mples          |                                                       |     |   | <b>7</b> 5 |

|   | 6.1  | Tool           |                                                       |     |   | 75         |

|   | 6.2  | No cl          | classic out-of-thin-air                               |     |   | 75         |

|   | 6.3  | Java           | Causality Test Cases                                  |     |   | 78         |

|   | 6.4  | Ševčí          | ík's litmus tests                                     |     |   | 84         |

|   | 6.5  | Misce          | ellaneous tests of relaxed atomics                    |     |   | 85         |

|   | 6.6  |                | chronising accesses                                   |     |   | 86         |

|   | 6.7  | Unde           | efined behaviour                                      |     |   | 89         |

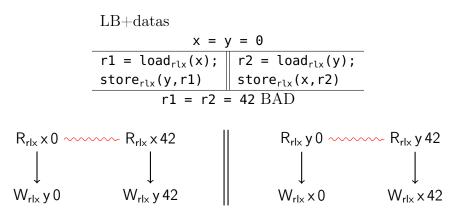

|   |      | 6.7.1          | LB and undefined behaviour                            |     |   | 89         |

|   |      | 6.7.2          | Undefined behaviour does not trigger itself           |     |   | 90         |

| 7 | Imn  | lement         | tability                                              |     |   | 91         |

| • | 7.1  |                | lementability on x86-TSO                              |     |   |            |

|   |      | -              | dementability on Power                                |     |   |            |

|   | 1.4  | 7.2.1          | Overview                                              |     |   |            |

|   |      | 7.2.1 $7.2.2$  | Details                                               |     |   | 96         |

|   | 7.3  | •              | arks                                                  |     |   | 99         |

|   | 7.4  |                | ted work                                              |     |   |            |

|   | 1.4  | Tuciai         | work                                                  |     | • | 100        |

| 8 | Sou  | $_{ m ndness}$ | s of optimisations                                    |     |   | 101        |

|   | 8.1  |                | interaction of value-range analysis and merging       |     |   | 101        |

|   | 8.2  |                | iliary definitions for syntactic program manipulation |     |   |            |

|   | 8.3  |                | ster operations                                       |     |   |            |

|   | 8.4  |                | mon subexpression elimination                         |     |   |            |

|   | 8.5  |                | stant propagation                                     |     |   |            |

|   | 8.6  |                | d code elimination (restricted)                       |     |   |            |

|   | 8.7  |                | dering                                                |     |   |            |

|   | 8.8  |                | evant read introduction                               |     |   |            |

|   | 8.9  |                | ble-program optimisations                             |     |   |            |

|   | 8.10 |                | ing: per-execution translation validation             |     |   |            |

|   | Q.10 |                | tod work                                              |     |   | 100        |

| 9         | Addi  | tional validation                                               | 111 |

|-----------|-------|-----------------------------------------------------------------|-----|

|           | 9.1   | "No out-of-thin-air guarantee" for arithmetic-free programs     | 111 |

|           | 9.2   | Strong release/acquire                                          | 112 |

|           | 9.3   | Fences                                                          | 113 |

|           | 9.4   | Relation to $C/C++11$ (for programs with only relaxed accesses) | 113 |

|           | (     | 9.4.1 Race reconstruction                                       | 113 |

|           | )     | 9.4.2 Value-range speculation in $C/C++11$                      | 114 |

|           | )     | 9.4.3 Relating executions                                       | 114 |

|           | 9.5   | Relation to strengthened C/C++11                                | 120 |

| 10        | Limit | tations                                                         | 121 |

|           | 10.1  | Finite value domain                                             | 121 |

|           | 10.2  | Loops                                                           | 121 |

|           | 10.3  | Addresses and address dependencies                              | 121 |

|           | 10.4  | Location typing                                                 |     |

|           | 10.5  | Read-modify-writes                                              | 122 |

|           | 10.6  | Locks and divergence                                            | 122 |

|           | 10.7  | Memory layout model                                             | 122 |

|           | 10.8  | Unsequenced and indeterminately sequenced accesses              | 123 |

|           | 10.9  | Sequencing of threads                                           | 123 |

|           | 10.10 | Optimising synchronising accesses                               |     |

|           | 10.11 | Monotonicity                                                    | 124 |

|           | 10.12 | The consume memory order                                        |     |

|           | 10.13 | The SC memory order                                             | 125 |

|           | 10.14 | Fences                                                          | 125 |

|           | 10.15 | ARM                                                             | 125 |

| 11        | Relat | sed work                                                        | 127 |

|           | 11.1  | Out-of-thin-air                                                 | 127 |

|           | 11.2  | Miscellaneous                                                   | 129 |

| <b>12</b> | Conc  | lusion                                                          | 131 |

# Notation

```

ff \ \ denotes \ the \ boolean \ "false"

ff \ \ denotes \ the \ boolean \ "false"

[] \ \ denotes \ the \ empty \ list

\ell_1 ++ \ell_2 \ \ denotes \ the \ concatenation \ of \ the \ lists \ \ell_1 \ and \ \ell_2

e \ \# \ e' \ \ denotes \ conflict, \ see \ Page \ 54

e \sim e' \ \ denotes \ immediate \ conflict, \ see \ Page \ 54

\rightsquigarrow \ \ denotes \ steps \ of \ the \ semantics

; \ is \ the \ statement \ separator, \ and \ also \ denotes \ concatenation \ of \ statements

\{a \mapsto b\} = \{(a,b)\}

f[a \mapsto b] = \{(a',b') \mid (a',b') \in f \land a' \neq a\} \cup \{(a,b)\}

fst((a,b)) = a

snd((a,b)) = b

A \uplus B = A \cup B, \ but \ is \ only \ defined \ when \ A \cap B = \varnothing

```

The syntax of the language we use for our examples is described on Page 21.

In a litmus test postcondition, x = v means that the last write to x in coherence order is a write of v.

# Chapter 1

# Introduction

#### 1.1 Context

Multiprocessors appeared as early as 1962, with the Burroughs D-825 [30], but remained rare for many years, as it was often simpler, cheaper, and more usable to increase CPU clock frequency and exploit instruction-level parallelism. However, in the early 2000s, hardware designers found themselves too constrained by the challenges of power dissipation to continue increasing frequency, and unable to extract any more instruction-level parallelism. Instead, they had to resort to designing multiprocessors, in the form of multicore processors, that is, multiprocessors on a single piece of silicon [37]. However, as for any multiprocessor, to actually take advantage of the joint computing power of the cores, many tasks require the cores to communicate. In mainstream multicore processors, this communication is done via a shared, mutable memory through which cores communicate by writing and reading. This memory is implemented by a series of buffers and caches on top of a flat memory that propagate writes and reads from one core to the others. However, this mechanism is typically not transparent: a program executing on multiple cores can observe that there is something interposed between its threads, and that memory is not sequentially consistent [45], that is, an immediately updated map from locations to values. This appeared as early as 1972 with the IBM 370/158MP [12], but became widespread in the 2000s with multicore processors. Moreover, on many architectures, cores have instruction pipelines that execute independent instructions, for example writes to different memory locations, out of order, in a way that programs can observe. This compounds with the effect of caches and buffers. This setting where memory is not sequentially consistent is called *relaxed*, or *weak*.

As the exact extent of the relaxed behaviours depends on details of the hardware configuration, programmers and hardware designers benefit from a memory model of the hardware, that is, a description of the allowed behaviours. The memory model of the hardware acts as a contract between the programmer and hardware designers. Programmers can work against the memory model rather than the details of the hardware, and hardware designers can change the details of the hardware, as long as they follow the memory model. The design of the memory model is in tension between two goals. (1) The memory model needs to allow enough behaviours to be implementable efficiently. (2) At the same time, the memory model needs to forbid enough behaviours to be programmable efficiently. Programmers should not need to introduce so many synchronisation instructions to ensure the outcome of their programs that they cancel the benefits of having a relaxed memory in the first place. Moreover, the memory model benefits from being

abstract, so that programmers do not need to know about the details of the hardware, and so that hardware designers can change those details.

Programming languages add their own challenge to relaxed memory. While a machinecode program is meant to be taken at face value by the hardware, a program in a programming language alludes to some machine-code program that — one hopes — executes fast. Compilers are expected to deliver such a machine-code program. To do so, they are allowed to take certain liberties with the program text concerning how the flow of the program is expressed, the pattern of accesses to the memory, etc. The extent of these liberties was not designed, but rather accumulated over time, from the early work of Allen [8] to sparse conditional constant propagation [88] and beyond. These liberties allow a compiler to optimise a single-threaded program, that is, replace it with a program the behaviours of which are behaviours of the original, but is — one hopes — faster. However, when applied to a multi-threaded program, these 'optimisations' can introduce extra behaviours, making the term misleading. By the time the extent of this interaction was realised, for example by Boehm [19], programmers were unwilling to give up on established compiler optimisations, and the effect of the state of the art in implemented compiler optimisations was restricted enough for programming with the extra behaviours to still be possible in practice. However, describing the extent of the extra behaviours, that is, designing a memory model for a programming language, is an open problem. Batty et al. [12] note that:

Disturbingly, 40+ years after the first relaxed-memory hardware was introduced (the IBM 370/158MP), the field still does not have a credible proposal for the concurrency semantics of any general-purpose high-level language that includes high-performance shared-memory concurrency primitives. This is a major open problem for programming language semantics.

Neither of the main previous attempts succeeds in this. The Java Memory Model [49] is unsound with respect to standard compiler optimisations [26, 75]. The memory model of C11 and C++11 (abbreviated C/C++11) [20, 18, 2, 15] is arguably the current state of the art, and gives the "right" behaviours in many cases, but it permits too much in others. At the heart of the problem are the "thin-air" examples for concurrent high-performance accesses, recalled in Section 1.2.1, in which values appear out of nowhere [49, 75, 21, 12]. Those thin-air executions are not thought to occur in practice, with any combination of current compiler and hardware optimisations, but excluding them without also excluding important optimisations has not previously been achieved. A further concern for C/C++11, also highlighted by Batty et al. [12], is the interaction between undefined behaviour and relaxed memory, which we recall in Section 1.2.4.

## 1.2 Recalling the problems

## 1.2.1 The thin-air problem

As acknowledged by the C++11 standard [18], in trying to define an envelope around all reasonable optimisations, the C/C++11 memory model also admits undesirable executions where values seem to appear out of thin air. In Section 23.9, paragraph 9, the C++11 standard says (in C++11 syntax):

[Note: The requirements do allow r1 == r2 == 42 in the following example, with x and y initially zero:

```

// Thread 1:

r1 = x.load(memory_order_relaxed);

if (r1 == 42) y.store(r1, memory_order_relaxed);

// Thread 2:

r2 = y.load(memory_order_relaxed);

if (r2 == 42) x.store(42, memory_order_relaxed);

```

However, implementations should not allow such behavior. – end note

In this thesis, we use a more compact syntax, detailed in Section 2.1, in which this *litmus* test is as follows:

$$\begin{array}{c|cccc} LB + ctrldata + ctrl-single & & & & \\ x & = & y & = & 0 \\ \hline r1 & = & load_{rlx}(x); & r2 & = & load_{rlx}(y); \\ if & (r1 & == & 42) & if & (r2 & == & 42) \\ store_{rlx}(y, r1) & store_{rlx}(x, 42) \\ \hline r1 & = & r2 & = & 42 & BAD \\ \hline \end{array}$$

The program starts with two locations x and y, initially set to 0. It has two threads:

- 1. The first thread reads from location x into r1 with a relaxed read. A relaxed read or write in C/C++ is meant to be compiled to a plain load or store, without memory barriers or other synchronisation. If this read reads 42, then the first thread writes what it read (the contents of r1, which was checked by the test to be 42) to y with a relaxed write.

- 2. The second thread almost does the symmetric of the first thread: it reads from y into r2 with a relaxed read. If it read 42, then it writes 42 to x with a relaxed write.

We do not want this program to be allowed to end with r1 and r2 both being set to 42. For this outcome to happen, the read of the first thread would have to read 42, which it must read from the write of 42 of the second thread, as there are no other writes to x, and x is initially 0. The write of 42 of the second thread is only executed if the read of the second thread reads 42, which it must read from the write of the first thread (as there are no other writes to y, and y is initially 0). For the write of the first thread to write 42, the first thread must have read 42. This means that for the read of the first thread to read 42, it must read it from a write that itself depends on the read of the first thread reading 42. The only way this could happen is if one of the reads read the value 42 "out of thin air".

Having such "out of thin air" outcomes would be highly undesirable: not being able to constrain what values reads read breaks elementary programming and reasoning principles [11, 21, 84].

There is however no precise definition of what thin-air behaviour is—if there were, it could simply be forbidden by fiat, and the problem would be solved. Rather, there are a few known litmus tests like the one above where certain outcomes are undesirable and do not appear in practice as the result of hardware and compiler optimisations. The problem is to draw a fine line between those undesirable outcomes and the outcomes of other very similar litmus tests which important optimisations make observable and which therefore must be admitted.

Java Similar issues arose in the first Java Memory Model design, in a slightly different form [49]. C/C++11 has nonatomic and relaxed accesses, both of which are intended to be implementable without memory barriers or other synchronisation; concurrent relaxed access to the same location is permitted, while concurrent nonatomic access gives wholly undefined behaviour (to let optimisers assume the latter does not occur). Java plain (non-volatile) accesses are similarly intended to be implementable with just the underlying hardware plain loads and stores; programmers are not supposed to make non-synchronised concurrent use of these; however, to provide safety guarantees even in the presence of arbitrary code, the semantics must forbid the forging of pointers. However, if reads are allowed to read values "out of thin air", then such guarantees cannot be provided.

#### 1.2.2 Per-candidate-execution semantics does not suffice

A common approach to relaxed-memory semantics, and that followed by C/C++11, is to define what is called an *axiomatic* memory model. One defines a notion of candidate execution, each consisting of a set of memory actions and basic relations over them (such as program order, reads-from, coherence, etc., see below), and a consistency predicate that picks out the candidate executions that are allowed by the semantics (e.g. including a check that some happens-before relation, derived from the basic relations, is acyclic). The semantics of a program is taken to be the set of all consistent executions that are compatible with some control-flow unfolding of the program, or, in some semantics, that set modulo the existence of data races.

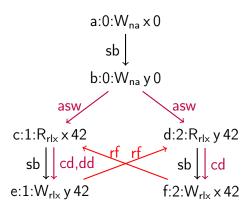

However, as observed by Batty et al. [12], there are pairs of programs which share a particular candidate execution where that execution should be allowed for one program but not for the other. Consider the following:

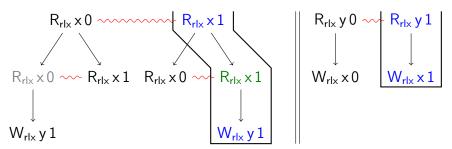

$$\begin{array}{c|cccc} LB + ctrldata + ctrl-double & & & & & \\ x & = & y & = & 0 & & \\ \hline r1 & = & load_{rlx}(x); & & r2 & = & load_{rlx}(y); \\ if & (r1 & == & 42) & & if & (r2 & == & 42) \\ store_{rlx}(y, r1) & & store_{rlx}(x, 42) \\ else & & store_{rlx}(x, 42) \end{array}$$

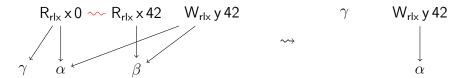

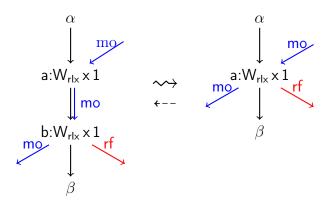

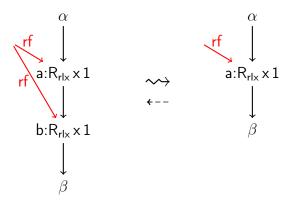

As there is a write to **x** in both branches of the second thread of LB+ctrldata+ctrldouble, the conditional can be collapsed by compiler optimisation to yield

$$\begin{array}{c|cccc} LB + ctrldata + po & & & \\ & x = y = 0 & & \\ \hline r1 = load_{rlx}(x); & r2 = load_{rlx}(y); \\ if (r1 == 42) & store_{rlx}(y, r1) & & store_{rlx}(x, 42) \end{array}$$

in which both threads can read 42, because the read and the write of the second thread can be reordered, either thread-locally (by the compiler or the hardware) or when propagating between the threads (by the hardware). This happens in practice, and so should be allowed by the semantics.

On the other hand, for LB+ctrldata+ctrl-single (the first example, from the C++ standard), this outcome does not appear in practice; that would, as discussed earlier, be highly undesirable.

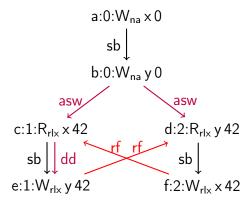

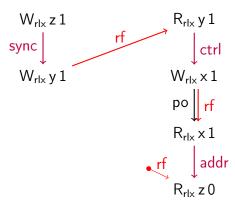

In the C/C++11 semantics (detailed in Section 2.3), the two share the candidate execution below, where "sb" ("sequenced-before") is program order, that is, the syntactic order coming from the program text, "asw" indicates thread synchronisation (here from the initial thread to spawned threads), and "rf" indicates where the reads read from. The other edges indicate syntactic dependencies: "dd" stands for (syntactic) data dependency, and "cd", which is not part of C/C++11, stands for (syntactic) control dependency.

**Dependencies** As the example above shows, syntactic data and control dependencies do not provide enough information to draw the distinction between desirable and undesirable outcomes. In retrospect, this is not surprising: programmers expect to be able to interchange control flow and dependencies without changing program outcome, and compilers do that freely, sometimes removing syntactic dependencies.

For example, LB+ctrl+po below ought to behave the same as LB+ctrldata+po, as the data dependency in LB+ctrldata+po does not contribute any information that the control dependency does not already contribute: the write to y can only be a write of 42, and compilers will routinely transform LB+ctrldata+po into LB+ctrl+po.

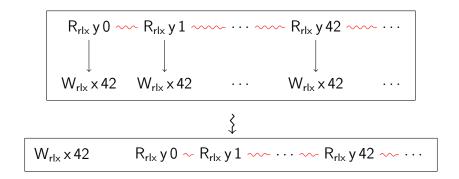

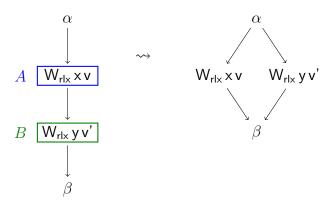

Perspective Trying to draw a more general, informal conclusion, Batty et al. [12, §6] argue that the problem with the C/C++11 memory model is that it considers executions individually, whereas what it is trying to model the effect of, the hardware and compiler optimisations, effectively consider all executions simultaneously by operating on the code. For example, executing the write in the second thread of LB+ctrldata+po before the read that is before it in program order is justified because the write occurs in all control-flow paths. Similarly, optimising LB+ctrldata+ctrl-double into LB+ctrldata+po is justified because the write of the second thread occurs in all control-flow paths.

## 1.2.3 Further challenges

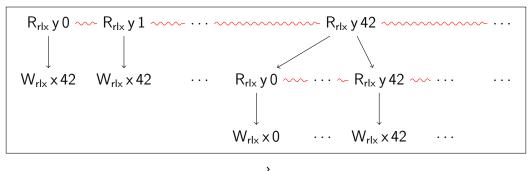

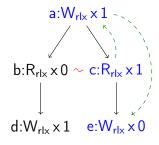

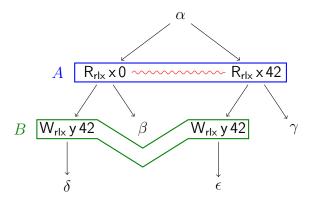

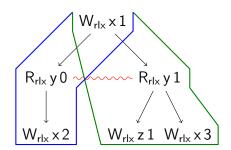

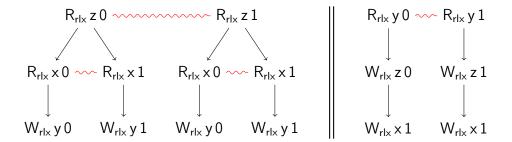

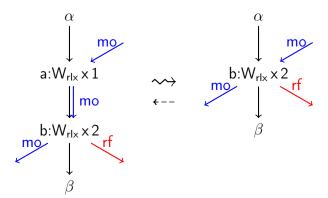

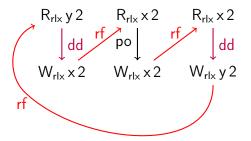

Merging Compiler optimisations can also merge memory actions. For example, for the nonatomic version of the below, compiler passes like common subexpression elimination can and do merge the reads of y. The same optimisation for relaxed atomics, turning it

into the second thread of LB+ctrldata+ctrl-double, has been proposed [10]. This would allow the outcome where r1 and r2 are set to 42.

```

JMM CSE trap

x = y = 0

r1 = load<sub>rlx</sub>(x);

if (r1 == 42)

store<sub>rlx</sub>(y,r1)

r2 = load<sub>rlx</sub>(y);

if (r2 == 42) {

r3 = load<sub>rlx</sub>(y);

store<sub>rlx</sub>(x,r3)

} else {

store<sub>rlx</sub>(x,42)

}

```

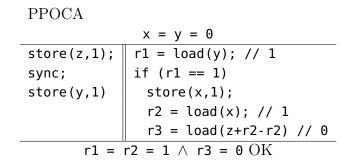

Memory models for programming languages need to account for these optimisations. However, the Java Memory Model fails to give this particular litmus test the right behaviour, as noted by Ševčík and Petri [74] (we describe this in more detail in Section 2.4).

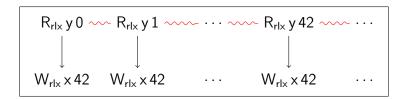

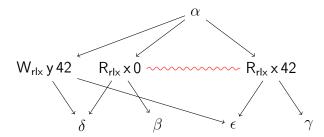

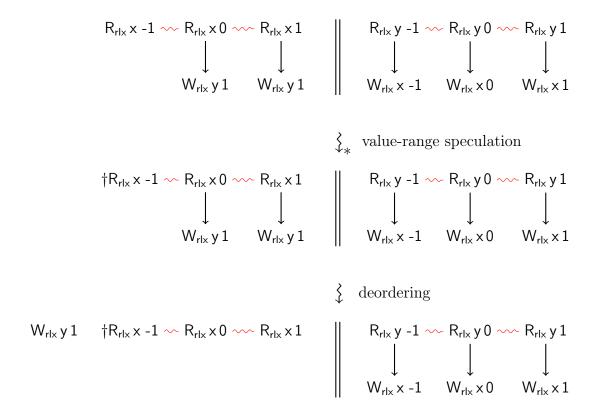

Value-range analysis The optimisations considered so far are thread-local, and independent of the manipulated values, and of the wider program in which a thread executes. However, their applicability can be greatly extended by analyses. For example, a compiler pass could analyse the values that x and y can take during executions of the program below, a variant of the Causality Test Case 1 of Pugh [68]. This analysis, the kind of which we will refer to as "value-range analysis", could determine that r2 will always contain a nonnegative value. The compiler could then collapse the if, and turn this program into LB+ctrldata+po, and therefore allow the outcome where r1 and r2 are set to 42.

Java causality test case 1 variant

While we are not aware of this precise optimisation being done, counterparts on pointers are performed by alias analyses [22].

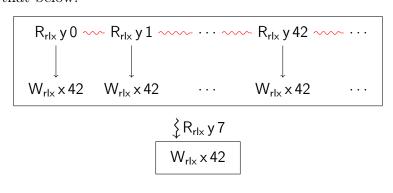

Moreover, analysis during just-in-time compilation can take advantage of information about the current state of the program, for example that a write has propagated to a thread, masking previous values and hence shrinking the set of possible values of a variable, thereby enabling additional optimisations. For example, in the program below, after the write of 1 to z by the third thread has propagated to the second thread, the conditional on r3 in the second thread can be collapsed, yielding LB+ctrldata+ctrl-double, and therefore allowing the outcome where r1 and r2 are set to 42. While C/C++11 is not typically compiled just-in-time, the combination of inlining and special-casing has similar effects.

Guarded LB+ctrldata+ctrl-double

To prevent undesirable behaviour, and in particular thin-air reads, such analysis has to be stable under the effect of the optimisations it enables. In the program below, without optimisations taking advantage of value-range analysis, the read of the second thread cannot read 42. However, if an optimisation takes advantage of that information to reorder the write of the second thread, then the read of the second thread can read 42. This violates the assumption it made earlier, and makes the program execute a write of 42 to x even though it should not execute any if the second thread reads 42.

Java causality test case 1 broken variant

Importantly, this means that optimisations do not necessarily increase the behaviour of threads. An optimisation based on value-range analysis can allow more the behaviour for one thread, for example allowing it to execute a write early, which can allow less behaviour of another thread, for example forbidding it from assuming that a certain read cannot read a certain value, and therefore forbidding it from executing another write early, because the early write now makes this reading this value possible. This also compounds with the fact that merging can restrict the behaviour of a thread, for example preventing it from reading two different values from the same location and therefore preventing it from executing a write, which can allow another thread to assume that it cannot read a certain value (the one written by the write that is now impossible), and therefore allow that other thread more behaviour. This defeats the hope of identifying a maximally optimised program.

#### 1.2.4 The concurrent undefined behaviour problem

The C/C++11 memory model also has an issue with its treatment of undefined behaviour, that is separate from, but interacts with, the "out-of-thin-air" problem. If a language features undefined behaviour, as C and C++ do, then its memory model needs to be able to express it, to determine whether it is triggered. As pointed out by Batty et al. [12, §7], there is a mismatch in the C/C++ standard: the thread-local semantics, which is described operationally, assumes that there is some form of execution order that makes it possible to tell whether a point of the program has been reached, and therefore undefined behaviour is triggered (though if undefined behaviour is triggered, it makes the whole program undefined, not merely the execution from that point). However, the candidate executions of the axiomatic memory model do not have such a notion, and because they are candidate complete executions, rather than being built incrementally, it is far from obvious how it could be included. We illustrate this problem and explain how our memory model accounts for it in Section 6.7.

#### 1.3 Thesis

Our thesis is that it is possible to address these problems:

It is possible to design memory models for programming languages, that are weak enough to be sound with respect to hardware- and compiler-induced behaviour, but strong enough to be usable, by excluding out-of-thin-air behaviour. Moreover, it is also possible to handle undefined behaviour in concurrent contexts.

**Plan** We support this thesis by presenting a memory model (Chapters 3, 4, and 5), arguing that it behaves well on a series of litmus tests (Section 6), establishing that it can be implemented using the expected compilation schemes (Chapter 7) and that it forms an envelope around some common compiler optimisations (Chapter 8), and showing that it supports some common programming idioms (Chapter 9). We then discuss the remaining challenges (Chapter 10).

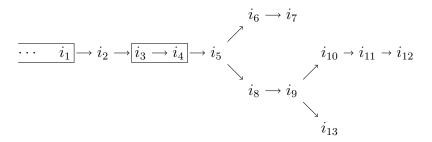

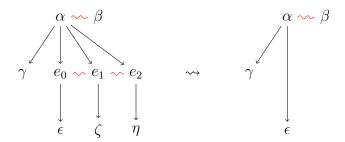

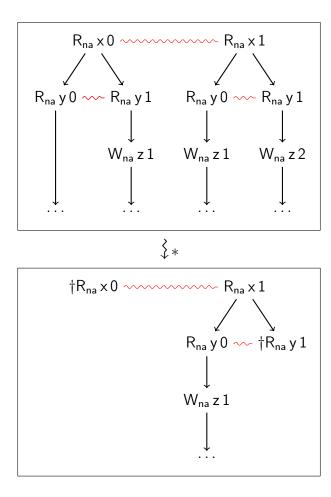

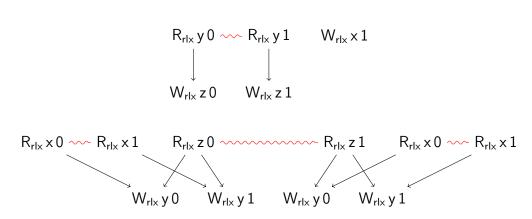

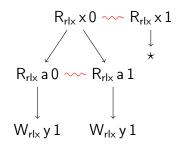

Summary of our approach In our memory model, we represent the state of a thread using an event structure, that is, a set of events equipped with some causal order and a conflict relationship obeying certain sanity conditions. The event structure represents all the possible future executions of the thread. The key idea of our memory model is that a thread can take transitions that mutate its event structure that account for mixed execution and thread-local and inter-thread optimisations. Threads interact by synchronising through a storage subsystem.

# Chapter 2

# Background

In this chapter, we first introduce the syntax of the calculus we will consider, and discuss general features of memory models. We then describe the two most developed programming language memory models, those of C/C++11 and Java, as they delineate the problem well: the former allows too much behaviour, and the latter too little. Finally, we describe the hardware memory models of Power, ARM, and x86, to provide context and a counterpoint to the challenges of designing a memory model for a programming language, and because our memory model reuses the storage subsystem of Power (as described in Section 4.4.2). We leave discussion of other related work to Chapter 11.

## 2.1 Language

We consider a minimal calculus featuring the core concurrency primitives of C/C++11, but (as explained below) abstracting over the subtleties of the thread-local semantics. This calculus is inspired by that of the CppMem C/C++11 memory model exploration tool [14]. It features relaxed-atomic, nonatomic, and sequentially consistent reads and writes, acquire reads, release writes, read-modify-writes, locks, and a thread-local undefined behaviour trigger. This covers all the C/C++11 memory orders except "consume".

**Definition 1.** The syntax of our calculus is defined inductively by

```

program

parallel threads

|ss_1| ... |ss_n|

statement

| r = load_{rmo}(x)

read

store<sub>wmo</sub>(x,e)

write

r1, r2 = rmw_{acqrel/acq}(x,e,e')

read-modify-write

| if (e_1 cmp e_2) ss_1 else ss_2

conditional

r = e

register assignment

lock \ell

lock

unlock \ell

unlock

undefined behaviour

undef

ss ::=

statements

sequential composition

S<sub>1</sub>; ... ; S<sub>n</sub>

{ ss }

block

pure expressions

е

::=

```

```

٧

constant

r

register

sum

e_1 + e_2

difference

| e_1 - e_2 |

. . .

comparison operator

cmp ::=

equality

| ==

!=

inequality

| >=

greater than

rmo ::=

read memory orders

relaxed

rlx

acquire

acq

SC

sequentially consistent

nonatomic

na

\mathsf{wmo} ::=

write memory orders

rlx

relaxed

release

rel

sequentially consistent

SC

nonatomic

na

```

Variables x, y, ..., are shared memory locations, and actions on them induce memory actions, whereas r1, r2, ..., are registers, thread-local variables which have no effect on memory, and  $\ell$  is a lock location.

The registers in our calculus do not feature in usual programming languages, and are unrelated to the C/C++11 "register" keyword. We introduce them in our calculus for two purposes. First, they are used to explicitly represent data flow, which allows us to have simple, well-separated constructs in our language, instead of the complex compound constructs of real programming languages. For example, y = x++ in C/C++11 can be expressed (if we focus on data flow and ignore the many important details, for example as developed by Memarian et al. [57]) in our calculus as

$$r1 = load_{na}(x)$$

$r1 = r1 + 1$

$store_{na}(x,r1)$

$store_{na}(y,r1)$

Second, they can be used to elide irrelevant memory actions. For example, int y = x in C/C++11, where y is purely thread-local, corresponds to

$$r1 = load_{na}(x)$$

store<sub>na</sub>(y,r1)

despite the fact that the store to y, or in fact the existence of y, is irrelevant to concurrency, and that the program could more simply be written as

$$ry = load_{na}(x)$$

While most programming languages do not feature such register variables, intermediate languages in compilers, for example registers in LLVM IR [4], or in semantics, for example the CppMem C/C++11 memory model exploration tool [14], or the Core language in the Cerberus C semantics [57], do. Moreover, optimisations like scalar replacement of aggregates transform the program with the irrelevant variable y above into the one where it has been replaced by a register. We return to this in Section 8.4 in the context of common subexpression elimination.

**Undefined behaviour** In C/C++11, in addition to memory errors, undefined behaviour can be induced by some operations, for example division by zero. In our calculus, for clarity, we separate thread-local undefined behaviour from other operations, with an **undef** statement that signals undefined behaviour.

**Location typing** As in the formalised C/C++ memory model, for simplicity, we assume a location typing: each location can be used for either atomic locations, or nonatomic locations, or locks. We return to this limitation in Section 10.4.

Finite domain We restrict values (v above) to a finite domain V. Our calculus does not feature pointers, or different types of values, as they are not directly relevant to out-of-thin-air. While the out-of-thin-air problem is independent from pointers, it is especially problematic in the presence of pointers, as it violates physical separation, as illustrated by "ghostly linking of data structures" example of Boehm and Demsky [21]. We return to this limitation in Section 10.1.

Address dependencies Our language does not feature computed addresses, or address dependencies. We return to this limitation in Section 10.3.

**Loops** Our language omits loops. This is not for any fundamental reason, but rather to keep the semantics straightforwardly executable. We return to this limitation in Section 10.2.

Thread composition Our language features a top-level concurrent composition of threads (the "parallel" operator ||) rather than the thread management mechanism of C/C++11. This allows us to consider litmus tests without clutter, at the cost of limiting us to a bounded number of threads.

RMWs Our language features a read-modify-write (abbreviated RMW, and also called 'atomic update') operation, rmw. Given a location, a value to be expected, and a replacement value, it tries to atomically read the expected value from the location, and replace it with the replacement value, returning a success/failure flag, and the value read. This specific kind of RMW is also called 'compare-and-swap' or 'compare and exchange'. The RMW we model reads with the same strength as an acquire read, and writes with the same strength as a release write. We return to this limitation in Section 10.5.

## 2.2 Basic memory model concepts

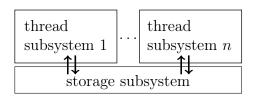

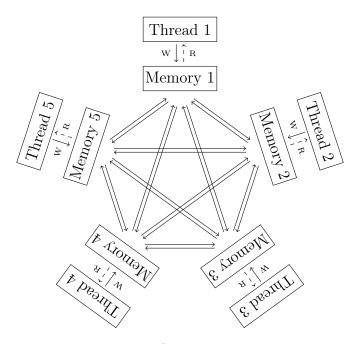

Figure 2.1: Schema of a memory model split into a storage subsystem and thread subsystems

**Styles** There are several styles of memory models: the *operational* style, where the memory model is defined by the steps of an abstract machine, as in our case; the *axiomatic* style<sup>1</sup>, where a complex, global predicate is used to filter a coarse set of potential executions of a program (the C/C++11 memory model, sketched in Section 1.2.2, is an example of this style); the *denotational* style, where the description of a program is built inductively. Because of the problem they try to address, many memory models are made from a combination of different styles.

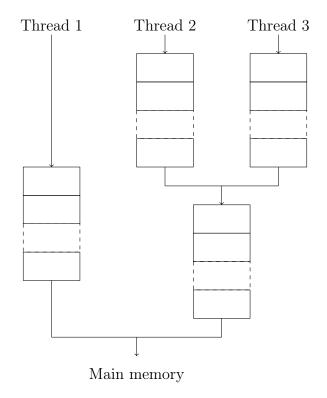

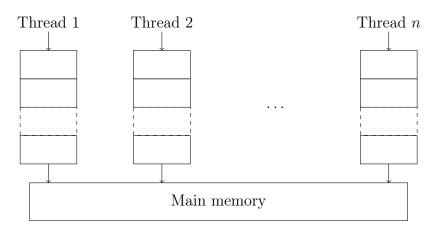

Thread subsystem and storage subsystem To simplify presentation, and to reflect the architecture of the underlying hardware, memory models, in particular operational memory models, are often split into two parts, as sketched in Figure 2.1: a *storage subsystem*, through which threads communicate, that describes the propagation effects between threads, and *thread subsystems*, that describe the out-of-order execution of instructions by the threads.

Coherence An important feature of most memory models (C/C++11, Power, ARM, x86, but not Java, see Causality Test 16 on Page 83) is coherence. Coherence is the existence, for each location, of a total order on the writes at that location that respects program order, and that reads respect. C/C++11 expresses coherence using a "modification order" relation on writes. The following litmus test illustrates one aspect of coherence, "read-read coherence":

$$\begin{array}{c|c} \operatorname{CoRR} & & & \\ & & x = 0 \\ \hline & \operatorname{store}_{\operatorname{rlx}}(x,1); & \operatorname{r1} = \operatorname{load}_{\operatorname{rlx}}(x); \\ \operatorname{store}_{\operatorname{rlx}}(x,2) & \operatorname{r2} = \operatorname{load}_{\operatorname{rlx}}(x) \\ \hline & \operatorname{r1} = 2 \wedge \operatorname{r2} = 1 \operatorname{BAD} \\ \end{array}$$

Coherence respects program order, so the write of 1 is before the write of 2 in coherence order. Reads from the same thread respect coherence, so if the first read reads from the write of 2, the second read cannot read from the write of 1. This is not enforced if the locations are different, as illustrated by the MP litmus test on Page 86.

The following litmus illustrates that what is respected is coherence, not merely program order of writes: if the third thread observes that the write of 1 is before the write of 2 in coherence order, by reading 1, then 2, then the fourth thread cannot read 2, then 1, as that would violate the coherence order we know from the third thread.

$<sup>^{1}</sup>$ This is different from the usual meaning of "axiomatic semantics", where the semantics of a programming language is given by a program logic.

#### CoRR2

| x = 0                                               |                            |                                               |                       |  |  |  |

|-----------------------------------------------------|----------------------------|-----------------------------------------------|-----------------------|--|--|--|

| $store_{rlx}(x,1)$                                  | store <sub>rlx</sub> (x,2) | $r1 = load_{rlx}(x);$                         | $r3 = load_{rlx}(x);$ |  |  |  |

|                                                     |                            | $r1 = load_{rlx}(x);$<br>$r2 = load_{rlx}(x)$ | $r4 = load_{rlx}(x)$  |  |  |  |

| $r1 = 2 \land r2 = 1 \land r3 = 1 \land r4 = 2 BAD$ |                            |                                               |                       |  |  |  |

Non-multi-copy-atomicity Writes at different locations propagate to each thread individually. This important feature of many relaxed memory models (in particular Power and ARMv7) is called non-multi-copy-atomicity in the terminology of Collier [28]. The following litmus test, IRIW ("independent reads of independent writes"), illustrates it: the write to x can propagate to third thread before the write to y does, while the write to y propagates to the fourth thread before the write to x does<sup>2</sup>:

#### **IRIW**

## 2.3 The C/C++11 memory model

The memory model of C++11 [18, 20] and C11 [2], which was formalised, concurrently with its development, by Batty et al. [15, 16], was the state of the art for production languages at the start of the work described in this thesis. Despite the focus of this document on its shortcomings regarding out-of-thin-air behaviour, the C/C++11 memory model achieved several of its objectives:

- It seems to almost form an envelope around hardware and compiler optimisations, and many of its shortcomings to do so seem fixable [83, 44].

- It is implementable on top of x86-TSO [15], Power [71, 13] (with a few fixes, see [44, 47]), and ARM [33], with simple and efficient compilation schemes (which we apply to our memory model in Chapter 7).

- Programs written in the fragment with only nonatomic and SC accesses and locks and free of races do not exhibit relaxed behaviour [12, §3] (this property is sometimes called "DRF-SC" or "DRF0" [3]).

- It has a usable release/acquire fragment, for which program logics have been developed [84, 82]. Moreover, the release/acquire fragment can be made optimal with respect to the standard compilation scheme with relatively minor modifications [43] (as we show for our memory model in Section 9.2).

Our remarks also apply to the memory model of OpenCL [89, 17], as it is an extension of the C/C++11 memory model, and suffers from the same issues.

<sup>&</sup>lt;sup>2</sup>The first read of each thread is an acquire read to prevent it from executing out of order with the other read by the same thread, which would also allow this outcome, even without multi-copy-atomicity.

#### 2.3.1 Description

The C/C++11 memory model is an axiomatic memory model. It is defined in phases:

• Each program is first mapped to the set of its "pre-executions". A pre-execution is a graph that represents the memory actions of a putative execution of the program, if we just consider the flow of values from reads to writes, but do not constrain what values reads can read, or where from.

For example, a program where a thread reads from x, and then writes what it read to y is going to have (among others) a pre-execution where that thread reads 0 from x, and writes 0 to y, and a pre-execution where it reads 42 from x, and writes 42 to y, but no pre-execution where it reads 0 from x, and writes 42 to y.

The set of pre-executions is defined by induction on the syntax, without interaction between the threads.

- Each pre-execution is then associated with the set of its "execution witnesses". An execution witness is a graph that proposes an interaction between the threads of a pre-execution that would make the pre-execution possible, in particular by providing, for each read, a write it proposes it reads from, and a coherence order.

- The set of pairs of a pre-execution and an execution witness (called a "candidate execution") is then filtered by a "consistency" predicate. The consistency predicate determines whether the execution witness justifies that the pre-execution should be considered a possible behaviour. In that case, the candidate execution is called an "execution", or a "consistent execution". This is the main part of the definition.

- In addition, the consistent executions are checked for data races and other such errors. This is done in a problematic way, as we describe in Section 9.4.1.

Because of the simple language we use (as defined in Section 2.1), we can make a few simplifications in our presentation. Memarian et al. [57] and Nienhuis et al. [62] show how to generate pre-executions for the (almost) entire C11 language.

#### Pre-executions

The definition of pre-executions is straightforward, but usually elided; we spell it out for clarity and completeness.

A pre-execution is a directed graph with two kinds of edges: sb ("sequence-before"), which represents program order, and dd, which represents data dependencies<sup>3</sup>, and where nodes are labelled with memory actions (the set of which we will denote A), like  $R_{rlx} \times v$ , a read of value v from location v, v, a write of value v to location v, etc. (we describe memory actions for our memory model, which are very close to that of v0/C++11, in Section 4.1).

**Definition 2.** X is a per-thread pre-execution when it is of the form  $\langle E, sb, data, \lambda \rangle$ , where

• E is a set of events<sup>4</sup>;

<sup>&</sup>lt;sup>3</sup>We do not consider address dependencies; we discuss this limitation in Section 10.3.

<sup>&</sup>lt;sup>4</sup>Batty et al. [15] call these "action identifiers". We call them events to make the relation to event structures more apparent.

- $sb \subseteq E \times E$ ;

- $dd \subseteq E \times E$ ;

- $\lambda: E \to A$ .

**Register state** Pre-executions constrain the flow of values from reads to writes (but not the values or the writes reads read), and record data dependencies ('dd'). To keep track of that information, when computing pre-executions, we keep it in a register state, where each register is associated to the last value it was set to, and to the events it depends on:

**Definition 3.** A C/C++11 register state (denoted  $\mu$ ) is a map from registers to values and sets of events.

For simplicity, we assume the registers of each thread are initialised to zero:

**Definition 4.** The initial C/C++11 register state  $\mu_0$  is such that for all r,  $\mu_0(r)=(0,\varnothing)$ .

A register state induces a value for expressions, and thus tests:

**Definition 5.** The value of an expression **e** in a register state  $\mu$ ,  ${}^{\text{c}}[\![\mathbf{e}]\!]_{\mu}^{\text{e}}$ , is defined inductively by

**Definition 6.** The *interpretation of a comparison operator* cmp, [cmp], is the associated mathematical operator.

**Definition 7.** The interpretation of a comparison is defined by:

$$^{\mathrm{C}}\llbracket \mathsf{e}_1 \text{ cmp } \mathsf{e}_2 \rrbracket_{\mu}^{\mathrm{e}} = {^{\mathrm{C}}}\llbracket \mathsf{e}_1 \rrbracket_{\mu}^{\mathrm{e}} \text{ } \llbracket \mathsf{cmp} \rrbracket {^{\mathrm{C}}} \llbracket \mathsf{e}_2 \rrbracket_{\mu}^{\mathrm{e}}$$

Register use induces data dependencies, which we then have to track:

**Definition 8.** Occurrence of a register r in an expression e,  $r \in e$ , is defined inductively by

$$r \in r$$

$r \in e1 + e2$  if  $r \in e1 \lor r \in e2$

The dependencies of an expression is the union of the dependencies of the registers occurring in that expression:

**Definition 9.** The dependencies of an expression **e** given a register state  $\mu$  are

$$^{\mathrm{c}}[\![\mathbf{e}]\!]_{\mu}^{\mathrm{r}} = \bigcup_{\mathsf{r}\in\mathsf{e}}\mathrm{snd}\left(\mu\left(\mathsf{r}\right)\right)$$

The C/C++11 semantics of a thread ss is given as the set of per-thread pre-executions inductively defined on ss. We use induction on the size of ss, rather than structural induction:

**Definition 10.** The size of a list of statements ss, |ss|, is defined inductively by:

$$\begin{split} |[]| &= 0 \\ |\texttt{r} = \texttt{load}_{\texttt{mo}}(\texttt{x}); \texttt{ss}| = |\texttt{ss}| + 1 \\ |\texttt{store}_{\texttt{mo}}(\texttt{x},\texttt{e}); \texttt{ss}| &= |\texttt{ss}| + 1 \\ |\texttt{lock}\; \ell; \texttt{ss}| &= |\texttt{ss}| + 1 \\ |\texttt{unlock}\; \ell; \texttt{ss}| &= |\texttt{ss}| + 1 \\ |\texttt{if}\; (\texttt{e}_1\; \texttt{cmp}\; \texttt{e}_2)\; \texttt{ss}_1\; \texttt{else}\; \texttt{ss}_2; \texttt{ss}| &= |\texttt{ss}_1| + |\texttt{ss}_2| + |\texttt{ss}| + 1 \\ |\texttt{r} = \texttt{e}; \texttt{ss}| &= |\texttt{ss}| + 1 \end{split}$$

**Definition 11.** The set of per-thread pre-executions of a list of statements ss given a C/C++11 register state  $\mu$ ,  ${}^{C}[\![ss]\!]_{\mu}^{t}$ , is defined inductively on  $[\![ss]\!]$  by:

• The set of pre-executions for the empty thread is just the empty pre-execution:

$${}^{\mathrm{C}}\llbracket\llbracket\rrbracket\rrbracket^{\mathrm{t}}_{\mu}=\{\langle\varnothing,\varnothing,\varnothing,\varnothing,\varnothing\rangle\}$$

• The set of pre-executions for a read contains, for each value v, and for each pre-execution X of the continuation of the read (where  $\mu$  has been updated so that  $\mathbf{r}$  maps to v, to reflect that the read has read v), the pre-execution with an event corresponding to reading v, sb-before X:

$$\mathbb{C}[\mathbf{r} = \mathsf{load_{mo}}(\mathbf{x}); \mathbf{ss}]_{\mu}^{\mathsf{t}} = \left\{ egin{array}{c} E \cup \{n\}, \\ sb \cup (\{n\} imes E), \\ dd, \\ \lambda \cup \{n \mapsto \mathsf{R_{mo}} imes v\} \end{array} \right| n

otin E \wedge \left\{ egin{array}{c} E, sb, dd, \lambda \in \mathbb{C}[\mathbf{ss}]_{\mu[\mathbf{r} \mapsto (v,\{n\})]}^{\mathsf{t}} \end{array} \right\}$$

• The set of pre-executions for a write contains, for each pre-execution X of the continuation of the write, a pre-execution with an event corresponding to writing the value of e in  $\mu$ , sb-before X, and dd-after its dependencies:

$$\begin{cases} E \cup \{n\}, \\ sb \cup (\{n\} \times E), \\ dd \cup \left(\left(\bigcup_{\mathbf{r} \in \mathbf{e}} \operatorname{snd}(\mu(\mathbf{r}))\right) \times \{n\}\right), \\ \lambda \cup \{n \mapsto \mathsf{W}_{\mathsf{mo}} \times \llbracket \mathbf{e} \rrbracket_{\mu} \} \end{cases} \\ \langle E, sb, dd, \lambda \rangle \in {}^{\mathtt{C}} \llbracket \mathbf{ss} \rrbracket_{\mu}^{\mathtt{t}}$$

• The set of pre-executions for a lock contains, for each pre-execution X of the continuation of the lock, a pre-execution with an event corresponding to locking, sb-before

X, plus a pre-execution with the lock failing:

$$\left\{ \left. \begin{cases} E \cup \{n\}, \\ sb \cup (\{n\} \times E), \\ dd, \\ \lambda \cup \{n \mapsto \mathsf{L}^+\ell\} \end{cases} \middle| n \notin E \land \right. \right\} \cup \left\{ \left. \left. \begin{cases} \{n\}, \\ \varnothing, \\ \varnothing, \\ \{n \mapsto \mathsf{L}^-\ell\} \end{cases} \right. \right\}$$

• The set of pre-executions for an unlock contains, for each pre-execution X of the continuation of the unlock, a pre-execution with an event corresponding to unlocking, sb-before X:

$$\left\{ \left. \begin{cases} E \cup \{n\}, \\ sb \cup (\{n\} \times E), \\ dd, \\ \lambda \cup \{n \mapsto \mathsf{U}\,\ell\} \end{cases} \right| n \notin E \land \right. \right\}$$

$$\left\{ \left. \begin{cases} E \cup \{n\}, \\ sb \cup (\{n\} \times E), \\ dd, \\ \lambda \cup \{n \mapsto \mathsf{U}\,\ell\} \end{cases} \right| n \notin E \land \right.$$

• The set of pre-executions of a conditional is the set of pre-executions of the appropriate continuation:

$$\begin{array}{l} ^{\mathrm{C}}\llbracket\mathrm{if}\ (\mathsf{e_1}\ \mathsf{cmp}\ \mathsf{e_2})\ \mathsf{ss_1}\ \mathsf{else}\ \mathsf{ss_2}; \mathsf{ss}\rrbracket^{\mathrm{t}}_{\mu} = \\ \left\{ \begin{array}{l} \mathrm{if}\ ^{\mathrm{C}}\llbracket\mathsf{e_1}\ \mathsf{cmp}\ \mathsf{e_2}\rrbracket^{\mathrm{e}}_{\mu},\ ^{\mathrm{C}}\llbracket\mathsf{ss_1}; \mathsf{ss}\rrbracket^{\mathrm{t}}_{\mu} \\ \mathrm{else} \end{array} \right. \end{array}$$

• The set of pre-executions of a register assignment is the set the pre-executions of its continuation, where  $\mu$  has been updated:

$${}^{\mathrm{C}}[\![\mathbf{r}=\mathbf{e};\mathbf{s}\mathbf{s}]\!]_{\mu}^{\mathrm{t}}={}^{\mathrm{C}}[\![\mathbf{s}\mathbf{s}]\!]_{\mu\left[\mathbf{r}\mapsto\left({}^{\mathrm{C}}[\![\mathbf{e}]\!]_{\mu}^{\mathrm{e}},{}^{\mathrm{C}}[\![\mathbf{e}]\!]_{\mu}^{\mathrm{r}}\right)\right]}$$

**Undef** This definition does not cover undef, because the memory model of C/C++11 does not cover thread-local sources of undefined behaviour, as discussed in Section 1.2.4.

**RMWs** For brevity, this definition does not cover RMWs, which follow the same pattern as the rest of the construction.

This definition generates many graph-isomorphic pre-executions corresponding to the "same" pre-execution, but with different event names (and other definitions for C/C++11 suffer from the same defect). This does not matter for our purposes.

**Definition 12.** The *per-thread pre-executions of a thread* are its per-thread pre-executions in the initial register state:

$$^{\scriptscriptstyle \mathrm{C}}\llbracket\mathtt{ss}

rbracket^{\scriptscriptstyle \mathrm{t}}={}^{\scriptscriptstyle \mathrm{c}}\llbracket\mathtt{ss}

rbracket^{\scriptscriptstyle \mathrm{t}}_{\mu_0}$$

Whole-program pre-executions A whole-program pre-execution is like a per-thread pre-execution, but where each event is labelled with both a memory action and a thread identifier (a natural number), and where there can be synchronisation edges between threads (asw, "additional synchronises with"):

**Definition 13.** X is a whole-program pre-execution when it is of the form  $\langle E, sb, dd, asw, \lambda \rangle$ , where

- $\bullet$  E is a set;

- $sb \subset E \times E$ ;

- $dd \subseteq E \times E$ ;

- $asw \subseteq E \times E$ ;

- $\lambda: E \to A \times \mathbb{N}$ .

In the figures, the events are labelled with the event name and the event label.

To obtain the whole-program pre-executions, C/C++11 takes the product of the per-thread pre-executions:

**Definition 14.** Annotating a per-thread pre-execution (respectively a set of per-thread pre-executions) with a thread identifier t (and no synchronisation):

$$\uparrow_t \langle E, sb, dd, \lambda \rangle = \langle E, sb, dd, \varnothing, \{ (e, (a, t)) \mid (e, a) \in \lambda \} \rangle$$

$$\uparrow_t \mathcal{X} = \{ \uparrow_t X \mid X \in \mathcal{X} \}$$

**Definition 15.** The occurrence of a variable x in a statement s (respectively in a list of statements ss),  $x \in s$  (respectively  $x \in ss$ ), is defined inductively by:

```

\begin{split} &x \in \mathsf{store}_{\mathsf{mo}}(\mathsf{x},\mathsf{e}) \\ &x \in \mathsf{load}_{\mathsf{mo}}(\mathsf{x}) \\ &x \in (\mathsf{r1},\mathsf{r2} = \mathsf{rmw}_{\mathsf{acqrel/acq}}(\mathsf{x},\mathsf{e},\mathsf{e'})) \\ &x \in (\mathsf{if}\; (\mathsf{e}_1\; \mathsf{cmp}\; \mathsf{e}_2) \; \mathsf{ss}_1 \; \mathsf{else}\; \mathsf{ss}_2) \\ &x \in \mathsf{s}_1;...; \mathsf{s}_n \end{split} \qquad \qquad \mathsf{if}\; x \in \mathsf{ss}_1 \vee x \in \mathsf{ss}_2

```

**Definition 16.** The pre-executions of a program  $ss_1 \parallel ... \parallel ss_n$  are

$$\begin{bmatrix} & & & & & & & \\ & E \cup \{n_x \mid x \in Xs\}, & & & & \\ & sb \cup sb', & & & \\ & dd, & & & \\ & \{(n_x,n) \mid x \in Xs \land n \in E\}, & & \\ & \lambda \cup \{n_x \mapsto (\mathsf{W_{na}} \times \mathsf{0}, \mathsf{0}) \mid x \in Xs\} \end{bmatrix} \end{bmatrix}$$

$$\begin{cases} & & & & \\ & \lambda \cup \{n_x \mapsto (\mathsf{W_{na}} \times \mathsf{0}, \mathsf{0}) \mid x \in Xs\} \end{cases} \\ & & & & & \\ & \langle E, sb, dd, \varnothing, \lambda \rangle \in \mathcal{X} \land & \\ & \forall x, y \in Xs. \ x \neq y \Longrightarrow n_x \neq n_y \land \\ & \forall x \in Xs. \ n_x \notin E \land \\ & & total\_order(\{n_x \mid x \in Xs\}, sb') \end{cases}$$

where

$$\mathcal{X} = \left\{ \begin{array}{c} \left\langle E_1 \cup \ldots \cup E_n, \\ sb_1 \cup \ldots \cup sb_n, \\ dd_1 \cup \ldots \cup dd_n, \\ \varnothing, \\ \lambda_1 \cup \ldots \cup \lambda_n \end{array} \right\rangle \\ \left\langle \left\langle E_1, sb_1, dd_1, \varnothing, \lambda_1 \right\rangle, \\ \left\langle \ldots, \\ \left\langle E_n, sb_n, dd_n, \varnothing, \lambda_n \right\rangle \\ \forall i, j \in \{1, \ldots, n\}. \ i \neq j \Longrightarrow E_i \cap E_j = \varnothing \end{array} \right\}$$

and

$$Xs = \{x \mid x \in ss_1 \lor \cdots \lor x \in ss_n\}.$$

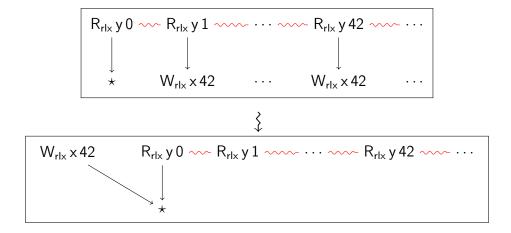

For example, LB+ctrldata+ctrl-double and LB+ctrldata+ctrl-single share the preexecution below (among others):

#### Execution witnesses

An execution witness is a proposal of a justification of "write-to-read" constraints, and of coherence. By mapping each read to a write of the same value to the same location, the rf relation ensures that if a program reads a value from a location, then a thread must write that value to that location at some point. The mo ('modification order') relation embodies coherence. The lo relation imposes a total, alternating order on locks and unlocks at each lock location. The sc relation imposes, for each location, a total order on SC accesses at that location.

For example, the diagram below superimposes an execution witness on top of the preexecution above that justifies each each read of 42 from a location by a thread with a write of 42 to that location by the other thread. *lo* and *sc* are empty because there are no locks or SC accesses. *mo* is empty because it does not involve the initial, non-atomic writes. This example will be considered to be a consistent execution witness in the following.

The diagram below superimposes a different execution witness on top of the same preexecution, that justifies the read of 42 from y by the initial write of 0 to y. This example will not be considered to be a consistent execution witness.

**Definition 17.** W is an execution witness when it is of the form  $\langle rf, mo, lo, sc \rangle$ .

#### Consistency

**Definition 18.** A candidate execution is the pair of a (whole-program) pre-execution and an execution witness.

See the example diagram on Page 17.

The set of candidate executions is filtered by a "consistency" predicate. We sketch the overall structure of the predicate, and some of the details, but refer to Batty et al. [15] and Batty [16] for a more thorough description.

- 1. The consistency predicate first ensures well-formedness of the execution witness. For example, it checks the following:

- 'rf' is a map<sup>5</sup> from the reads of the pre-execution to the writes of the pre-execution. Formally, this is expressed as follows, using auxiliary definitions we

<sup>&</sup>lt;sup>5</sup>A backwards map, with domain and range interchanged.

do not detail:

```

\begin{aligned} \forall (a,b) \in rf. \\ a \in E \land \\ b \in E \land \\ loc\_of(a) = loc\_of(b) \land \\ is\_write(a) \land \\ is\_read(b) \land \\ value\_read\_by(b) = value\_written\_by(a) \land \\ \forall a' \in E. \ (a',b) \in rf \Longrightarrow a = a' \end{aligned}

```

• 'mo' is the union of, for each non-atomic location, a total order on the writes of the pre-execution at that location;

$$(\forall (a,b) \in mo. \ a \in E \land b \in E) \land \\ transitive(mo) \land \\ irreflexive(mo) \land \\ \forall a \in E. \ \forall b \in E. \\ ((a,b) \in mo \lor (b,a) \in mo) \Leftrightarrow \\ \begin{pmatrix} a \neq b \land \\ is\_write(a) \land \\ is\_write(b) \land \\ loc\_of(a) = loc\_of(b) \land \\ \dots \end{pmatrix}$$

- 'lo' is the union of, for each lock location, a total order on the locks and unlocks of the pre-execution at that location that alternates between lock and unlock; and

- 'sc' is a total order on SC accesses.

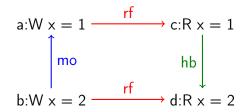

- 2. The consistency predicate then defines several derived relations. The main ones are:

- 'sw' (synchronises-with) represents direct synchronisation, as it arises from a release write to an acquire read that reads from it, from an unlock to the next lock, etc., and including 'asw'; and

- 'hb' (happens-before), represents inherited synchronisation; without consume reads, it is the transitive closure of the union of 'sb' and 'sw'.

- 3. The consistency predicate finally checks that the execution witness justifies the preexecution. For example:

- it checks coherence by checking for the absence of certain shapes (subgraphs) in the candidate execution, for example

• it checks that nonatomic reads read from the latest write at that location in 'hb' (we return to the consequences of this for race detection in Section 9.4.1).

It is sometimes simpler to work with immediate adjacency in mo, which we denote  $mo_1$ , than mo itself:

#### Definition 19.

$$(a,b) \in mo_1 \Leftrightarrow ((a,b) \in mo \land \nexists c. (c \neq a \land c \neq b \land (a,c) \in mo \land (c,b) \in mo))$$

For consistent executions, mo and  $mo_1$  are interdefinable.

**Definition 20.** The executions of a program p are

$$[\![\mathfrak{p}]\!] = \{(X, W) \mid X \in {}^{\mathrm{C}}[\![\mathfrak{p}]\!]^{\mathrm{p}}, \operatorname{consistent}(X, W)\}$$

#### Data races

Finally, C/C++11 checks for the presence of data races, mainly by looking, in consistent executions, for non-atomic accesses that are not totally ordered by hb.

### 2.3.2 Limitations of C/C++11

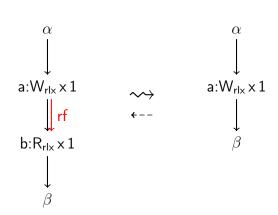

Out-of-thin-air As described in Section 1.2.2, Batty et al. [12] show that there are two programs, LB+ctrldata+ctrl-double and LB+ctrldata+ctrl-single, that share a pre-execution (see Page 17) for which the corresponding behaviour should be allowed for the first, and forbidden for the second. Because these two program share a pre-execution, the C/C++11 memory model cannot be modified to differentiate them just by changing the consistency predicate. Moreover, Batty et al. show that enriching pre-executions with "control dependencies", that is, edges from reads to memory actions inside a control block (like an if) the condition of which syntactically depends on the read (as in Section 1.2.2), is not sufficient either, as the two programs above have the same control dependencies.

Thread-local undefined behaviour As discussed in Section 1.2.4, the C/C++11 language definition fails to integrate the treatment of undefined behaviour and the memory model. This is illustrated by the litmus test in Section 6.7.

## 2.4 The Java Memory Model

## 2.4.1 Description of the JMM

The Java Memory Model of Manson et al. [49] (abbreviated JMM) was the second relaxed memory model for a production programming language<sup>6</sup>. In the JMM, an execution is justified by a sequence of partial executions of the program, where the writes of a partial execution are used to justify the reads of the next partial execution, but where the two partial executions do not have to agree on exactly which control-flow path of the program was taken. This allows the JMM to relax a partial execution by finding another partial

<sup>&</sup>lt;sup>6</sup>The first was the original JMM [35, §17], about which one of its authors, Guy Steele, states that while it "broke new ground [...] in the art of programming language specification", it was "broken" and had "certain obvious technical and practical flaws, and certain other very subtle flaws" [79].

execution that, by relying on reading the same values, can write additional values, thus making taking different branches of the program possible.

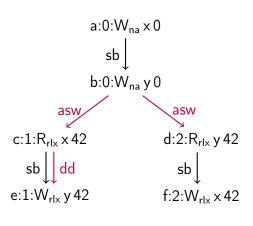

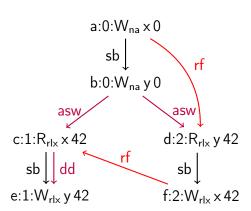

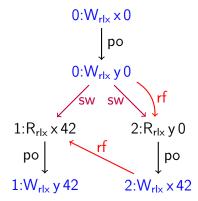

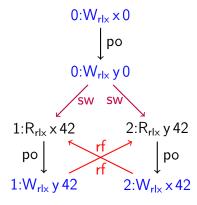

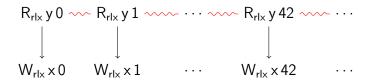

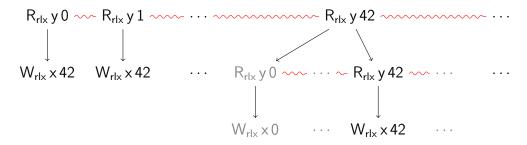

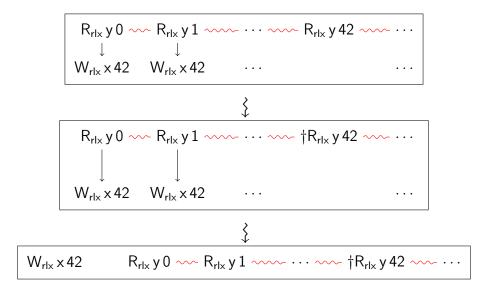

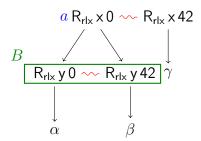

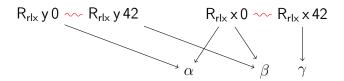

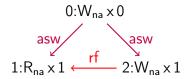

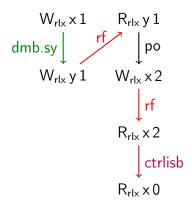

For example, Java (roughly) justifies the outcome of LB+ctrldata+po (Page 16), where both reads read 42, as follows (see Figure 2.2): in the first partial execution (Figure 2.2a), both reads have to read from the initial writes. However, this allows Thread 2 (on the bottom right) to write 42 to x. This write is then visible in the second partial execution (Figure 2.2b) by the read of x, which can read 42, which allows Thread 1 (bottom left) to write 42 to y. This write is then visible in the third partial execution (Figure 2.2c) by the read of y. The actions highlighted in blue are the "committed" actions that are available to justify the next execution of the sequence.

The aim of this approach was to incrementally determine causality by exploring under what conditions an action can safely be executed early. Their solution was to consider this was when data races could be somehow resolved: "early execution of an action does not result in an undesirable causal cycle if its occurrence is not dependent on a read returning a value from a data race" [49, §4.2].

#### 2.4.2 Limitations of the JMM

One of the design goals of the JMM was to avoid out-of-thin-air behaviour. Based on a series of litmus tests, in particular the Java Causality Tests of Pugh [68] (which we describe in Section 6.3), it seemed to achieve this goal. However, Cenciarelli et al. [26] and Ševčík and Aspinall [75] showed that some common compiler optimisations, like common subexpression elimination, are not sound in the JMM. For example, the JMM forbids the outcome of JMM CSE trap of Ševčík and Petri (on Page 46) where all reads read 42, but allows it for LB+ctrldata+ctrl-double (on Page 16), despite the fact that common subexpression elimination turns the former to the latter.

Java compilers perform these optimisations nonetheless, as shown for example by Ševčík and Aspinall for the reference "HotSpot" Java compiler [75], because compiler writers deem these optimisations more important than respecting the JMM. As a consequence, the JMM is not used as the memory model of Java. Instead, programmers have to rely on their knowledge of the compilers and hardware, as illustrated by the concurrency-interest mailing list [1].

Trying again to draw more general intuitive conclusions, the fact that the JMM only requires the *existence* of a sequence of partial executions is surprising, given that hardware and compilers do not consider how an individual execution arises, but rather — by looking at the program as a syntactic object — how all executions arise. There have been attempts to revisit the JMM approach by changing the justification mechanism, for example the work of Jeffrey and Riely, which we discuss in Section 11.1.

## 2.5 Hardware memory models

Memory models for hardware have different design constraints from programming language memory models. As the hardware executes the machine code as it finds it<sup>7</sup>, hardware memory models hinge on *syntactic* program constructs.

<sup>&</sup>lt;sup>7</sup>or works hard to maintain the illusion that it does for sequential contexts.

(a) First partial execution: both reads read the initial value, 0.

(b) Second partial execution: the read of the second thread reads 42

(c) Final execution: both reads read 42

Figure 2.2: Sketch of the justification of the outcome of LB+ctrldata+po where both reads read 42 in the Java memory model. Memory actions that are committed after the partial execution are highlighted in blue. 'po' is program order, 'rf' is reads-from, and 'sw' is thread synchronisation.

**Dependencies** In the program below, because there is an *artificial dependency* between the read and the write in the first thread, hardware forbids the outcome where both reads read 42. An artificial dependency (also known as a "fake" dependency) is a syntactic dependency that does not change the values produced. In the example below, while there is an occurrence of r1 in the expression determining the value written to y, the expression always evaluates to 42, independently of the value of r1:

However, a seemingly benign peephole optimisation that removes this seemingly useless computation turns it into the following program, for which both reads reading 42 is allowed by the Power and ARM architectures, and observed on ARMv7 hardware, because of out-of-order execution:

LB+po+data

$$x = y = 0$$

r1 = load<sub>rlx</sub>(x); r2 = load<sub>rlx</sub>(y);

store<sub>rlx</sub>(y,42) store<sub>rlx</sub>(x,r2)

r1 = r2 = 42 OK

Branching Similarly, hardware memory models ascribe more restricted behaviour to LB+ctrldata+ctrl-double than to LB+ctrldata+po (see Page 16), operationally on the basis that the former features more branches, and architecturally because they respect control dependencies from reads to writes (as far as other threads can observe).

This situation is not completely clear-cut. Some programmers are surprised that peephole optimisations such as removing artificial data dependencies can change behaviour. Hardware architects feel a pressure to move to hardware memory models where these optimisations are sound.

One important principle of these hardware memory models is that they do not feature observable value speculation (except for branch targets, but they do not leak into values for reads and writes): values are constructed by the threads from values they have obtained from "previous" operations (immediate values in the program source, and reads from memory), with respect to a total order (execution order in operational models).

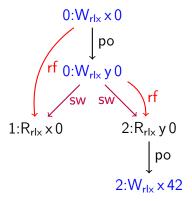

# 2.5.1 The Power memory model

Reference, operational model Sarkar et al. developed an operational model of Power [72, 71, 13] with the aim of faithfully capturing the architectural intent of Power, through extensive discussion with Power architects, and extensive testing against hardware [6]. This model was further refined and interfaced with the Power instruction set architecture by Gray et al. [36]. This is the model we consider in the rest of this section.