# A SIMD architecture for hard real-time systems

Roy Spliet

Fitzwilliam

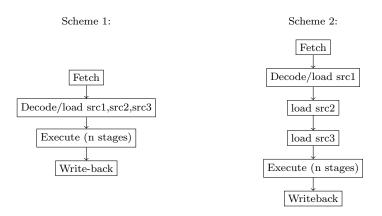

This dissertation is submitted on March 2020 for the degree of Doctor of Philosophy

### DECLARATION

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or am concurrently submitting, for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my dissertation has already been submitted, or is being concurrently submitted, for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. This dissertation does not exceed the prescribed limit of 60 000 words.

> Roy Spliet March 2020

#### Abstract

#### A SIMD architecture for hard real-time systems

#### Roy Spliet

Emerging safety-critical systems require high-performance data-parallel architectures and, problematically, ones that can guarantee tight and safe worst-case execution times. Given the complexity of existing architectures like GPUs, it is unlikely that sufficiently accurate models and algorithms for timing analysis will emerge in the foreseeable future. This motivates a clean-slate approach to designing a real-time data-parallel architecture.

In this work I present Sim-D: a wide-SIMD architecture for hard real-time systems. Similar to GPUs, Sim-D performs *hardware strip-mining* to schedule the work for a compute kernel in entities called *work-groups*. Sim-D schedules the work for each work-group as a sequence of uninterruptible *access-* and *execute program phases*, interleaving the phases of two work-groups. By providing performance isolation between the memory- and compute resources, the execution time of each phase can be tightly bound through static analysis.

I present a predictable closed-page DRAM controller that processes requests for large 1D- and 2D blocks of data, as well as indirect *indexed* transfers. These large transfers coalesce the data requests of a whole work-group. For a linear 4KiB transfer over a 64-bit data bus, the utilisation provably exceeds 78% for DDR4-3200AA DRAM. For 2D blocks, a well-chosen tiling configuration can achieve near-similar efficiency. I show that bounds on the execution time of indexed transfers are pessimistic by nature, but propose a novel *snoopy indexed transfer* mechanism that permits more reasonable bounds when the buffer size is limited.

Finally, I present a worst-case execution time calculation algorithm for Sim-D. This algorithm is paired with two hardware work-group scheduling policies that deterministically reduce run-time variance. The worst-case execution time analysis algorithm combines static control flow analysis with a simulation-based cost model for execution and DRAM transfers. Its key novelty is the addition of a stage that considers work-group scheduling effects. I show that the work-group scheduling policies degrade performance on average by 8.9%, but permit the calculation of worst-case execution time bounds that are tight within 14.3% on average for benchmarks that avoid inefficient indexed transfers.

### Acknowledgements

First and foremost I would like to thank my supervisor, Dr. Robert Mullins, for his continuous support, numerous interesting discussions and pointers to relevant work. I am deeply grateful for the freedom I was given to pursue this project.

Numerous other people in the Department deserve credit for the many on- and off-topic conversations we had throughout the years: my secondary supervisor Prof. Simon Moore, my office mates Alex Bradbury, Sam Ainsworth, Tobias Kohn and Wei Song, my colleagues Daniel Bates, Alex Chadwick, Tim Jones, Theo Markettos and the many others I was privileged to share a corridor or two with.

A special thanks goes out to Dr. Björn Brandenburg for offering me the hands-on introduction to real-time systems research, which provided much inspiration for this work.

I am grateful to my many friends from different colleges and societies who made Cambridge feel like home, the Havana Londres gang for being a solid counterweight on the work-life balance and making London feel like home, my family and long-time friends who remained a beacon of light and made Utrecht feel like home every time I returned, not to forget the many people I've met along the road that have now scattered across the globe. I hope to encounter you again some day.

Finally, I wish to express my gratitude to the late Claire Sparkes who, in the short time I've been privileged to know her, has shared incredible joy and taught me many valuable lessons on empathy, (self-)compassion and looking out for one another on this planet.

# Contents

| 1        | $\operatorname{Intr}$ | oducti  | on                                                             | 19        |

|----------|-----------------------|---------|----------------------------------------------------------------|-----------|

|          | 1.1                   | Contri  | ibutions                                                       | 20        |

|          | 1.2                   | Public  | eation                                                         | 21        |

| <b>2</b> | Bac                   | kgrour  | nd                                                             | <b>23</b> |

|          | 2.1                   | Data-p  | parallel architectures                                         | 23        |

|          |                       | 2.1.1   | Vector processors                                              | 23        |

|          |                       | 2.1.2   | Packed SIMD extensions                                         | 24        |

|          |                       | 2.1.3   | Graphics processing units                                      | 25        |

|          |                       | 2.1.4   | Digital signal processors                                      | 26        |

|          |                       | 2.1.5   | Domain-specific accelerators                                   | 26        |

|          |                       | 2.1.6   | Comparison with Sim-D                                          | 27        |

|          | 2.2                   | DRAN    | A and data layout optimisation                                 | 28        |

|          |                       | 2.2.1   | DDR4 DRAM organisation                                         | 28        |

|          |                       | 2.2.2   | Data layout optimisation                                       | 29        |

|          |                       | 2.2.3   | Edges in filter operations                                     | 32        |

|          | 2.3                   | Real-t  | ime systems                                                    | 32        |

|          |                       | 2.3.1   | Hard real-time DRAM controllers                                | 33        |

|          |                       |         | 2.3.1.1 Closed page: Memory pattern-based HRT DRAM controllers | 34        |

|          |                       |         | 2.3.1.2 Open page: Bank privatisation                          | 36        |

|          |                       |         | 2.3.1.3 Sim-D                                                  | 36        |

|          |                       | 2.3.2   | Hard real-time worst-case execution time analysis              | 37        |

|          |                       |         | 2.3.2.1 Control flow analysis                                  | 37        |

|          |                       |         | 2.3.2.2 Processor behaviour analysis                           | 38        |

|          |                       |         | 2.3.2.3 Bound calculation                                      | 39        |

|          |                       |         | 2.3.2.4 Sim-D                                                  | 39        |

|          | 2.4                   | Miscel  | laneous related work                                           | 40        |

| 3        | A w                   | vide-SI | MD architecture                                                | 43        |

|          | 3.1                   | Overv   | iew                                                            | 43        |

|   |     | 3.1.1   | Instruction set architecture                                                                                                                |

|---|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.2 | Contro  | bl logic                                                                                                                                    |

|   |     | 3.2.1   | Program launch and hardware strip-mining                                                                                                    |

|   |     | 3.2.2   | Assigning global IDs to work-items                                                                                                          |

|   | 3.3 | Pipelir | ne                                                                                                                                          |

|   |     | 3.3.1   | Fetch                                                                                                                                       |

|   |     | 3.3.2   | Decode                                                                                                                                      |

|   |     | 3.3.3   | Execute                                                                                                                                     |

|   |     |         | 3.3.3.1 Compute resources                                                                                                                   |

|   |     |         | 3.3.3.2 Load/store units $\ldots \ldots 52$                                  |

|   |     | 3.3.4   | Write-back                                                                                                                                  |

|   | 3.4 | Contro  | bl flow                                                                                                                                     |

|   |     | 3.4.1   | Vector control flow                                                                                                                         |

|   |     |         | 3.4.1.1 Predicate registers                                                                                                                 |

|   |     |         | 3.4.1.2 Control stack                                                                                                                       |

|   |     | 3.4.2   | Scalar control flow                                                                                                                         |

|   |     | 3.4.3   | Usage example                                                                                                                               |

|   | 3.5 | Data p  | bath $\ldots \ldots \ldots$ |

|   |     | 3.5.1   | Scratchpads                                                                                                                                 |

|   |     | 3.5.2   | Register Files                                                                                                                              |

|   |     |         | 3.5.2.1 Operand interface                                                                                                                   |

|   |     |         | 3.5.2.2 DRAM- and scratchpad interface                                                                                                      |

|   |     |         | 3.5.2.3 Vector register file implementation                                                                                                 |

|   |     |         | 3.5.2.4 n-vector load/stores                                                                                                                |

|   |     | 3.5.3   | Mapped buffers: BufToPhysXlat                                                                                                               |

|   |     | 3.5.4   | Scoreboard                                                                                                                                  |

|   |     |         | 3.5.4.1 Special cases                                                                                                                       |

|   | 3.6 | Summ    | ary                                                                                                                                         |

|   |     |         |                                                                                                                                             |

| 4 | -   |         | ntal set-up 69                                                                                                                              |

|   | 4.1 |         | accurate simulation                                                                                                                         |

|   |     | 4.1.1   | DRAM configuration                                                                                                                          |

|   | 4.2 |         | vorld comparison and OpenCL data acquisition                                                                                                |

|   | 4.3 |         | marks $\ldots \ldots 73$                  |

|   |     | 4.3.1   | CNN                                                                                                                                         |

|   |     | 4.3.2   | KinectFusion                                                                                                                                |

|   |     | 4.3.3   | SRAD                                                                                                                                        |

|   |     | 4.3.4   | MRI-Q                                                                                                                                       |

|   |     | 4.3.5   | SPMV                                                                                                                                        |

|          |     | 4.3.6  | LU Decomposition                                                                                                                                                        |

|----------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 4.3.7  | Stencil                                                                                                                                                                 |

|          |     | 4.3.8  | FFT                                                                                                                                                                     |

|          | 4.4 | Limita | ations                                                                                                                                                                  |

|          | 4.5 | Summ   | nary                                                                                                                                                                    |

| <b>5</b> | A h | ard re | al-time DRAM controller 79                                                                                                                                              |

|          | 5.1 | Limita | ations of pattern-based hard real-time HRT DRAM controllers 80                                                                                                          |

|          |     | 5.1.1  | Inefficiency on modern DRAM                                                                                                                                             |

|          |     | 5.1.2  | Variation in transfer sizes                                                                                                                                             |

|          |     | 5.1.3  | Alignment constraints                                                                                                                                                   |

|          |     | 5.1.4  | Takeaway points                                                                                                                                                         |

|          | 5.2 | Buffer | characterisation and data locality                                                                                                                                      |

|          | 5.3 | Archit | tecture                                                                                                                                                                 |

|          |     | 5.3.1  | Pipeline                                                                                                                                                                |

|          |     |        | 5.3.1.1 Front-end                                                                                                                                                       |

|          |     |        | 5.3.1.2 Command generator                                                                                                                                               |

|          |     |        | 5.3.1.3 Command arbiter                                                                                                                                                 |

|          |     |        | 5.3.1.4 DQ scheduler                                                                                                                                                    |

|          |     | 5.3.2  | Snoopy indexed transfers                                                                                                                                                |

|          |     |        | 5.3.2.1 Data snoop unit $\ldots \ldots 102$             |

|          |     |        | 5.3.2.2 Stride sequencer $\ldots \ldots \ldots$         |

|          |     | 5.3.3  | Takeaway points                                                                                                                                                         |

|          | 5.4 | Worst  | -case request execution time and issue delay                                                                                                                            |

|          |     | 5.4.1  | Unit-stride                                                                                                                                                             |

|          |     |        | 5.4.1.1 Four or more bank-groups $\ldots \ldots \ldots$ |

|          |     | 5.4.2  | Non-unit-stride                                                                                                                                                         |

|          |     | 5.4.3  | Index iteration                                                                                                                                                         |

|          |     |        | 5.4.3.1 Four or more bank groups $\ldots \ldots 115$                                              |

|          |     | 5.4.4  | Snoopy indexed transfers                                                                                                                                                |

|          |     | 5.4.5  | Takeaway points                                                                                                                                                         |

|          | 5.5 | Evalu  | ation                                                                                                                                                                   |

|          |     | 5.5.1  | Unit-stride transfers                                                                                                                                                   |

|          |     | 5.5.2  | Non-unit-stride transfers                                                                                                                                               |

|          |     | 5.5.3  | Indexed transfers                                                                                                                                                       |

|          | 5.6 | Summ   | nary $\dots \dots \dots$                                                |

| 6 | Des | ign sp  | ace exploration                             | 127   |

|---|-----|---------|---------------------------------------------|-------|

|   | 6.1 | Resou   | rce usage characterisation                  | . 128 |

|   |     | 6.1.1   | NVIDIA Kepler                               | . 128 |

|   |     | 6.1.2   | Sim-D                                       | . 134 |

|   |     | 6.1.3   | Takeaway points                             | . 137 |

|   | 6.2 | Paran   | neter sensitivity                           | . 137 |

|   |     | 6.2.1   | Scratchpad bus width                        | . 138 |

|   |     | 6.2.2   | Compute configurations                      | . 139 |

|   |     | 6.2.3   | Takeaway points                             | . 143 |

|   | 6.3 | Avera   | ge case performance comparison              | . 144 |

|   | 6.4 | Hardw   | vare-supported optimisation                 | . 147 |

|   |     | 6.4.1   | n-vector load/stores                        | . 147 |

|   |     | 6.4.2   | Warp trimming                               | . 150 |

|   |     | 6.4.3   | Takeaway points                             | . 152 |

|   | 6.5 | Summ    | nary                                        | . 152 |

| 7 | Wo  | rst-cas | e execution time analysis                   | 155   |

|   | 7.1 |         | ation for work-group scheduling constraints | . 156 |

|   |     | 7.1.1   | DRAM variance and schedule search space     | . 157 |

|   |     | 7.1.2   | Scheduling policies                         | . 160 |

|   | 7.2 | Progra  | am- and execution model                     |       |

|   |     | 7.2.1   | Worst-case minimal valid schedule           | . 163 |

|   |     | 7.2.2   | Work-group early exit                       | . 166 |

|   |     | 7.2.3   | Complexity and bounds                       |       |

|   |     | 7.2.4   | Takeaway points                             |       |

|   | 7.3 | Hard :  | real-time work-group scheduling policies    | . 170 |

|   |     | 7.3.1   | Launching work-groups in pairs              |       |

|   |     | 7.3.2   | Two-resource scheduling                     | . 173 |

|   |     | 7.3.3   | Takeaway points                             | . 174 |

|   | 7.4 | WCE     | T computation algorithm                     |       |

|   |     | 7.4.1   | Parsing the program                         | . 175 |

|   |     | 7.4.2   | Control flow analysis                       |       |

|   |     | 7.4.3   | Worst-case performance simulation           |       |

|   |     | 7.4.4   | Construct a DAG                             |       |

|   |     | 7.4.5   | Critical path analysis                      |       |

|   |     | 7.4.6   | Access/execute program phase lists          |       |

|   |     | 7.4.7   | WCET computation                            |       |

|   |     | 7.4.8   | DRAM refresh inflation                      |       |

|   | 7.5 |         | ation                                       |       |

|              |                                 | 7.5.1                                           | Average-case performance                                                                                                                                   | 183                                    |

|--------------|---------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|              |                                 | 7.5.2                                           | Worst-case execution time $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                          | 185                                    |

|              |                                 | 7.5.3                                           | Software optimisation techniques                                                                                                                           | 187                                    |

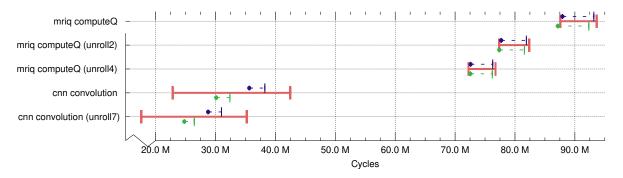

|              |                                 |                                                 | 7.5.3.1 Loop unrolling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                             | 187                                    |

|              |                                 |                                                 | 7.5.3.2 Instruction scheduling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                          | 189                                    |

|              |                                 |                                                 | 7.5.3.3 2D tiling                                                                                                                                          | 190                                    |

|              |                                 | 7.5.4                                           | Takeaway points                                                                                                                                            | 191                                    |

|              | 7.6                             | Summ                                            | ary                                                                                                                                                        | 192                                    |

| 0            | C                               | 1.                                              |                                                                                                                                                            | 105                                    |

| 8            |                                 | clusio                                          |                                                                                                                                                            | 195                                    |

|              | 8.1                             | Future                                          | e work                                                                                                                                                     | 196                                    |

| Bi           | bliog                           | raphy                                           |                                                                                                                                                            | 199                                    |

| $\mathbf{A}$ | ISA                             |                                                 |                                                                                                                                                            | 211                                    |

|              | A.1                             | Conve                                           | ntions                                                                                                                                                     | 211                                    |

|              | A.2                             | Regist                                          | er specifications                                                                                                                                          | 211                                    |

|              | A.3                             | Floatin                                         | ng point arithmetic                                                                                                                                        | 212                                    |

|              | A.4                             |                                                 |                                                                                                                                                            | •••===                                 |

|              | 11.1                            | Recipr                                          | cocal/Trigonometry (expensive FP arith)                                                                                                                    |                                        |

|              | A.5                             | -                                               |                                                                                                                                                            | 215                                    |

|              |                                 | Integer                                         | rocal/Trigonometry (expensive FP arith)                                                                                                                    | 215<br>215                             |

|              | A.5                             | Integer<br>Data o                               | rocal/Trigonometry (expensive FP arith)                                                                                                                    | 215<br>215<br>222                      |

|              | A.5<br>A.6                      | Integer<br>Data o<br>Load/                      | rocal/Trigonometry (expensive FP arith)                                                                                                                    | 215<br>215<br>222<br>224               |

|              | A.5<br>A.6<br>A.7<br>A.8        | Integer<br>Data o<br>Load/S<br>Contro           | rocal/Trigonometry (expensive FP arith)                                                                                                                    | 215<br>215<br>222<br>224<br>229        |

|              | A.5<br>A.6<br>A.7<br>A.8<br>A.9 | Integer<br>Data o<br>Load/2<br>Contro<br>Predic | cocal/Trigonometry (expensive FP arith)           r/Boolean arithmetic           copy, conversion and intra-lane shuffle           Store           ol flow | 215<br>215<br>222<br>224<br>229<br>232 |

# GLOSSARY

- **address mapping** As a noun, refers to the scheme used to translate a physical address to its corresponding DRAM channel, rank, bank-group, bank, row and column. Used as a verb to describe the act of translation.

- **ALAP** as late as possible.

- **ASOM** addition, single-overflow modulo.

- **BB** basic block.

- **CAM** content-addressable memory.

- **CAS** Column Access Strobe, delay between issuing a read command and the first data word appearing on the DQ.

- CCD CAS to CAS delay.

- CFA control flow analysis.

- CFG control-flow graph.

- CMASK control mask.

- **CNN** convolutional neural network.

- compute unit Hardware unit that performs the computation for some or all work-groups.

- CSTACK control stack.

- **CWD** Column Write Delay, delay between issuing a write command and writing the first data word to the DQ.

- DAG directed acyclic graph.

- device Massively-parallel accelerator, e.g. GPU, FPGA, DSP.

- **DMA** direct memory access.

$\mathbf{D}\mathbf{Q}$  data bus.

$\mathbf{DQM}\xspace$  data mask.

- **DRAM pattern** Fixed schedule of DRAM commands, statically scheduled by a DRAM controller to service a request spanning a fixed number of consecutive, aligned bytes of data.

- **DSA** domain specific architecture.

- **DSP** digital signal processor.

- FAW four-activate window.

- **FFT** fast-fourier transform.

- GPGPU General-Purpose compute on Graphics Processing Unit.

- **GPR** general-purpose register.

- GPU graphics processing unit.

- GTRR greedy-then-round-robin.

- **HRT** hard real-time.

- **ILP** integer linear programming.

- **IMem** instruction memory.

- index iterator Sub-component in the DRAM controller front-end responsible for translating a request in the form of a set of indexes into a buffer into burst requests.

- **IPET** implicit path enumeration.

- ${\bf IR}\,$  intermediate representation.

- **ISA** instruction set architecture.

- **JDS** jagged diagonal storage.

- kernel A non-interactive function designed to run on a device.

- **kernel-instance** An instantiation of a kernel on the device as it is launched by the host system, with it's parameters, buffer objects and compiled kernel..

LID longest issue delay.

**local memory** A fast addressable storage region private to a work-group. CUDA: shared memory.

${\bf LUT}$  look-up table.

**NDRange** N-Dimensional range, describing the dimensions of the grid of work-items launched for a kernel-instance.

pattern transaction Execution of a single DRAM pattern.

**PBA** processor-behaviour analysis.

**PBGI** paired bank-group interleaving.

PC program counter.

$\mathbf{PR}$  (vector) predicate register.

RCP-unit reciprocal/trigonometry unit.

**remainder work-group** work-group for which at least one thread falls outside the kernelinstances' thread dimensions.

$\mathbf{RF}$  register file.

**RRD** row-activate to row-activate delay.

SGPR general purpose scalar register.

**SIMD** single-instruction multiple-data.

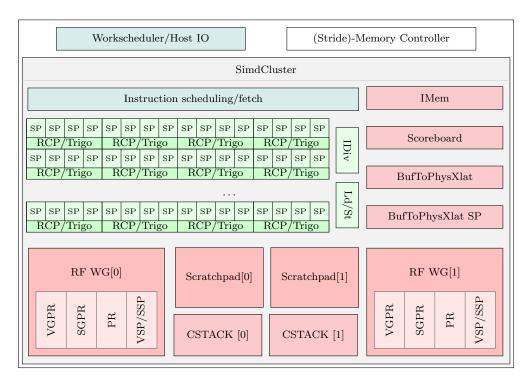

SimdCluster Sim-D's compute unit.

$\mathbf{SIMT}$  single-instruction multiple-threads.

**SLAM** simultaneous localisation and mapping.

$\mathbf{SP}$ -unit single-precision unit.

**SPMD** single program multiple-data.

**SSP** special purpose scalar register.

**stride sequencer** Sub-component in the DRAM controller front-end responsible for translating a request in the form of a 2D stride pattern into burst requests.

- **TID** global ID (OpenCL) or thread ID (CUDA), a multi-dimensional identifier within the NDRange unique to a work-item.

- VGPR general purpose vector register.

- **VRF** vector register file.

- **VSP** special purpose vector register.

- **warp trimming** Technique for reducing the number of scheduled warps when executing remainder work-groups.

- $\mathbf{WCET}\xspace$  worst-case execution time.

- WCRET worst-case request execution time.

- **work-group** Collection of work-items that are guaranteed to run on a single compute unit.

- work-item A single thread of a kernel execution.

# CHAPTER 1

# INTRODUCTION

There are many emerging examples of cyber-physical systems that demand both significant compute and hard real-time (HRT) support. In automotive, the shift towards more autonomous vehicles requires running time-critical image processing, AI classification and decision making algorithms on-board [1]. In medical imaging, many algorithms use graphics processing units (GPUs) to achieve lower processing times and higher resolution visualisations [2]. The image processing, neural networks and dense-matrix operations required for these and many other safety-critical applications all exhibit large amounts of data parallelism. To pursue ambitious goals in these fields, researchers and equipment manufacturers are increasingly looking at applying semi-specialised massively parallel accelerators in their devices. Hardware vendors are keen to fill this gap in the market, with e.g. NVIDIA recently releasing their Drive PX1 platform for automotive [3].

An important property distinguishing hard real-time (HRT) systems from regular systems is the stringent deadlines such systems must meet. For HRT systems, the throughput offered by any given hardware platform is only valuable if a *safe* and *tight* bound can be placed on the worst-case execution time (WCET) of the tasks it performs.

It is then unfortunate that, although WCET calculation methods have been researched for GPUs programs [4, 5], none of these methods are able to derive safe bounds for commercially available hardware. The main problem preventing the derivation of safe bounds is the complexity of the hardware. GPUs have over the years developed themselves into a Swiss army knife of graphics processing, containing dedicated subcomponents for compute, video encoding and decoding, data transfers between the host and the device, display scan-out, texture operations, rasterising and possibly many other purposes. When these subcomponents all make use of the GPU's shared memory hierarchy in parallel, latencies on read and write requests are highly unpredictable. This can lead to unexpected timing anomalies [6] that may be difficult to model or reason about in a real-time context.

Even if it is possible to disable all those components that are unused in HRT systems,

the GPU's execution model is difficult to reason about. The very fine grain warp-scheduling mechanisms, designed to make the GPU strongly resilient to high DRAM latencies, permit such a wide range of warp interleavings that practical analysis of all possible program executions is infeasible. Without a solid understanding of the worst-case warp interleavings, it seems impossible to claim a WCET bound as safe.

Given the problem of WCET analysis of programs running on massively parallel accelerators, the potential solutions are obvious: either construct more sophisticated models for existing hardware, or create simpler hardware. In the light of the corporate secrecy that exists around current architectures, it is my expectation that the former approach leads to a dead end. Taking the GPU's memory system as an example, is it reasonable to assume that the DRAM controller re-orders requests to maximise throughput. Request re-ordering could theoretically lead to starvation, where a request is continuously placed at the back of the queue in favour of higher priority requests. A DRAM controller can safeguard against starvation by taking a request's age into account when determining its priority. However, there is no public knowledge available for any GPU that unequivocally guarantees starvation-free request prioritisation. Without even such basic guarantees, it seems unwise to assume that safe WCET bounds exist, let alone such bounds being sufficiently tight for practical purposes. A more promising approach is then to design hardware from the ground up with hard real-time requirements and principles in mind.

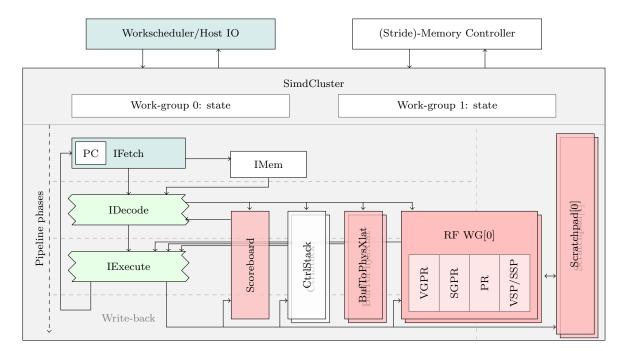

In this work, I present Sim-D: a wide-SIMD architecture designed for hard real-time systems. Similar to GPUs, Sim-D performs hardware strip-mining to schedule the work for a compute kernel in entities called work-groups. Inspired by the *PRedictable Execution Model* (PREM) [7], Sim-D schedules the work for each work-group as a sequence of uninterruptible access- and execute program phases, interleaving the phases of up to two work-groups at a time. Owing to the strict performance isolation between Sim-D's compute- and storage resources, the execution time of each access- and execute phase can be tightly bound through static analysis. Static WCET derivation of a kernel-instance is then achieved through an analysis of the possible interleavings of these phases. Various scheduling policies are enforced in hardware to reduce the number of possible interleavings. The result is a WCET analysis algorithm tailored to the Sim-D architecture that derives a safe bound tight within 14.3% on average.

### **1.1** Contributions

My thesis is that an efficient wide-SIMD accelerator can feasibly be designed that permits the derivation of safe and tight bounds on the execution time of data-parallel programs. To support this thesis, in this work I contribute the following:

• I introduce the Sim-D architecture, a wide-SIMD processor that is designed to permit

WCET analysis. Sim-D provides *performance isolation* between its compute and data storage resources such that parallel occupation does not introduce pessimism to a program's WCET, (Chapter 3)

- I introduce the experimental set-up used for the evaluation in this work, (Chapter 4)

- I present Sim-D's closed-page DRAM controller, capable of servicing large requests for 1D or 2D regions of data in bound time. Along with its design, I provide the necessary analysis methods to derive worst-case request execution time bounds on each transfer, (Chapter 5)

- I perform a design space exploration of Sim-D, in order to justify its design decisions and to derive sensible parameters for the experiments in this work, (Chapter 6)

- I show that Sim-D is capable of achieving performance on par with an embedded-grade commercial GPU, (Chapter 6)

- I introduce a WCET analysis algorithm that permits efficient derivation of safe bounds on a program's execution time. To support this algorithm, I introduce both a tailored program- and system model, and I introduce two work-group scheduling policies that introduce a 8.9% run-time overhead on average. Ignoring outliers, the resulting WCET bounds are shown to be tight within 14% on average, (Chapter 7)

- I evaluate the impact of several known program optimisations on the WCET of a program running on Sim-D. (Chapter 7)

# 1.2 Publication

Research carried out as part of this study has resulted in the following publication:

• R. Spliet and R. Mullins. *The case for limited-preemptive scheduling in GPUs for real-time systems.* In ECRTS, Operating Systems Platforms for Embedded Real-Time applications, Jul 2018. [6]

# CHAPTER 2

# BACKGROUND

In this chapter I set out to explain the necessary terminology and relevant work that led up to the design and evaluation of Sim-D.

Specifically I contribute the following:

- An overview of the classes identified in the landscape of data-parallel architectures and the position Sim-D occupies in this space (Section 2.1),

- A short introduction to DDR4 DRAM and data layout optimisation techniques relevant to GPUs (Section 2.2),

- An explanation of related work in hard real-time DRAM controllers, worst-case timing analysis techniques and other related work that inspired the design of Sim-D (Section 2.3).

### 2.1 Data-parallel architectures

This section summarises several classes of data-parallel architectures, with the goal of explaining Sim-D's position in the landscape. The presented taxonomy is largely drawn from Hennessy and Patterson [8].

#### 2.1.1 Vector processors

In broad terms, vector processors are processors that support instructions to perform arithmetic operations on every element of an array. A defining feature of a vector processor is that the length of this array is run-time configurable, anywhere between 1 and the maximum number of elements that can be stored by their SRAM- or register-backed array storage. Such vector processor designs go back to the 1960s with the presentation of the ILLIAC IV [9]. More recent examples include the HWACHA architecture [10] and ARM's Scalar Vector Extension (SVE) [11].

Three complementary techniques are used to process vectors of independent elements in a single-instruction multiple-data (SIMD) fashion. Firstly, *pipelining* permits a throughput of one vector element per cycle. Control logic ensures that for a given vector instruction, the operation is issued as many times as required to process the every element in the vector. Secondly, *vector chaining* [12] permits multiple vector instructions to overlap provided there are no hazards. For example, if a vector load operation is followed by a vector addition of said vector with a different element, the vector addition can start processing the first element of the vector as soon as it arrives, rather than waiting for the entire load operation to finish. Chaining m instructions could therefore result in an IPC approaching m. Finally, duplication of arithmetic units permits performing a vector operation for multiple elements in parallel in the same cycle. A parallel processor capable of performing n arithmetic operations in parallel are said to have n (vector-)*lanes*.

Transforming a loop of scalar operations into a loop of vector operations is called *strip* mining [13]. Given a vector processor with a maximum array length  $l_{max}$ , strip-mining is performed explicitly in assembly by replacing any scalar loop iterating over n elements with a loop that performs  $\left\lceil \frac{n}{l_{max}} \right\rceil$  iterations, each iteration issuing the vector arithmetic for up to n elements.

#### 2.1.2 Packed SIMD extensions

To speed up applications that perform digital signal processing or graphics operations on application processors, several instruction set architectures (ISAs) have been extended with packed SIMD operations. These operations borrow from the parallel-processing concepts of vector processors. Early extensions were designed to re-use existing resources from high-end application processors. For example, Intel's MMX-extension [14] does not introduce specialised vector storage, but *packs* vectors of  $2 \times 32$ -bit,  $4 \times 16$ -bit or  $8 \times 8$ -bit elements into existing x87 floating point registers.

Over time, packed SIMD extensions have converged with vector processor architectures. This is most evident from the storage reserved for vector elements: where for MMX the size of a vector was limited to 64-bits [14], the current-generation AVX-512 [15] extension offers dedicated vector registers of 512 bits each. For comparison, ARM SVE [11] can offer up to 2048 bits of storage per vector.

Today, the main distinguishing property of packed SIMD extensions is that the number of elements in a vector is fixed to the width of the register rather than configurable at run-time. Packed SIMD extensions may define instruction variants for different register widths. If arrays are shorter or elements must be skipped, a predicate mask can inform instructions which elements of a vector register must be processed. Predicate masks have no influence on performance, rather they determine which results must be written back to the destination vector register and which should be discarded.

Packed SIMD operations are part of the application processor's ISA. As such, their execution does not incur overheads paid for uploading the kernel code and data-set to an external accelerator, like it would be the case with GPUs or digital signal processors (DSPs). However, their throughput is generally only a fraction of the throughput achieved even on a embedded GPU.

#### 2.1.3 Graphics processing units

Since the advent of 3D gaming, GPUs have gradually developed into a distinct class of massively-parallel processors. After several research projects aimed at utilising the GPUs resources for non-graphics applications (e.g. BrookGPU [16]), NVIDIA's CUDA was the first commercially available architecture to offer general purpose usage of their GPU [17]. Like vector processors and packed SIMD extensions, GPUs apply pipelining and lock-step parallel execution of operations on vector elements to reduce control overhead, resulting in energy-efficient high-throughput processing of data-parallel kernels. However, their hardware strip-mining single-instruction multiple-threads (SIMT) programming model make GPUs unique in their capabilities to effectively occupy several thousands arithmetic units and other resources in parallel.

GPUs rigorously part with the concept of processing vector elements in order. Instead, conceptually a GPU work scheduler breaks vectors into *warps*, groups of 32 (NVIDIA) or 64 (AMD) elements. Each warp is processed in a separate hardware thread, with the operations for the warp performed in SIMD. Each *compute unit* in a GPU can issue multiple instructions per cycle from a plurality of warps. The large pool of active warps helps to mask data movement latencies between the memory hierarchy and the individual warps, maximising occupancy of the available compute- and memory resources.

To illustrate the scale of a compute unit, each "SMX" in an NVIDIA Kepler GPU [18] contains 192 single-precision units (SP-units) for integer and floating-point arithmetic, 32 load/store units, 32 special function units (used for e.g. trigonometry operations) and various other units required mostly for graphics operations. A high-end GeForce 780Ti GPU contains 15 compute units [19]. At any time, a compute unit can have 64 active warps divided over four warp-schedulers. Each warp-scheduler can issue one or two instructions per cycle.

Warp scheduling requires the GPUs to perform strip-mining in hardware. To this end, an application that wishes to off-load computation to the GPU launches a *kernel-instance* parametrised with its desired vector size. This size, called the *NDRange*, is specified in up to 3 dimensions, and dictates how many work-items must be launched. Work-items are identified by a global ID (TID), a unique identifier in the NDRange space. Work-items are grouped into *warps*, in turn grouped into *work-groups*. All warps in a work-group execute on a single compute unit, allowing a work-group to share data between its work-items.

Contrary to vector processors and packed SIMD extensions, developers treat the GPU as an external device. Relevant vectors and other parameters must be uploaded to dedicated DRAM local to the GPU. Kernels, non-interactive functions running on the GPU, are developed according to the single program multiple-data (SPMD) paradigm: code specifies the work that needs to be performed for a single work-item, relying on hardware strip-mining to run this code for every work-item.

#### 2.1.4 Digital signal processors

DSPs are frequently found in embedded systems that perform filtering, transformation and error-correction of digital signals. Although their architectures vary, most are best categorised as VLIW processors with data-parallel processing capabilities, using narrowword SIMD techniques [20–22] for increased throughput of arithmetic operations like multiply-accumulate.

DSPs are used to fulfil HRT tasks. For example, Qualcomm's baseband modem is paired with two dedicated DSPs to perform latency-sensitive audio-processing tasks [20]. To this end, pipelines are kept simple, multi-threading is limited to a few hardware threads and input data may be processed through dedicated channels rather than over shared buses. Software running on DSPs is generally persistent by nature, rather than acting as a CPU-controlled accelerator device.

Exceptionally, the Qualcomm Hexagon DSP permits user-space applications running on their mobile SoCs to upload custom kernels for execution. This brings the DSP's role and design closer to that of a GPU.

#### 2.1.5 Domain-specific accelerators

Domain specific architectures (DSAs) are architectures that are highly optimised for a single task, trading general applicability for performance and power efficiency. Such architectures play a prominent role in the domains of video decoding (e.g. NVIDIA Falcon [23]) and machine learning (e.g. TPU [24], NVDLA [25] and GraphCore [26]). Besides their application in specialised high performance computing, DSAs are often used in power-constrained mobile systems.

DSAs can be tailored to their task in various ways. Firstly, compute resources are designed to closely match the precision requirements of the task. Secondly, the ISA of a specialised accelerator usually contains application-specific vector instructions. Such instructions may have non-standard result modifiers or even follow VLIW encoding practices to maximise code density. These modifiers or fused instructions are matched with a non-standard pipeline to perform the task at hand as quickly as possible. Finally, memory hierarchies are tuned to the data requirements of the task, for example by replacing associative caches with scratchpads or introducing single-purpose buffers.

#### 2.1.6 Comparison with Sim-D

Sim-D is designed as a general-purpose wide-SIMD accelerator tailored to HRT systems. The targeted applications are inspired by recent trends in autonomous safety-critical systems, such as assisted driving. Domains include computer vision, artificial intelligence but also digital signal processing. Latencies and deadlines of such applications are often expressed in (tens of) milliseconds [1, 27], one or two orders of magnitude larger than that of most DSP applications and of control tasks like e.g. software-controlled fuel injection in car engines. In the light of such latencies, fixed overheads for communication and task scheduling have a relatively small impact on the overall execution time of a task. This combination of large data-parallel workloads and relatively low cost of fixed scheduling overheads resulted in Sim-D's design to resemble existing GPUs. Besides wide-SIMD execution, this is reflected in the way Sim-D performs hardware strip-mining and permits parallel scheduling of multiple hardware threads processing the same vector.

Compared to a contemporary GPU, Sim-D's unit of scheduling is more coarse-grain: where GPUs operate on warps, Sim-D's compute unit schedules operations at a work-group granularity, each work-group containing 1024 work-items. Work-items within a work-group are processed like in a regular multi-lane pipelined vector processor, without the use of chaining techniques. Instead, parallel occupation of resources is increased by interleaving the execution of two work-groups at any point in time. While such coarser-grain scheduling reduces the ability for parallel occupation of resources, it increases the predictability of instruction scheduling and data movements. This predictable execution allows Sim-D's to provide WCET bounds on the run-time of kernel-instances, as explained in Chapter 7.

In terms of resources, Sim-D currently positions itself as an embedded-grade accelerator. It features a 64-bit DRAM bus and a single compute unit. Scaling this design up towards the DRAM bus and compute resources of a discrete GPU comes with specific challenges to the memory controller and the WCET analysis algorithm. I will outline these challenges throughout the dissertation, but leave their resolution for future work.

Despite its resemblance to a GPU, Sim-D does not aim to implement a graphics pipeline. Although it is conceivable that the compute resources can be used for some graphics-related computation, it lacks features specific to 3D-rendering such as texture sampling or rasterising.

Sim-D's ISA more closely resembles that of a vector processor, explicitly mixing vectorand scalar instructions in an otherwise RISC-like ISA. That being said, Sim-D is not an application processor. Its ISA borrows heavily from NVIDIA's GPU ISAs, and omits the hardware I/O and timing features required to run an operating system. Unique to Sim-D is the ability to issue large DRAM requests for 1D- and 2D blocks of data for an entire work-group, which is then processed by the DRAM controller in parallel with compute for another work-group.

# 2.2 DRAM and data layout optimisation

In this section, I present an abstraction of DRAM as relevant to the understanding of this thesis. This explanation is followed by an explanation of common data layout optimisation considerations for GPUs. For a more complete overview of the internals and operation of DRAM, I refer the reader to "Memory Systems : Cache, DRAM, Disk" [28].

### 2.2.1 DDR4 DRAM organisation

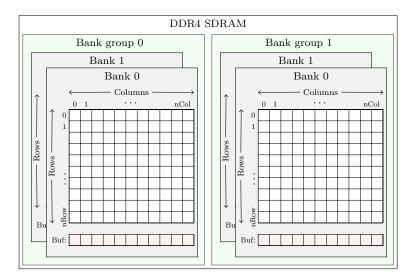

Figure 2.1: Schematic abstraction of a DDR4 DRAM chip

A DDR4 DRAM chip consists of multiple *bank groups*, each containing an equal number of *banks*. Each bank contains a 2D-grid of memories, organised as *rows* and *columns*. Each bank additionally contains a *row buffer*. A DRAM chip's interface consists of a clock input, command- and address signals, a chip select input, a data mask (DQM) input and a bidirectional data bus (DQ).

The DQ width of a memory chip specifies the number of data lines, and thus the number of bits it transfers in a single cycle. A rank is generally formed of multiple DRAM chips in parallel. For example, a 64-bit wide rank can consist of 8 chips with a DQ width of 8, or 4 chips with a DQ width of 16. A channel consists of a set of data- and command lines that are shared between one or more ranks. Each channel has a one-hot bit mask

to select the destination rank for each command. In this work, I only consider a channel containing a single rank.

Data is requested in *bursts*. For DDR4 DRAM, a burst consists of 8 beats. In other words, each request issues a read or write to 8 consecutive columns in a row. Write operations can be performed at a byte granularity by clearing each byte's corresponding bit in the DQM for each beat of a burst. In this work all latencies are measured in clock cycles of the command bus. Being *double data rate* DRAM, a burst is thus said to complete its transfer in 4 cycles. Transfers must be aligned to a multiple of a burst.

Operating DRAM is done using three operations: activation, read/write and precharge. Activation brings the data from a row into the row buffer of the respective bank. Read and write operations transfer data between the row buffer and the requestor. Finally, precharge conceptually writes back data to the DRAM cells and prepares the row-buffer for the next activation of that bank.

Physical properties of the DRAM chip place constraints both on the latencies of each operations and on the distance that must be guaranteed between two operations. A chip's set of constraints is referred to as its *DRAM timings*. Although banks are conceptually parallel independent entities within a chip, constraints exist on the minimal distance between e.g. two activation operations to different banks. In DDR4, the minimal distance between two consecutive operations issued to different bank groups is shorter than the same operations issued to banks in the same bank group. A full overview of all dimensions and timings for the Micron MT40A512M16JY-062E and MT40A1G8SA-062E DDR4-3200 DRAM chips is given in Section 4.1.1.

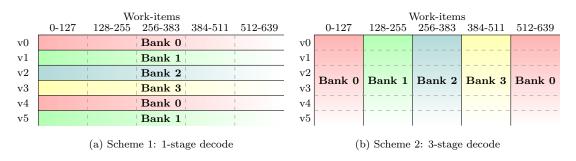

#### 2.2.2 Data layout optimisation

It is generally accepted that the performance of most GPU compute (GPGPU) kernels is bound by DRAM throughput. In turn, optimisation guides (e.g. AMD [29], Intel [30], NVIDIA [31]) discuss programming techniques that improve memory throughput of kernel-instances. Three themes emerge: data alignment with respect to DRAM or cache lines, coalesced accesses of work-items in a warp and reducing DRAM accesses by using local memory to share data between work-items in a work-group. From the architect's perspective, these techniques are interesting as they both determine the requirements applications impose on a hardware design as well as set out the scope for optimisations of common cases within the memory subsystem.

GPUs have the ability to coalesce memory requests of work-items when they access data elements from the same cache line or DRAM burst. A straightforward way of maximising the potential of request coalescing is to structure data such that there is a linear mapping from a work-item's TID and its requested data element from a buffer.

For this reason, structuring data as a struct-of-arrays is preferred over an array-of-

*structs.* As a concrete example, consider a buffer for which each data element consists of four components: x, y, z and w. Figure 2.2 shows how this data is laid out in memory under both an array-of-structs and an struct-of-arrays arrangement for 16 work-items. Each row aligns to a DRAM burst.

| $_{0,x}$ | 0,y  | $_{0,z}$ | $_{0,w}$ | $^{1,\mathrm{x}}$ | $^{1,y}$ | $^{1,z}$ | $^{1,w}$ | $^{2,\mathrm{x}}$ | $^{2,y}$ | $^{2,z}$ | $^{2,w}$ | $_{3,x}$          | $_{3,y}$ | $^{3,z}$ | 3,w  |

|----------|------|----------|----------|-------------------|----------|----------|----------|-------------------|----------|----------|----------|-------------------|----------|----------|------|

| 4,x      | 4,y  | $^{4,z}$ | $^{4,w}$ | $^{5,\mathrm{x}}$ | $^{5,y}$ | $^{5,z}$ | $^{5,w}$ | $_{6,\mathrm{x}}$ | $_{6,y}$ | $_{6,z}$ | $_{6,w}$ | $^{7,\mathrm{x}}$ | 7,y      | $^{7,z}$ | 7,w  |

| 8,x      | 8,y  | 8,z      | $^{8,w}$ | $_{9,x}$          | 9,y      | 9,z      | 9,w      | 10,x              | 10,y     | 10,z     | 10,w     | 11,x              | 11,y     | 11,z     | 11,w |

| 12,x     | 12,y | 12,z     | 12,w     | 13,x              | 13,y     | 13,z     | 13,w     | 14,x              | 14,y     | 14,z     | 14,w     | 15,x              | 15,y     | 15,z     | 15,w |

a) Array-of-structs

|      | $_{0,\mathrm{x}}$ | 1,x      | 2,x      | 3,x      | 4,x      | $^{5,\mathrm{x}}$ | 6,x      | 7,x | 8,x      | 9,x      | 10,x | 11,x | 12,x | 13,x | 14,x |

|------|-------------------|----------|----------|----------|----------|-------------------|----------|-----|----------|----------|------|------|------|------|------|

| 15,x | $_{0,y}$          | $^{1,y}$ | 2,y      | 3,у      | $^{4,y}$ | $^{5,y}$          | 6,y      | 7,y | 8,y      | 9,y      | 10,y | 11,y | 12,y | 13,y | 14,y |

| 15,y | $_{0,z}$          | $^{1,z}$ | $^{2,z}$ | $^{3,z}$ | $^{4,z}$ | $^{5,z}$          | $_{6,z}$ | 7,z | $^{8,z}$ | $_{9,z}$ | 10,z | 11,z | 12,z | 13,z | 14,z |

| 15,z | $^{0,w}$          | $^{1,w}$ | 2,w      | $^{3,w}$ | $^{4,w}$ | $^{5,w}$          | 6,w      | 7,w | $^{8,w}$ | 9,w      | 10,w | 11,w | 12,w | 13,w | 14,w |

| 15,w |                   |          |          |          |          |                   |          |     |          |          |      |      |      |      |      |

| 1 ) |                  |               |

|-----|------------------|---------------|

| h   | ) Struct-of-arra | vs misaligned |

| ~   | / Durace or arra | yo, moundiou  |

| $_{0,x}$ | $^{1,\mathrm{x}}$ | $^{2,\mathrm{x}}$ | 3,x      | 4,x      | $^{5,\mathrm{x}}$ | 6,x      | 7,x      | 8,x      | 9,x      | 10,x | 11,x | 12,x | 13,x | 14,x | 15,x |

|----------|-------------------|-------------------|----------|----------|-------------------|----------|----------|----------|----------|------|------|------|------|------|------|

| $_{0,y}$ | 1,y               | $^{2,y}$          | 3,у      | $^{4,y}$ | $^{5,y}$          | $_{6,y}$ | 7,y      | 8,y      | 9,y      | 10,y | 11,y | 12,y | 13,y | 14,y | 15,y |

| $_{0,z}$ | $^{1,z}$          | $^{2,z}$          | $^{3,z}$ | $^{4,z}$ | $^{5,z}$          | $_{6,z}$ | 7,z      | $^{8,z}$ | $_{9,z}$ | 10,z | 11,z | 12,z | 13,z | 14,z | 15,z |

| $_{0,w}$ | 1,w               | $^{2,w}$          | 3,w      | 4,w      | $^{5,w}$          | $_{6,w}$ | $^{7,w}$ | 8,w      | 9,w      | 10,w | 11,w | 12,w | 13,w | 14,w | 15,w |

c) Struct-of-arrays, aligned

Figure 2.2: Data lay-out examples for 4-element entries

As the red elements demonstrate, a request for the x-components of each work-item results in loading four bursts when the data is structured as an array-of-structs, while a well aligned struct-of-arrays buffer can provide the same data in a single burst.

Figure 2.2b demonstrates the importance of data alignment. Misaligned data necessitates the request of a second burst or cache line, resulting in more pressure on the memory system. If the nature of the data permits aligning the elements a warp requests to the boundaries of a burst, this pressure can be reduced. However, as the class of filter algorithms demonstrates, this is not always within control of the programmer.

Filter kernels read a  $n \times m$ -region of data for each work-item, performing a weighted multiply-addition on each element in this region to compute a final output. Regions read by adjacent work-items may overlap. Examples of such filter kernels include image anti-aliasing and the max-pooling operation for convolutional neural networks (CNNs).

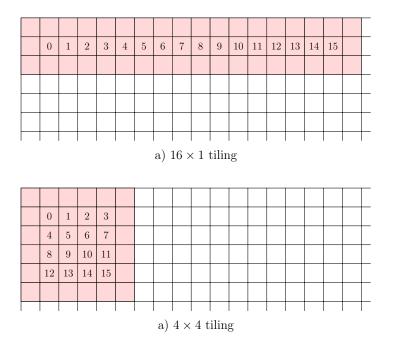

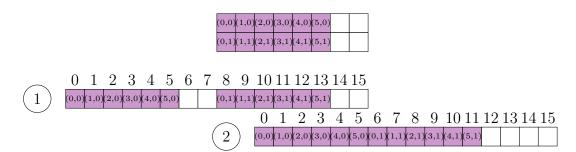

A common technique to maximise the number of words shared within a work-group is called *tiling*. To demonstrate this effect, consider a  $3 \times 3$  filter processed by a work-group containing 16 work-items. Figure 2.3 shows the tile of data accessed by one work-group for both a  $16 \times 1$ - and a  $4 \times 4$  tiling configuration. The centre of each work-item's  $3 \times 3$  data region is marked with its TID.

Figure 2.3: Data regions processed by one work-group for a  $3 \times 3$  filter operation, stride 1

As Figure 2.3 demonstrates, an efficient tiling strategy can reduce the number of elements requested by a work-group. Where for the  $16 \times 1$  configuration 18 \* 3 = 54 elements must be read from memory, the  $4 \times 4$  configuration reads only 6 \* 6 = 36 elements. It is not immediately clear which tiling strategy gives the best DRAM throughput, as alignment of data influences the number of bursts issued for the request of a given tile. Tile dimensions must thus be chosen on a per-case basis.

This technique assumes an effective mechanism to share data elements within a workgroup, such that tiles are only requested once from DRAM. GPUs support both transparent caching of tile data in associative caches, and explicit tile caching in local memory.

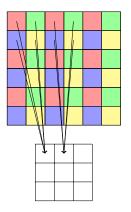

Even when data is not shared between work-items in a work-group, it could pay off to load data into local memory. Consider for example a  $2 \times 2$  filter operation with a pitch of 2. The arrows in Figure 2.4 show how elements from the input buffer map to the first two work-items. Each work-item requests its elements in the order *red, green, blue, yellow*.

Figure 2.4: Example  $2 \times 2$  filter operation with a pitch of 2.

Looking at the coalesced request for all red items, we can see that the pitch between two work-items causes every other (green) data element in a burst to be discarded even though these are required later. Performance of the application can be improved by pre-loading the work-group's entire block into local memory. This way the cost of issuing the second request for the green data words can be serviced by the lower-latency local storage, reducing the occupation of the shared DRAM bus.

#### 2.2.3 Edges in filter operations

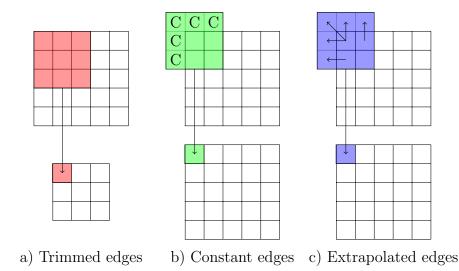

Tiling techniques for filter operations must consider the way an application handles the borders of a data set. Figure 2.5 demonstrates three edge-case strategies: trimmed edges, constant edges and extrapolated edges.

**Figure 2.5:** Variations of 3\*3 filter processing.

In all these cases, the most convenient TID mapping is a linear mapping of work-items to output elements. For the trimmed edges case this mapping ensures that no boundary cases exist for transferring tiles of data from DRAM to the compute cores' registers. The required tile of data for a work-group is simply of size xdim + 2, ydim + 2.

Requests that load a tile of data to local memory must compensate offsets and dimensions for constant- and extrapolated edges. If edges are simply ignored, transfers can end up reading beyond the bounds of the buffer. This poses a risk to program correctness and could violate process isolation principles.

### 2.3 Real-time systems

Real-time systems are a specific class of systems that can guarantee real time constraints, expressed as deadlines on work, that are imposed by the physical world. Consider for example the response time of car brakes: one deadline could express the maximum tolerable delay between the *event* of operating the brake pedal and the *response* of an engaged brake. An appropriate deadline is chosen by car manufacturers to ensure that the braking distance stays within safe limits.

To reason about a system's ability to meet such deadlines, a large body of research analyses the problem of *schedulability*. Using the abstraction of a task model [32–34], algorithms can decide for a given set of tasks and a given scheduling policy (e.g. fixedpriority (FP) [35], earliest-deadline first (EDF) [35, 36]) whether all deadlines are met. In these task models, a task is described by a *deadline*, a *WCET* (*cost*), the (minimum) interval between two events of the same task (*period*), and for some scheduling policies the *priority* of a task relative to others. To determine whether a task is guaranteed to meet it's deadline, its *worst-case response time* (*WCRT*) must be calculated. The WCRT is the maximum time it takes for a job to complete from the moment of launch, taking into account the worst-case blocking that can be caused by other active tasks. The WCRT is computed either explicitly or implicitly as part of a schedulability test for a given task set.

This dissertation contributes a wide-SIMD architecture and algorithm that together permit the derivation of a safe WCET for a given kernel-instance. In the context of scheduling, the WCET of either a single kernel-instance or a sequence of kernel-instances may form the cost of a task. Policies for scheduling tasks or kernels on Sim-D and schedulability tests to assess whether tasks meet their deadlines are considered beyond the scope of this work. Section 8.1 discusses various avenues for future work on task scheduling with Sim-D.

In the remainder of this section I discuss related work on two topics from the field of real-time systems relevant to this thesis: real-time DRAM controllers and WCET computation algorithms.

#### 2.3.1 Hard real-time DRAM controllers

DRAM controllers can be divided in two groups: closed-page and open-page. Closed-page DRAM controllers ensure that every request starts and finishes with all banks precharged. Open-page DRAM controllers leave rows open after servicing a request, anticipating that more columns from that row will be requested later. The latter strategy is mostly employed in throughput-oriented systems, as the overhead for precharging and activating rows are substantial.

From a real-time perspective, a closed-page policy has the favourable property of performance isolation: a requests' execution time does not vary based on those that precede it. This paves the way for worst-case execution analysis of individual request. At the same time, within each request it is possible to exploit bank locality and make use of parallel execution of activate and read/write commands to different banks. In other words: the deterministic closed-page property exists on the *boundaries* of each request, while *within* a request open-page performance optimisation techniques can be employed.

To evaluate the performance of DRAM controllers, I use two definitions defined by Paolieri et al [37], to describe the (worst-case) timing behaviour of DRAM requests: worst-case request execution time and longest issue delay.

The worst-case request execution time (WCRET) marks the maximum delay, excluding the time waiting for requests to wait for other requests to finish, before a work-group can continue execution. For read operations, the WCRET spans the interval between issuing the first bank activate command of a request and the arrival of the last data word. For write operations, this interval spans from the first bank activate command to the instance the last written data word is transferred on the DRAM data bus, either originating from Sim-D's register file or scratchpad.

The issue delay for a request is defined as the time required between starting the current request and starting the next. For a closed-page DRAM controller, this spans the interval from the first activate command to the first time instant at which all banks are precharged. Bar the refresh interval counter(s), the state of the DRAM controller is indistinguishable before a request and after passing the issue delay, a key property for allowing the analysis of requests in isolation from others. Longest issue delay (LID) is defined as the upper bound on a request's issue delay.

#### 2.3.1.1 Closed page: Memory pattern-based HRT DRAM controllers

A large body of research has focussed on *memory pattern*-based DRAM controllers [38–42]. In this context, a memory pattern is a predetermined schedule of DRAM commands that services a read or write request of fixed size to an arbitrary (but aligned) address. A request may span more than one burst of data, and may address more than a single row. Patterns have fixed timing properties and implement a closed-page policy at the boundaries, striking a balance between the analysability of statically scheduled DRAM controllers on one hand, and performance and flexibility of a dynamically scheduled DRAM controller on the other.

In the literature, the assumption is made that a request always reads or writes as many words as are serviced by one execution of a DRAM pattern. In the light of CPUs, issuing aligned cache-line sized requests, this assumption is valid, but in the context of our Sim-D architecture this assumption does not acknowledge the fact that coalesced requests can be of arbitrary size. Hence in this work I define a *request* to be of arbitrary size. An execution of the commands in a DRAM pattern will be referred to as a *pattern transaction*. A request could therefore require multiple pattern transactions to be performed by a pattern-based DRAM controller.

Akesson et al. [38] describe the basic architecture of a pattern-based DRAM controller

and show how its design leads to both performance-predictability and -composability. These properties imply that the performance of individual consumers can be analysed independently from one another, following the Latency-Rate model [43].

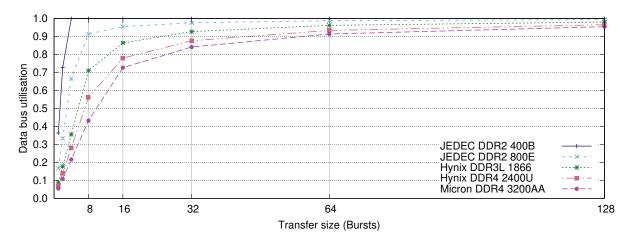

The first pattern-based DRAM controller was Akesson et al.'s "Predator" [40]. This DDR2 memory controller guarantees bandwidth and latency of requesters by pre-computing the latency for the execution of each cache-line sized DRAM patterns (Akesson: "memory groups"). The memory configuration is carefully chosen such that each pattern transaction hits all banks, helping to reduce the distance between two requests. By the time request  $R_n$ processes the data transfer of its last bank m + 3, the first bank will already be precharged. Request  $R_{n+1}$  is now ready to send its first request to bank m despite bank m+3 not being precharged yet. By using a novel arbitration policy called "credit-controlled static priority" (CCSP) [44], Predator is capable of providing both minimum bandwidth guarantees as well as a bound latency on individual requests.

Paolieri et al. [45] propose a similar solution called "AMC". Rather than providing latency-rate guarantees with a CCSP-based arbiter, AMC utilises a simpler round-robin policy. AMC provisions for mixed-criticality workloads by always prioritising HRT requests over non-real-time requests. This leads to a simple static latency analysis where every request is assumed to be delayed by at most the number of other HRT tasks in the system (plus one non-HRT task) multiplied by the maximum latency of any cache-line sized request. Like Predator, AMC makes each request iterate over all banks in the DRAM chip for efficient operation. In [37], they discuss an extension where non-HRT requests can be preempted between two bank-requests, thus breaking with the concept of issuing fixed DRAM patterns. Assuming their timing analysis model, wherein every request is treated independent rather than analysed as part of a global "sequential history", this preemption support reduces the analysed worst-case latency for HRT requests.

Goossens et al. [41] identify how reconfigurability could bring additional guaranteed bandwidth to pattern-based HRT memory controllers. They extend Akesson et al.'s model [38] in two ways. First they adjust the DRAM patterns such that read and write operations always take the same time, regardless of the interleaving of the two. The memory controller services clients following a TDM schedule, providing composable performance to the clients. Secondly, they add a mechanism for reconfiguring both the client TDM slot allocations and the memory patterns. In HRT systems following e.g. partitioned sporadic task scheduling, they can alter the client bandwidth based on the active tasks, thus cater for a wider range of task-sets.

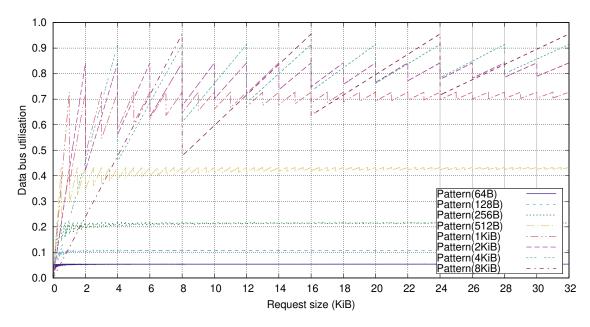

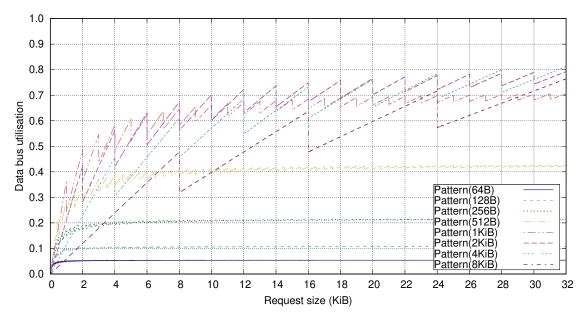

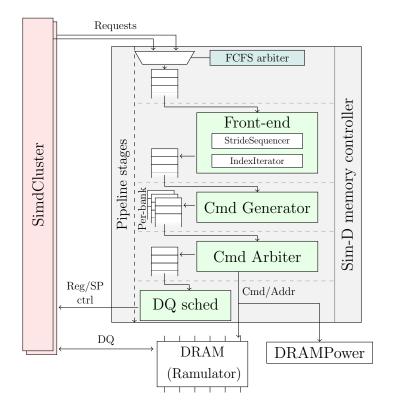

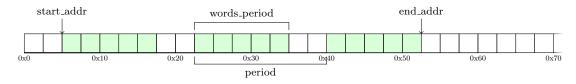

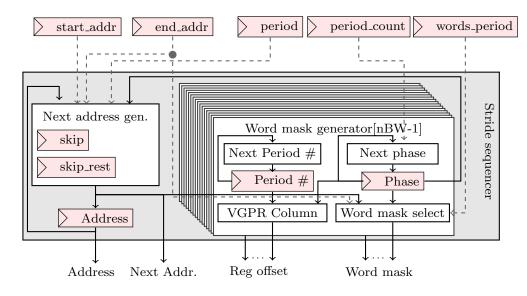

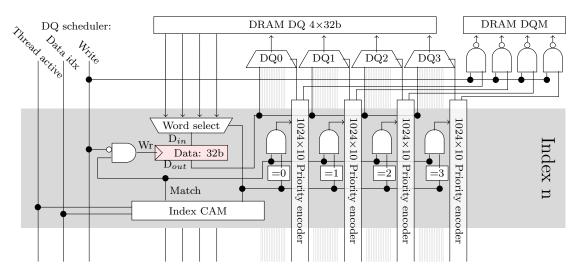

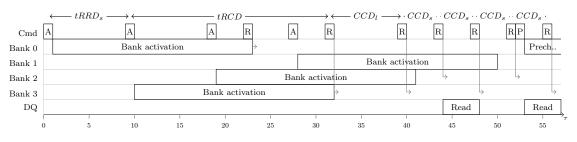

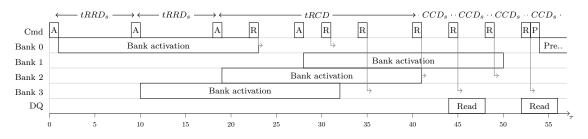

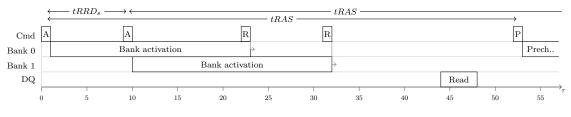

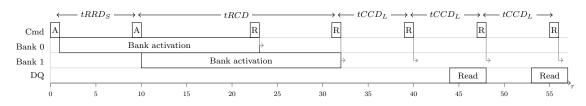

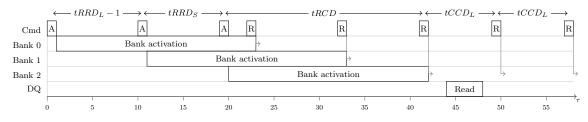

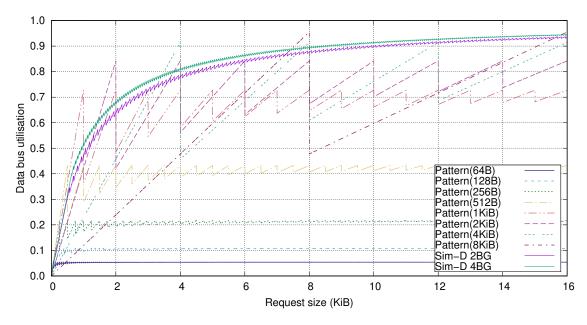

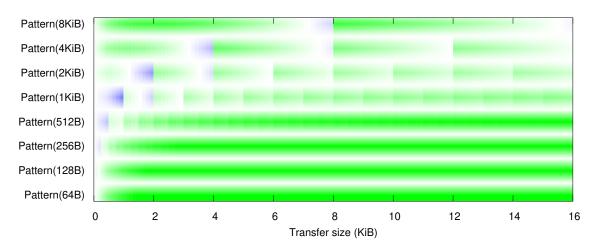

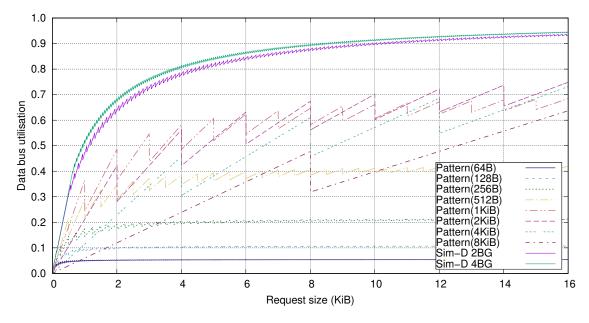

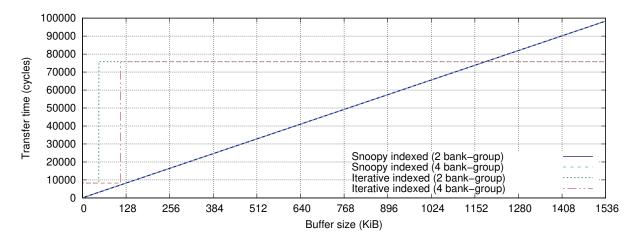

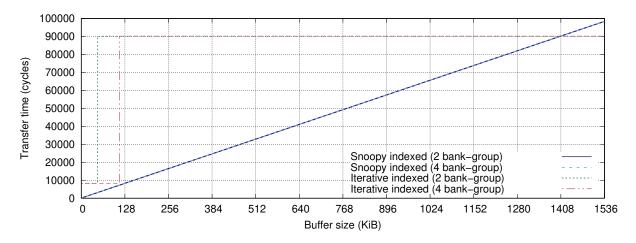

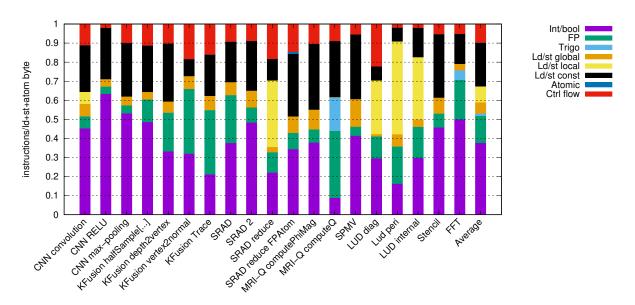

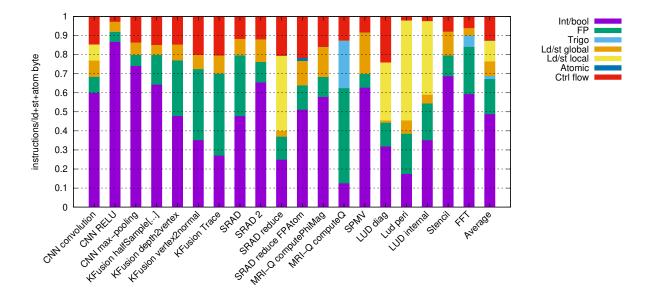

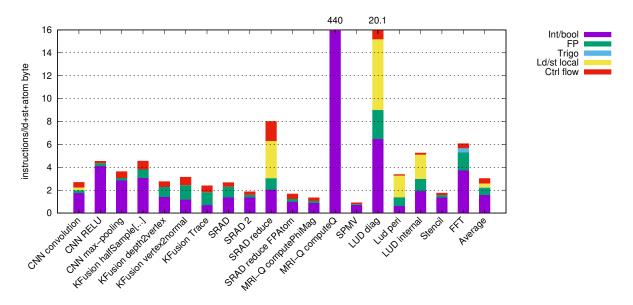

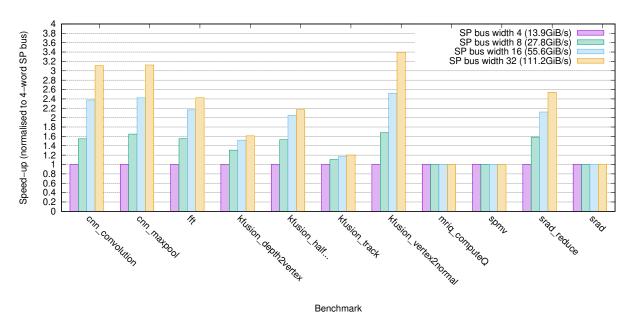

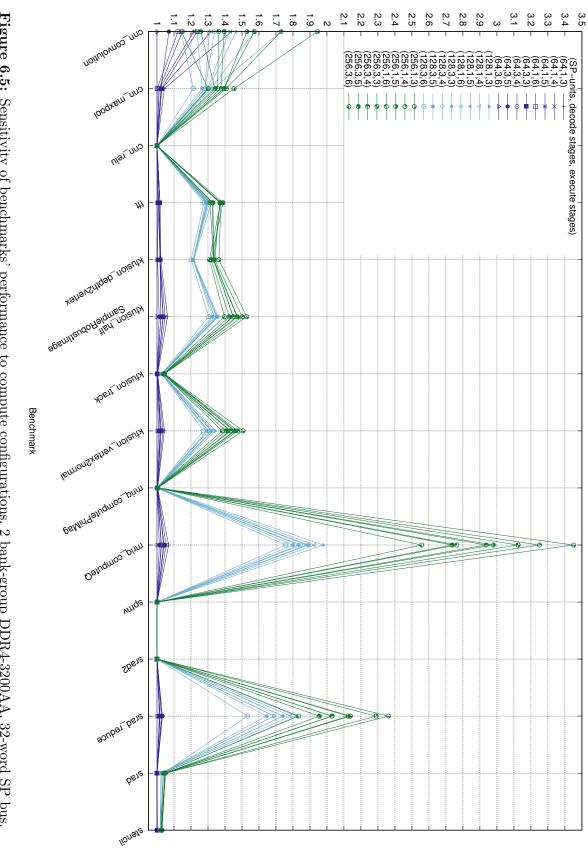

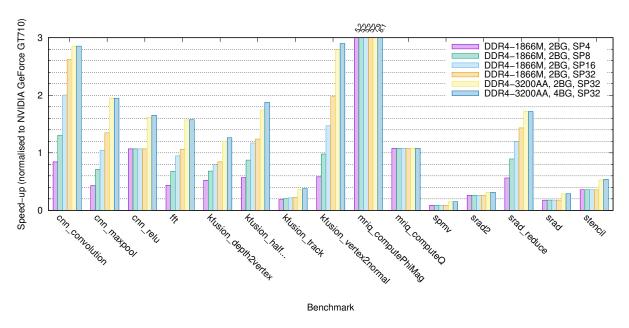

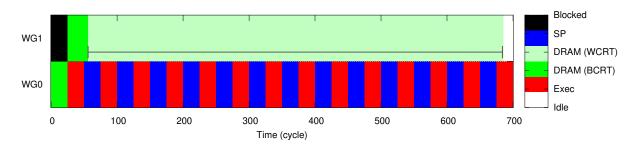

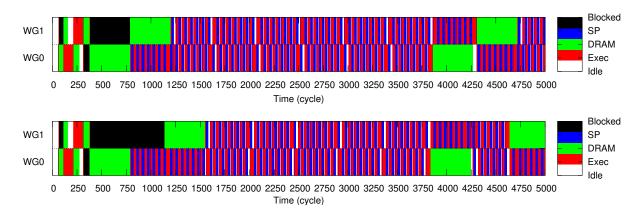

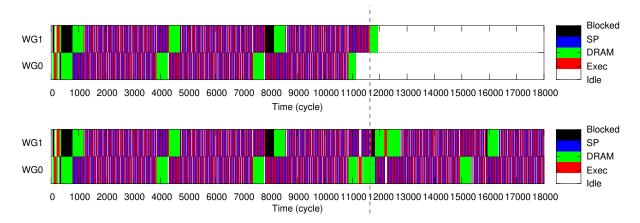

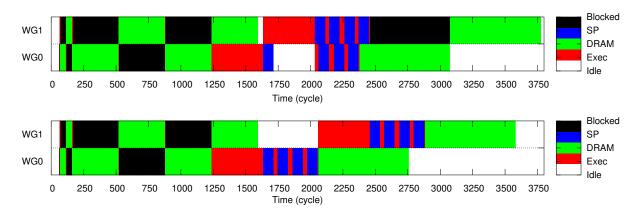

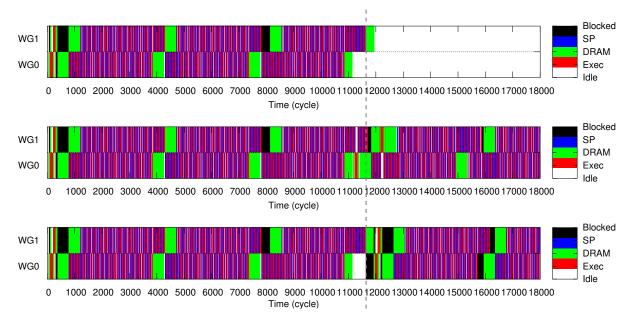

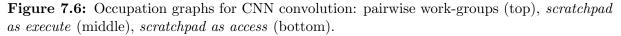

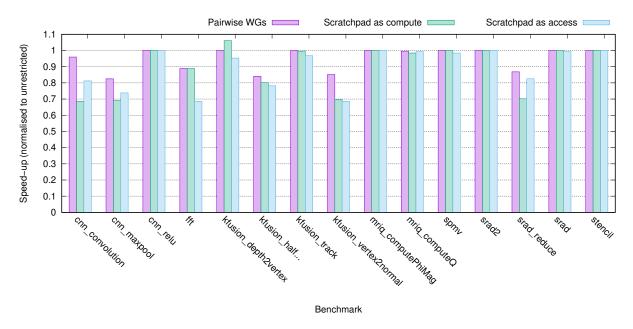

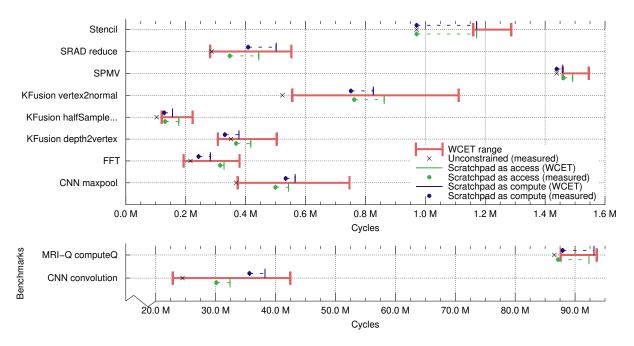

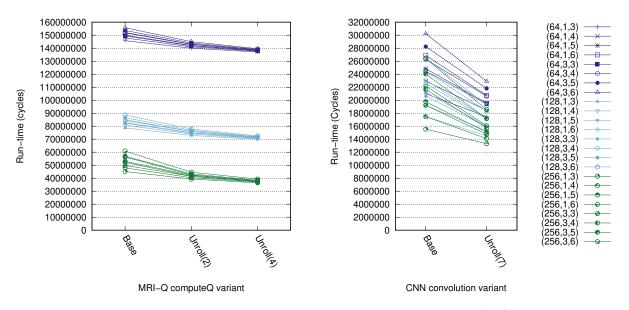

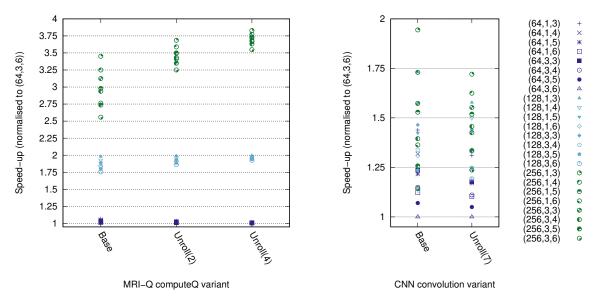

Li et al. [42] identify an increasing need for a variable DRAM request size. They observe that allowing arbitrary sized requests leads to timing anomalies caused by the history of transactions executed. They propose a round-robin scheduling policy of requests of variable size using a closed-page DRAM policy. For individual transactions, they propose a method to derive a tight bound on worst-case execution time. In subsequent work, they propose WCET analysis methods for DRAM requests based on data-flow programming [46] and timed automata [47], both resulting in tighter bounds.