# Turn-Off Voltage Sharing of Field-Stop IGBTs in Series Connection under Inductive Load Conditions

Xueqiang Zhang

Robinson College

University of Cambridge

January 2016

This thesis is submitted for the degree of Doctor of Philosophy

#### **Declaration**

This thesis is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or, is being concurrently submitted for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my thesis has already been submitted, or, is being concurrently submitted for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. It does not exceed the prescribed word limit for the relevant Degree Committee.

# Turn-Off Voltage Sharing of Field-Stop IGBTs in Series Connection under Inductive Load Conditions

#### Xueqiang Zhang

**Abstract** – Operating Silicon (Si) Insulated Gate Bipolar Transistors (IGBTs) in series connection is attractive to many power electronic applications, including converters, hybrid circuit breakers, etc. To operate IGBTs in series connection, regulating the voltage sharing between the IGBTs during the IGBT turn-off is essential.

The objective of this thesis is to explore practical and efficient methods at IGBT device level for regulating the voltage sharing of IGBTs in series connection during the IGBT turn-off under inductive load condition. The discussions in this thesis are regarding modern Field-Stop (FS) Si IGBTs which are widely adopted. The key mechanisms at IGBT device level are discussed regarding the turn-off voltage sharing of series-connected IGBTs under typical inductive load conditions. A Finite Element Method IGBT model of a 1700 V FS Si IGBT is developed, and simulations of two-in-series IGBT turn-off using this IGBT model in an inductive current commutation loop are conducted to study the effects of a few selective IGBT internal parameter variations and control errors on the turn-off voltage sharing.

Following these studies, three types of approaches from different perspectives are attempted to mitigate the turn-off voltage divergence of series-connected IGBTs. For a passive approach, a few selective adjustments to IGBT internal parameters are reviewed in simulation regarding their effects on the turn-off voltage divergence. Some of these parameter adjustments are useful for improving the basis of the turn-off voltage sharing, and appropriate application of them in combination is attractive.

Active voltage sharing regulation is essential for achieving closely matched turn-off voltage sharing of series-connected IGBTs. Regarding the direct control of IGBT gate for the voltage sharing regulation, a redesigned direct regulation method based on an Active Voltage Control (AVC) scheme is presented. This direct regulation method is based on differential regulation designed to regulate the voltage sharing as it tends to diverge. The design concept and the mechanism of this direct method is discussed, and the experimental demonstration is shown. Compared with previous relevant researches, the direct regulation method here avoids significant additional losses caused by the voltage sharing regulation process.

In addition, an external regulation method using auxiliary Silicon Carbide (SiC) Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) controlled by the AVC scheme is presented. This external regulation method is also based on differential regulation designed to regulate the voltage sharing as it tends to diverge. The design concept and the mechanism of this external method is discussed, and the experimental demonstration is shown. The response of the voltage sharing regulation is improved with the auxiliary SiC MOSFETs. Both the direct and the external regulation methods here are effective in the experiments.

The conclusions are drawn regarding the work presented in this thesis on the turn-off voltage sharing of series-connected IGBTs and its improvement and regulation. The limits in the experimental implementations here of the two voltage sharing regulation methods are discussed. Future work is suggested regarding modelling and advanced optimisation in simulation and advancing the voltage sharing regulation methods.

To my family.

## Acknowledgements

Firstly, I would like to express my gratitude to my supervisor, Prof Patrick Palmer, for his unfailing support throughout my PhD studies. His enthusiasm, encouragement, advice, and feedback have been invaluable.

I would also like to thank Zhihan Wang, Weiwei He, Fei Kong, Pritesh Hiralal, Yuhao Sun, Jin Zhang, Xin Yang, Teng Long, John Grundy, and the rest of the Oatley Lab for their helpful assistance with my work.

I would like to thank Qiang Liu, Yonghao Sun, Weiji Ma, and all my friends, both in Cambridge and elsewhere, for their kind support during my PhD studies.

And special thanks to my wife Jingchen Hou.

Finally, everything I achieved would not have been possible without the unfailing love, encouragement, and support of my parents. They gave me great power to always stay positive against various challenges.

# **Table of Contents**

| Chapter 1  | I Introduction                                                                                  | 1    |

|------------|-------------------------------------------------------------------------------------------------|------|

| 1.1        | An Introduction to Power Semiconductor Devices                                                  | 1    |

| 1.1.1      | An Introduction to Operations of IGBTs                                                          | 3    |

| 1.1.2      | General Limits in Commercial Si IGBTs                                                           | 4    |

| 1.2        | An Introduction to the Relevant Basics of Si IGBT Physics                                       | 5    |

| 1.2.1      | Intrinsic Carrier Concentration                                                                 |      |

| 1.2.2      | Impact Ionisation Coefficients                                                                  | 6    |

| 1.2.3      | Carrier Mobility                                                                                | 6    |

| 1.2.4      | Carrier Recombination and Recombination Lifetime                                                | 7    |

| 1.2.5      | Basic Equations for Si Power Devices.                                                           | 9    |

| 1.3        | Introduction to IGBT Structural Components                                                      | 10   |

| 1.3.1      | PN Junction and Depletion Region                                                                | 11   |

| 1.3.2      | Power BJT                                                                                       | 12   |

| 1.3.3      | Power MOSFET                                                                                    | 14   |

| 1.4        | An Introduction to Relevant IGBT Basics                                                         | 17   |

| 1.4.1      | High Voltage IGBT Structures                                                                    | 17   |

| 1.4.2      | Basic IGBT Operations                                                                           | 19   |

| 1.4.3      | High-level Injection and Ambipolar Carrier Transport                                            | 21   |

| 1.5        | Internal Mechanisms of FS IGBTs in Typical Inductive Turn-off                                   | 23   |

| 1.5.1      | 1D Approximations for the IGBT N Base                                                           |      |

| 1.5.2      | The IGBT Initial State Prior to Turn-off                                                        | 24   |

| 1.5.3      | Low IGBT Gate Resistance and Fast IGBT Turn-off                                                 | 24   |

| 1.5.4      | Initial Behaviour of the MOS Channel Region                                                     | 25   |

| 1.5.5      | Ambipolar Carrier Transport in the CSR in the Fast $V_{CE}$ - $I_C$ Transient                   |      |

| 1.5.6      | Carrier Recombination in the CSR in the Fast $V_{CE}$ - $I_C$ Transient                         | 27   |

| 1.5.7      | Carrier Transport at the MOS Gate Side CSR Boundary in the Fast $V_{CE}$ - $I_C$ Transient      | 27   |

| 1.5.8      | Hole Current and Electric Field in the Depletion Region in the Fast $V_{CE}$ - $I_C$ Transient. |      |

| 1.5.9      | Current Commutation in Inductive Turn-Off with Stray Inductance                                 |      |

| 1.5.10     | Carrier Transport and Recombination in the Tail Time                                            | 30   |

| Chapter 2  | 2 Application and Research Motivation for Operating IGBTs in Se                                 | ries |

| Connection | on                                                                                              | 31   |

| 2.1        | Applications of IGBTs in Series Connection                                                      | 31   |

| 2.1.1      | VSC using IGBTs in Series Connection                                                            |      |

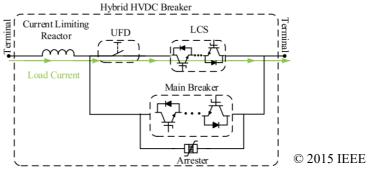

| 2.1.2      | Hybrid Circuit Breaker for MMCs                                                                 |      |

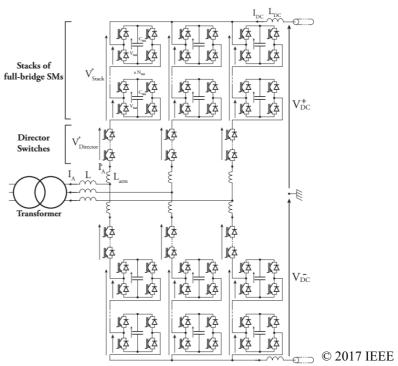

| 2.1.3      | Director Switch in Alternate Arm Converters                                                     |      |

| 2.1.4      | Cascaded Two-Level Converter                                                                    | 34   |

| 2.2        | Review of Methods for Improving the $V_{CE}$ Sharing                                            | 36   |

| 2.2.1      | Load Side Control Methods                                                                       |      |

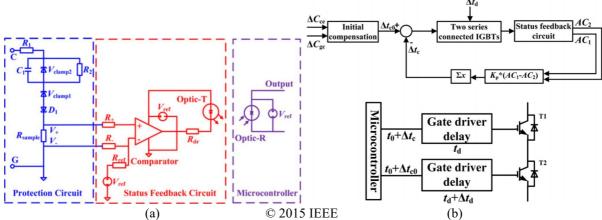

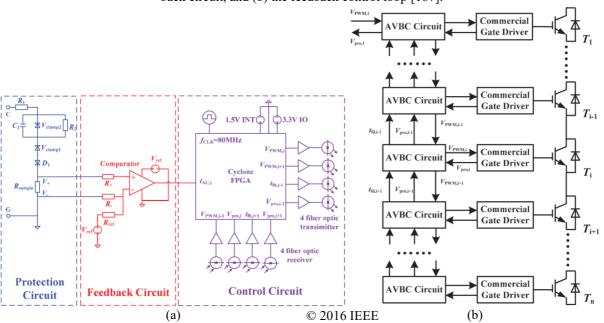

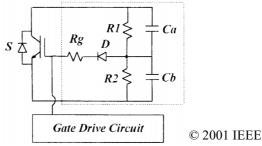

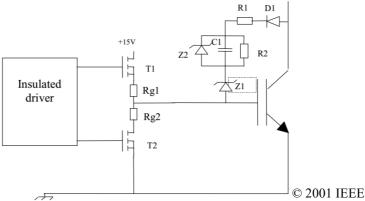

| 2.2.2      | Active Gate Control Methods                                                                     |      |

| 2.3        | Research Motivations                                                                            | 52   |

| 2.3.1      | Negative Effects of Uncontrolled $V_{CE}$ Divergence                                            |      |

| 2.3.2      | Approaches at IGBT Device Level for Improving $V_{CE}$ Sharing                                  |      |

|            |                                                                                                 |      |

| Chapter | 3 Internal Mechanisms and Simulations of the Turn-off $V_{CE}$ Diverge   | nce55     |

|---------|--------------------------------------------------------------------------|-----------|

| 3.1     | Practical Conditions for the Turn-off $V_{CE}$ Sharing                   | 55        |

| 3.2     | Experiment Examples of the Turn-off $V_{CE}$ Divergence                  | 55        |

| 3.3     | Basic Diverging Mechanisms of the Turn-Off $V_{CE}$ Sharing              |           |

| 3.3.1   |                                                                          |           |

| 3.3.2   |                                                                          |           |

| 3.3.3   | Basic Scenarios of the Turn-off $V_{CE}$ Divergence in the Tail Time     | 59        |

| 3.3.4   | Combinations of the Basic $V_{CE}$ diverging Scenarios                   | 61        |

| 3.3.5   | The Influence of the Anti-Parallel FWDs on the Turn-Off $V_{CE}$ Sharing | 64        |

| 3.3.6   | Long-Term Stability of the $V_{CE}$ Sharing in the IGBT Off-State        | 67        |

| 3.3.7   | Temperature Differences Arising from the Turn-Off Voltage Divergence     | 68        |

| 3.4     | FEM Simulation Setup for the Turn-Off $V_{CE}$ Divergence                | 69        |

| 3.4.1   | Estimation of IGBT Active Chip Area                                      | 69        |

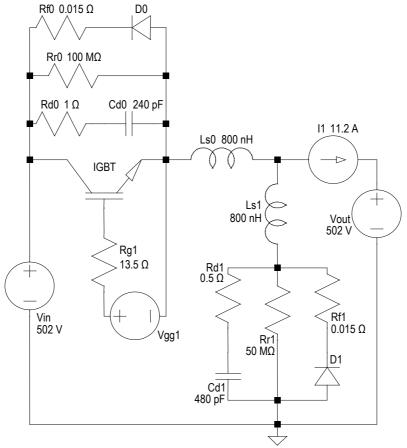

| 3.4.2   | 2 Simulation Circuit Parameters and Scaling                              | 70        |

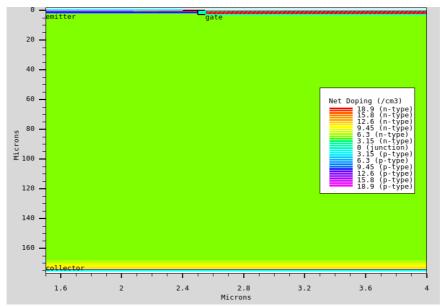

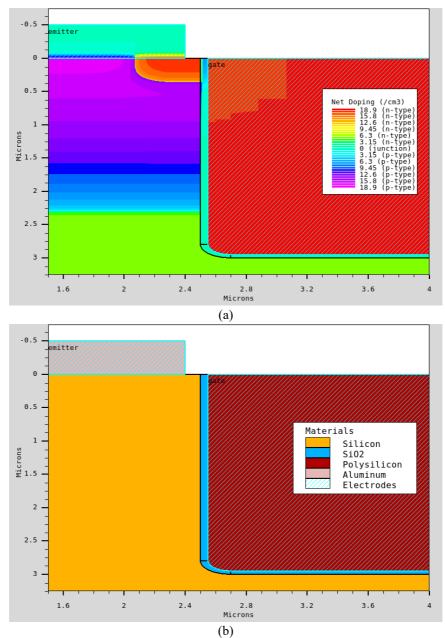

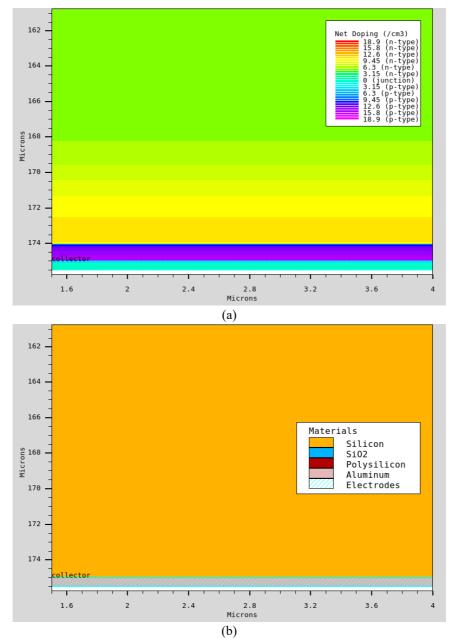

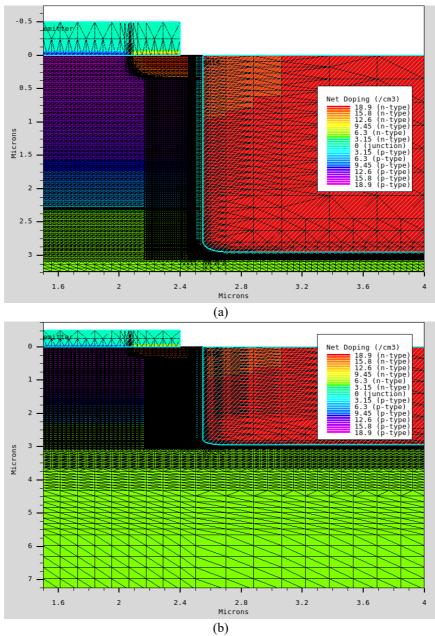

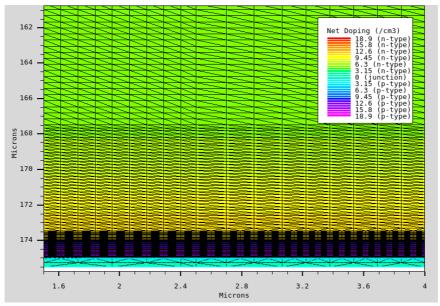

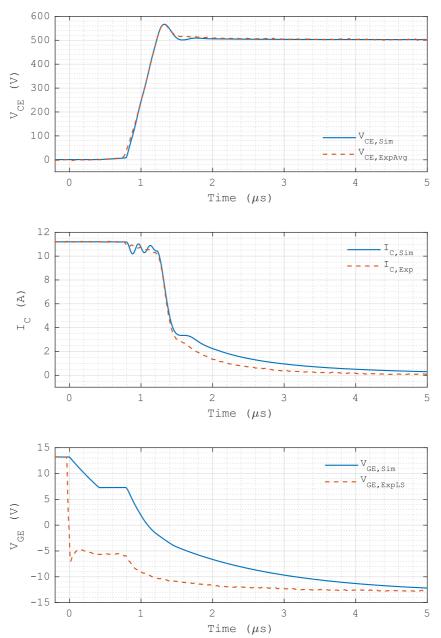

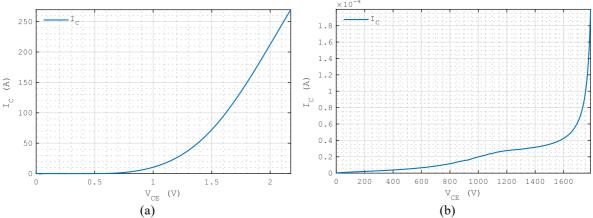

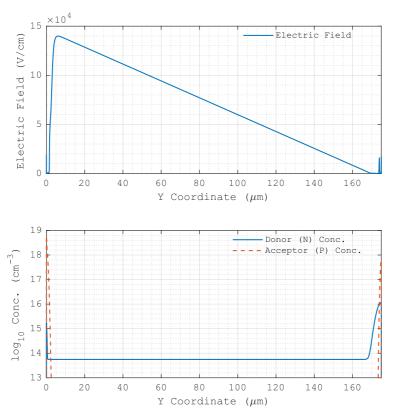

| 3.4.3   | FS IGBT Model in the Simulations                                         | 71        |

| 3.4.4   | Selection of the Physics Model in Silvaco ATLAS                          | 76        |

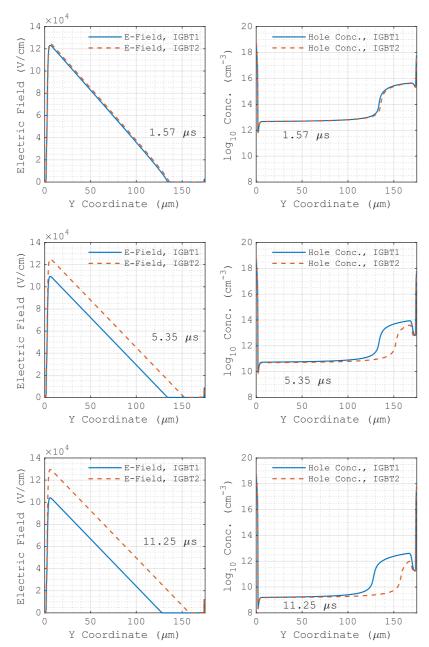

| 3.4.5   | 5 Simulation Examples                                                    | 78        |

| 3.5     | Simulations of Individual $V_{CE}$ Diverging Factors                     | 82        |

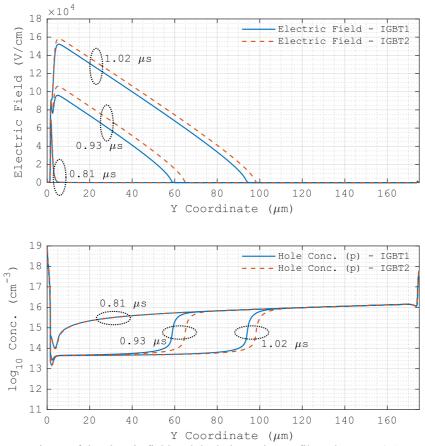

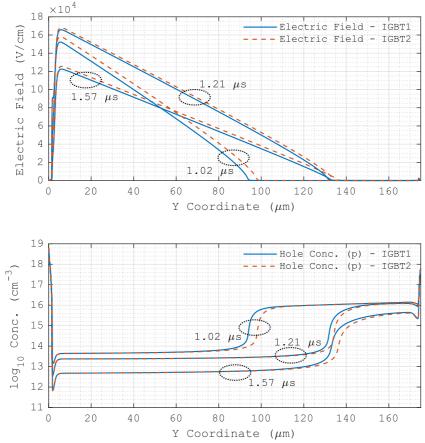

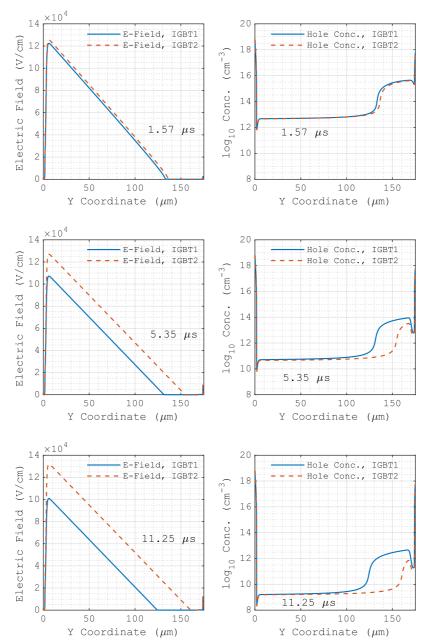

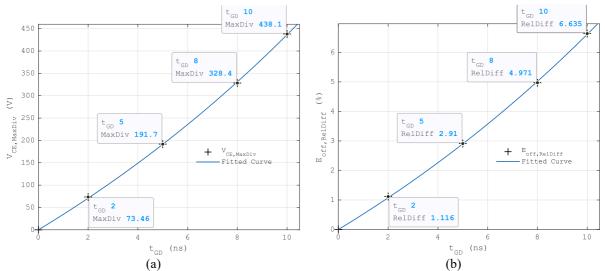

| 3.5.1   | An Output Delay in the IGBT <sub>1</sub> Gate Drive                      | 83        |

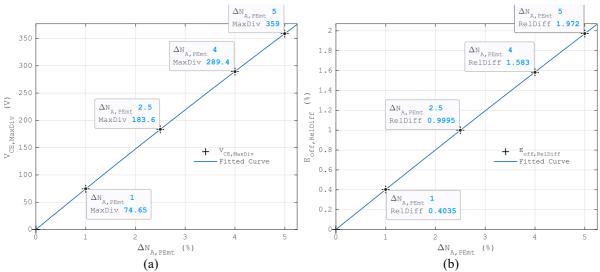

| 3.5.2   | 2 IGBT <sub>1</sub> with a Higher P Emitter Doping Profile               | 87        |

| 3.5.3   | B IGBT <sub>1</sub> with a Higher Gate Resistance                        | 92        |

| 3.5.4   | IGBT <sub>1</sub> with a Higher Gate Oxide Thickness                     | 94        |

| 3.5.5   | IGBT <sub>1</sub> with a Higher N buffer Doping Profile                  | 96        |

| 3.5.6   |                                                                          |           |

| 3.5.7   |                                                                          |           |

| 3.5.8   | Summary of the $V_{CE}$ Divergence Results and Sensitivity Analysis      | 101       |

| Chapter | 4 Passive Mitigation Methods at IGBT Device Level under Direct           | ct Series |

| Connect | ion                                                                      | 107       |

| 4.1     | $V_{CE}$ Diverging Features and Passive Mitigation Methods               | 107       |

| 4.2     | Simulation Test of the Passive Mitigation Methods                        |           |

| 4.2.1   | •                                                                        |           |

| 4.2.2   | •                                                                        |           |

| 4.2.3   |                                                                          |           |

| 4.2.4   |                                                                          |           |

| 4.2.5   |                                                                          |           |

| 4.2.6   |                                                                          |           |

| 4.3     | The Use of the Passive Mitigation Methods in Combination                 | 123       |

| Chapter | 5 Direct Active Voltage Control for Regulating the Voltage Sharing.      | 127       |

| 5.1     | Direct Active IGBT Gate Control for Regulating the $V_{CE}$ Sharing      |           |

| 5.1.1   |                                                                          |           |

| 5.1.2   |                                                                          |           |

| 5.2     | Design and Implementation of Direct Active $V_{CE}$ Sharing Regulation   |           |

| 5.2.1   |                                                                          |           |

| ا.۷.۷   | Design Concept of the Ducet Active & CE Sharing Regulation               | 129       |

| 5.2.2   | Mechanism of the Differential $V_{CE}$ Sharing Regulation                                  | 130   |

|---------|--------------------------------------------------------------------------------------------|-------|

| 5.2.3   | Implementation of the AVC Gate Drive Circuit                                               | 131   |

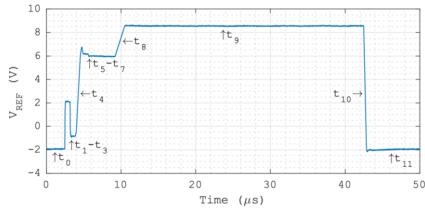

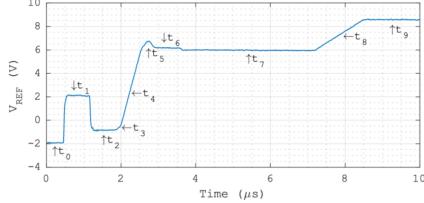

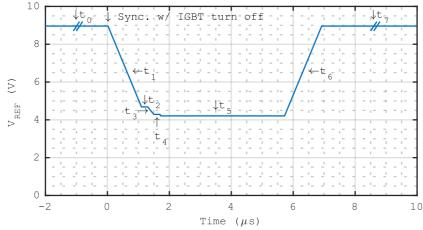

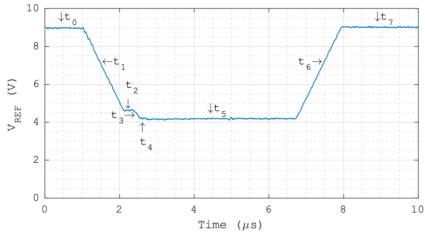

| 5.2.4   | Implementation of the $V_{CE}$ Reference Signal                                            | 132   |

| 5.3     | Experiments of the Direct Active $V_{CE}$ Sharing Regulation                               | 135   |

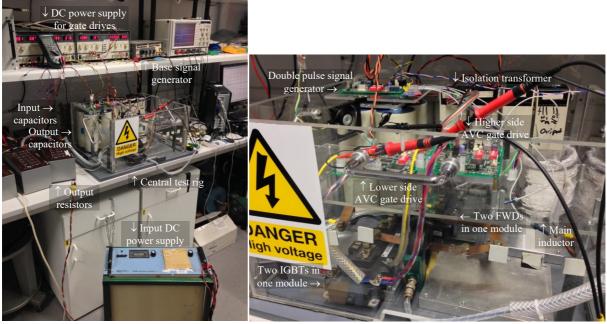

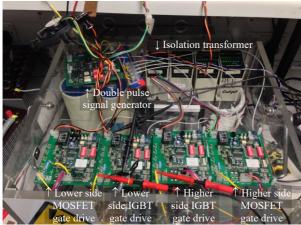

| 5.3.1   | Experiment Setup                                                                           | 135   |

| 5.3.2   | 62 &                                                                                       |       |

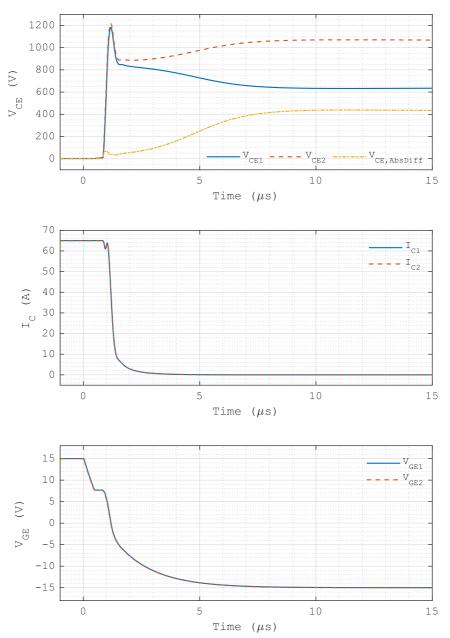

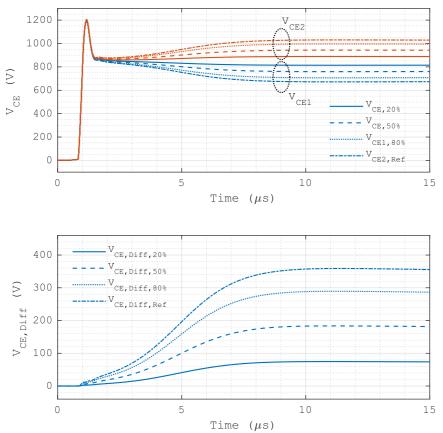

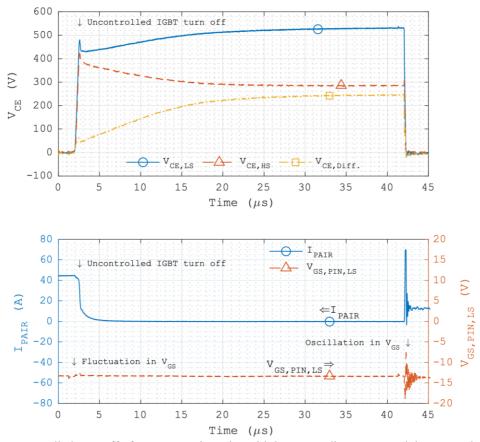

| 5.3.3   | $V_{CE}$ Divergence in Uncontrolled IGBT Turn-Off                                          | 137   |

| 5.3.4   |                                                                                            |       |

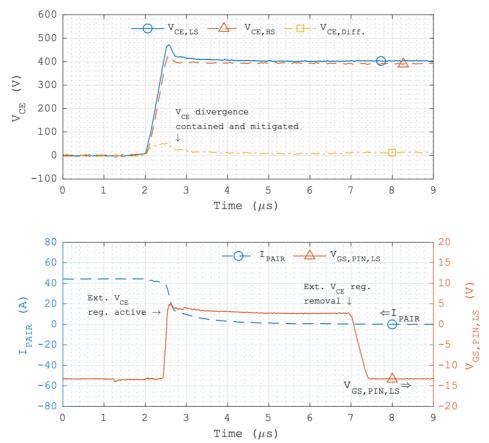

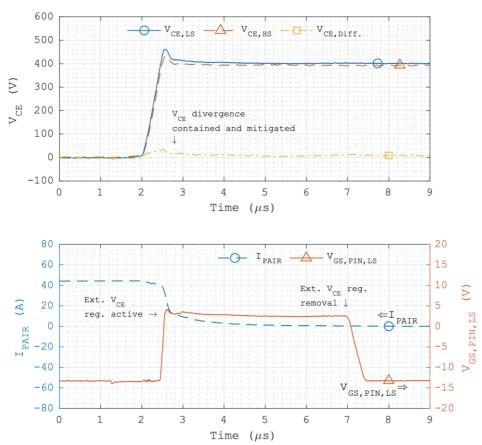

| 5.3.5   | Demonstration of the Direct Active $V_{CE}$ Sharing Regulation in the Tail Time            |       |

| 5.3.6   |                                                                                            |       |

| 5.4     | Summary of the Direct Active $V_{CE}$ Sharing Regulation                                   | 150   |

| Chapter | 6 External Active Voltage Control for Regulating the Voltage Sharing                       | ; 151 |

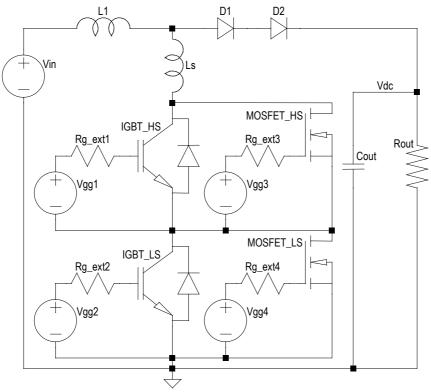

| 6.1     | External Active $V_{CE}$ Sharing Regulation with SiC MOSFETs                               | 151   |

| 6.1.1   | Design Concept of the External Active $V_{CE}$ Sharing Regulation                          | 151   |

| 6.1.2   | Mechanism of the External Active $V_{CE}$ Sharing Regulation                               | 153   |

| 6.1.3   | Implementation of the AVC Circuit and the $V_{CE}$ Reference Signal                        | 154   |

| 6.2     | Experiments of the External Active $V_{CE}$ Sharing Regulation                             | 156   |

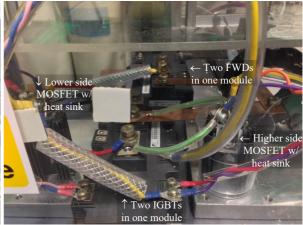

| 6.2.1   | Experiment Setup                                                                           | 156   |

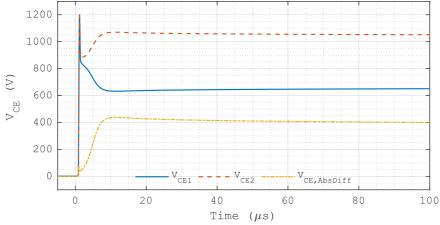

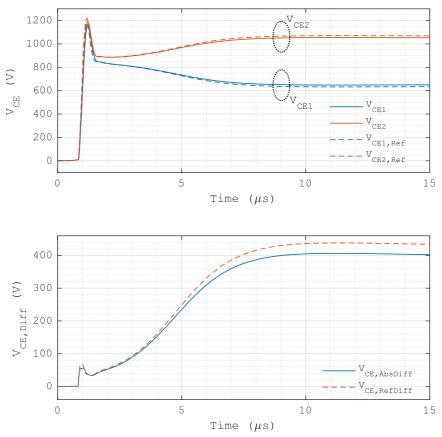

| 6.2.2   | $V_{CE}$ Divergence in Uncontrolled IGBT Turn-off                                          | 158   |

| 6.2.3   | Demonstration of the External Active $V_{CE}$ Sharing Regulation                           | 159   |

| 6.2.4   | Long-Term Off-State $V_{CE}$ Sharing after the External Active $V_{CE}$ Sharing Regulation | on162 |

| 6.2.5   | Thermal Utilisation of the Auxiliary SiC MOSFET                                            | 164   |

| 6.3     | Summary of the External Active $V_{CE}$ Sharing Regulation                                 | 166   |

| Chapter | 7 Conclusions and Suggestions for Future Work                                              | 169   |

| 7.1     | Conclusions                                                                                | 169   |

| 7.2     | Suggestions for Future Work                                                                | 171   |

| 7.2.1   | Modelling and Advanced Optimisation in Simulation                                          | 171   |

| 7.2.2   | Advancing the Active $V_{CE}$ Sharing Regulation Methods                                   | 171   |

### **Chapter 1** Introduction

Electricity as a form of energy is essential for today's technology evolution. Electric energy is widely adopted as a practical energy medium in the conversion of different energy forms. The processing of electric power is evolving constantly. The development of power electronic technologies enables the use of switch-mode power processing on high power applications. Switch-mode power processing provides higher conversion efficiency and enhanced control flexibility and precision for high power applications at lower costs, weights, and dimensions. Advanced power electronic technologies are widely adopted in energy conversion systems of a wide power range from milliwatts to megawatts. In switch-mode power processing, power flows are directed by active switches to achieve required power delivery between power sources, energy storage components, and loads.

In actual switching mode circuits, the active switches are implemented by solid-state power semiconductor devices with actively controllable switching capabilities to control the power flows. These power semiconductor devices are normally in either the on-state or the off-state during most of a switching cycle. The characteristics of these power devices in the on-state and the off-state have strong influences on the power processing capabilities. The switching behaviours of these power devices between the on-state and the off-state are a determining aspect in the reliability, the stability, and the performance of a power electronic system. Depending on the requirements, a power electronic system may use power semiconductor devices in various combinations, e.g. IGBTs in series connection switched simultaneously.

#### 1.1 An Introduction to Power Semiconductor Devices

In recent decades, a variety of power semiconductor devices have been developed. From Bipolar Junction Transistors (BJTs) in the late 1940s [1], [2] to Wide BandGap (WBG) power semiconductor devices [3], [4], the power ratings and the optimal switching frequencies of power semiconductor devices are improving constantly. Limited by the properties and the processing technologies of semiconductors over the years only a few types of practical power semiconductor devices have been widely adopted in power electronics.

Modern active power semiconductor devices originate from the Bipolar Junction Transistor (BJT) first introduced by J. Bardeen and W.H. Brattain in 1948 [1]. Later in 1952 the first power semiconductor rectifiers and transistors were reported by R.N. Hall [2]. Today there are two major types of commercial power semiconductor devices on the basis of active turn-off capability. The original thyristors, also known as Silicon-Controlled Rectifiers (SCRs) represent the type of switching devices without active turn-off capability. Introduced in 1956 by J.L. Moll [5], thyristors have dominated the power device market until late 1980s. They are widely adopted in high power applications of up to megawatts. To turn off the original symmetric thyristors, the thyristor current needs to be reduced below a holding current, normally by applying a reverse-biased anode-cathode voltage. Power diodes as passive devices also belong to this category. They are as important as other switching devices in power electronic systems, and modern power diode structures are highly optimised.

In power electronic systems that require both device turn-on and turn-off to be actively controllable, sometimes referred to as fully controllable, power BJTs and Gate Turn-Off (GTO) thyristors and their variants have been used since the 1980s in high power range. The first power BJT with substantial power processing capability was achieved in the 1960s [6]. Also invented in the same decade is the GTO thyristor [7]. Compared with power BJTs, GTO thyristors can easily achieve high conducting current densities with high blocking voltages. A GTO thyristor only requires a pulse of gate driving current for turn-on or turn-off, whereas a power BJT requires a continuous gate driving current in its on-state. Consequently, Si high power BJTs have been largely replaced by GTO thyristors in many power applications.

At the same current and voltage ratings, in general the on-state voltage and the gate driving current of a GTO thyristor are both higher than those of an original thyristor. Si GTO thyristors are fully controllable devices that possess the highest switchable current densities today among all the existing commercial Si power semiconductor devices with active turn-off capabilities. Improvements on the structure, the gate drive, the packaging, and the reverse conducting diode of the GTO thyristor device led to the Integrated Gate-Commutated Thyristor (IGCT). Compared with the original GTO thyristors, IGCTs have improved switching characteristics, allowing operation without dV/dt snubber at high current densities. Also, IGCTs provide reduced switching losses and external driving requirements. Featuring integrated low inductance gate drives, IGCTs are popular in MVA high voltage power applications [8].

Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) are another type of fully controllable devices introduced in 1963 [9] that first made an impact on low voltage electrical signal processing in the 1970s [10]. In 1978, devices based on the same basic principles with a significant increase in the scale, namely power MOSFETs, made a similar impact on power electronic applications. Power MOSFETs feature high static gate impedance which results in low driving power consumption for gate drives. Another advantage of power MOSFETs is rapid switching. The typical operating frequencies of power MOSFETs can be up to two orders of magnitude higher than that of GTO thyristors. The large Safe Operating Area (SOA) and the capability to withstand high dV/dt rates make power MOSFETs a desirable choice in high frequency power electronic circuits. However, as power MOSFETs are based on unipolar carrier transport, the on-state resistance increases greatly as the maximum blocking voltage increases, which limits the use of Si power MOSFETs at high voltage ratings. In general, the voltage ratings of Si power MOSFETs are below 1000 V, but commercial Silicon Carbide (SiC) power MOSFETs rated 1700 V and 225 A have appeared, e.g. Wolfspeed/Cree CAS300M17BM2.

Until early 1980s there had been two major concepts in power semiconductor devices: bipolar devices, e.g. power BJTs and GTO thyristors, and unipolar devices, e.g. power MOSFETs. These two device concepts each possess unique advantages while are subject to different drawbacks. After power MOSFETs were reported, it was realised that a proper integration of a MOSFET and a BJT will lead to a breakthrough in power semiconductor devices. The combination of the reduced on-state driving requirements and the rapid switching of power MOSFETs and the low on-state losses of BJTs was considered a great step towards the standards of ideal power semiconductor devices.

In 1983, the breakthrough was achieved with the Insulated Gate Bipolar Transistor (IGBT) reported by Baliga, the name of which was Insulated Gate Transistor at first [11]–[14]. In the same year a similar device named Conductivity-Modulated Field Effect Transistor (COMFET) was reported by Russell [15]. Since then, the ratings and the performance of IGBTs have been improved significantly. Successfully combining the advantages of power MOSFETs and power BJTs, IGBTs are now preferable in numerous high voltages, low switching frequencies and high output power electronic systems [16]–[18].

Due to the superior performance, IGBTs replaced power BJTs and are competitive with power MOSFETs, as commercial IGBTs with operating frequencies of up to 150 kHz have appeared [19]. After years of research and development, commercial IGBT modules of 6500 V and 750 A, e.g. Infineon FZ750R65KE3, 3300 V and 1500 A, e.g. Infineon FZ1500R33HE3, and 1700 V and 3600 A, e.g. Infineon FZ3600R17HE4, have appeared. Modern IGBTs are capable of challenging GTO thyristors in high power applications with their rapid switching, large Reverse Bias Safety Operating Area (RBSOA) and low driving requirements. In recent years, with the latest advancements in power semiconductor technologies, such as trench gate and Field-Stop (FS) design concepts, IGBTs have dominated medium to high voltage, medium power electronic systems, and is competitive in high voltage, high power electronic systems.

The innovations in WBG semiconductor technologies also contribute to the development of power semiconductor devices. Commercial SiC power devices are gaining popularity in 650 V to 1700 V classes, which overlap with the popular voltage classes of Si IGBTs. Compared with Si IGBTs, due to the high critical electric field of SiC, the same blocking voltage can be supported by a SiC drift region of a low thickness and a high doping concentration, which enables the use of unipolar current conduction for the on-state. As a result, SiC MOSFETs feature reduced switching losses at the same specific on-state performance due to the absence of excess carriers in the on-state. When SiC device technologies mature, SiC power devices will lead to a breakthrough in power electronics, although this is anticipated to extend over some years as in the case of Si IGBTs.

#### 1.1.1 An Introduction to Operations of IGBTs

One of the basics in power electronics is converting electric power between various forms. Power electronic converters are versatile due to their adaptability to the changes in input conditions and output requirements. The maximum efficiency of modern power electronic converters can exceed 90% depending on the application and the operating conditions. Power electronic converters are designed to reduce internal energy losses, e.g. the operations of IGBTs in the gate voltage controlled active region of operation, where at a certain gate voltage the device current is considered to be saturated with increases in the device voltage. For a low-loss on-state, the IGBTs are in the linear region of operation, where the relation between the increases in the device voltage and the increases in the device current is near linear.

Due to diffusion, drift, and recombination of the carriers in semiconductor devices, IGBT switching does not complete instantly. Typical IGBT switching creates an overlap between high device current and high device voltage that causes significant losses, especially under inductive

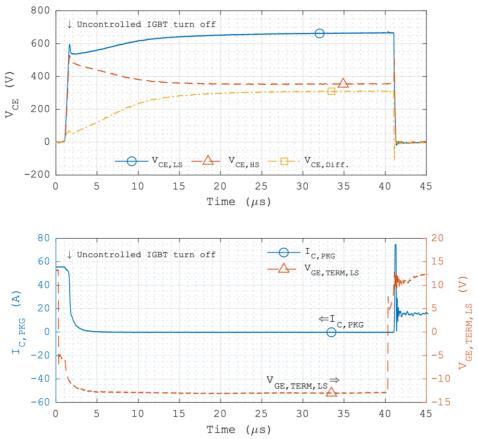

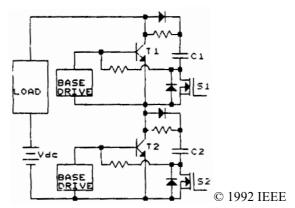

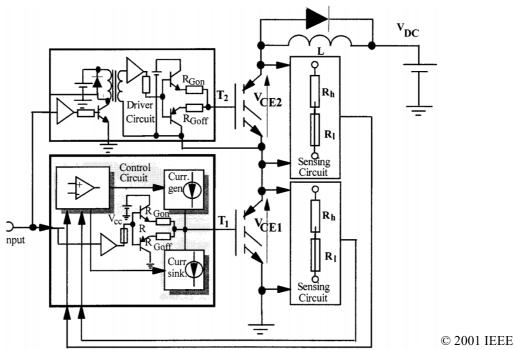

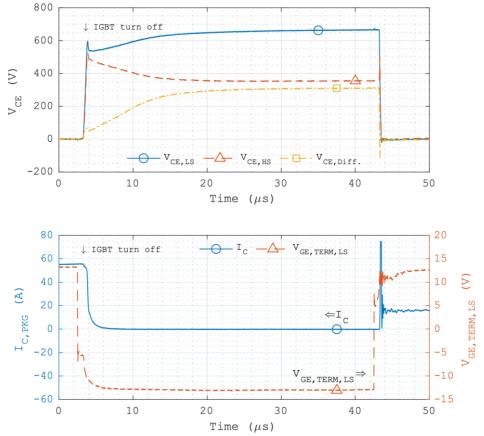

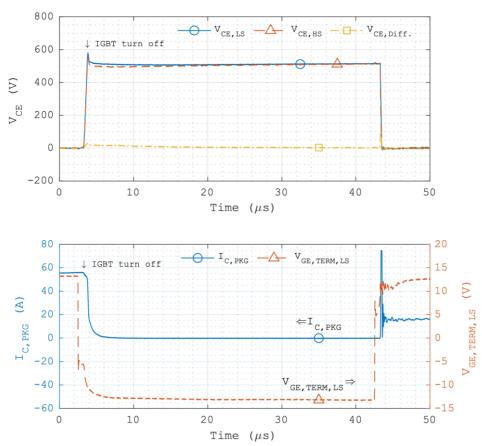

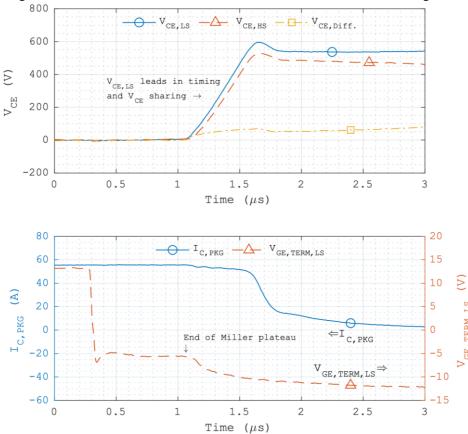

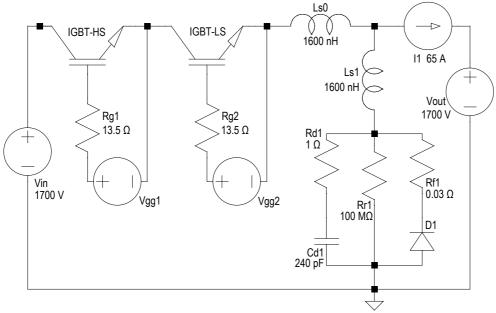

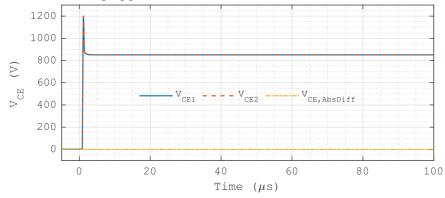

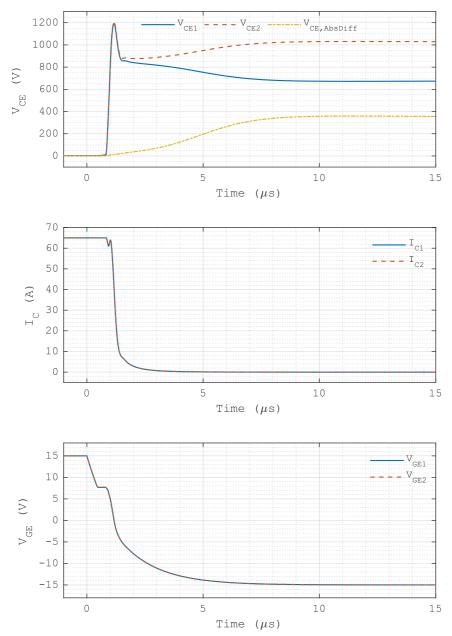

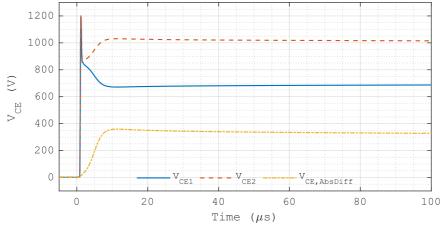

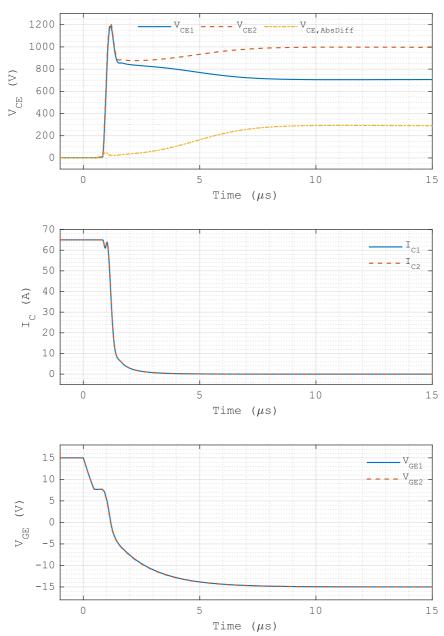

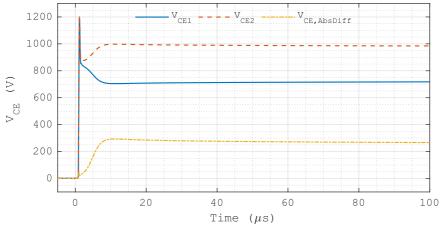

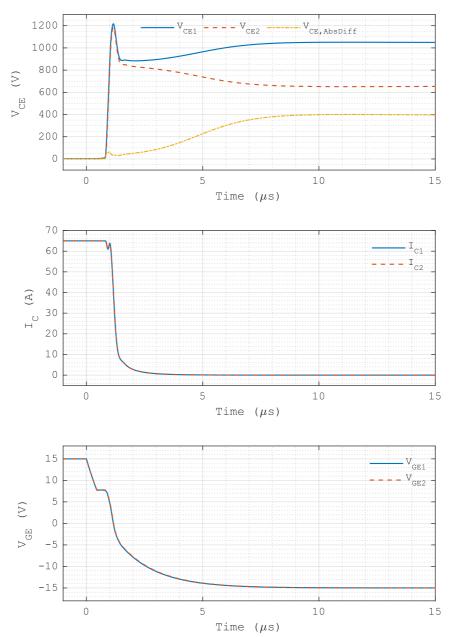

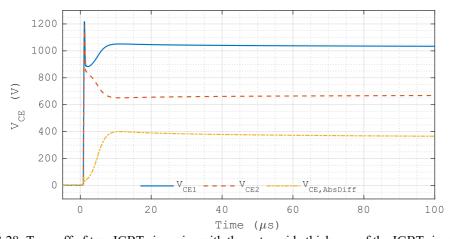

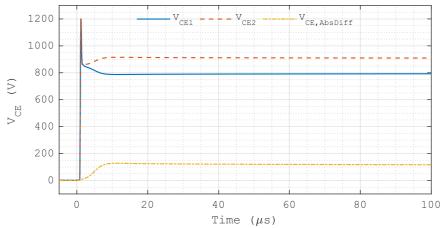

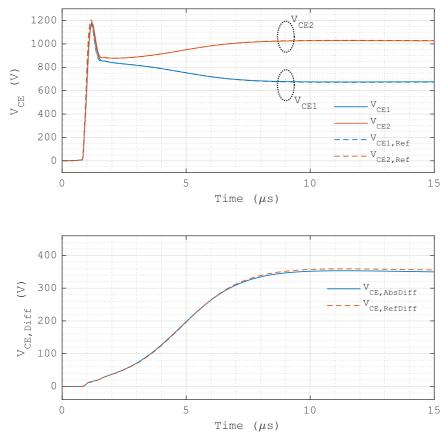

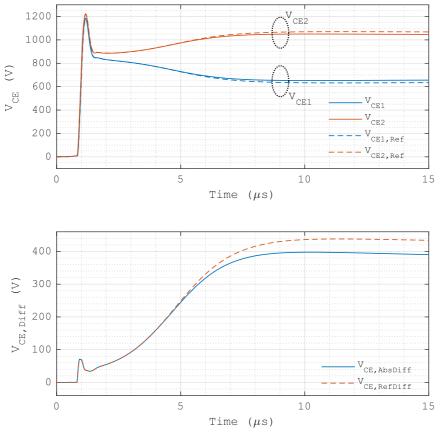

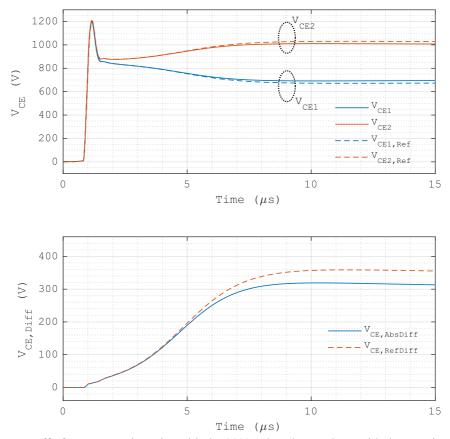

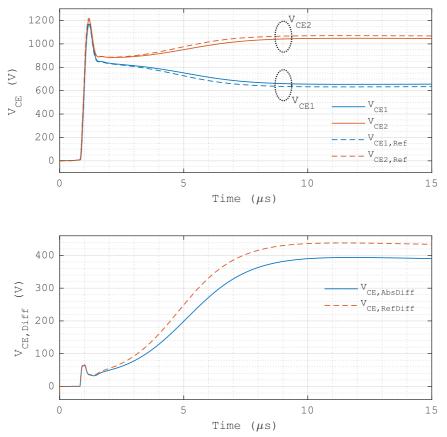

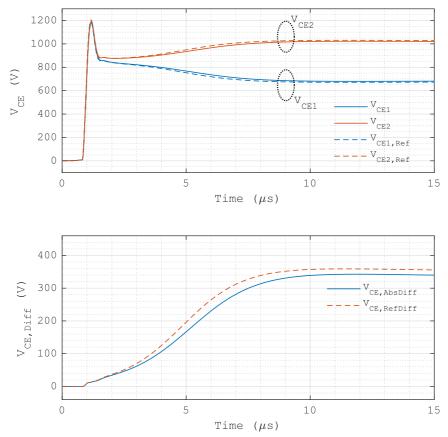

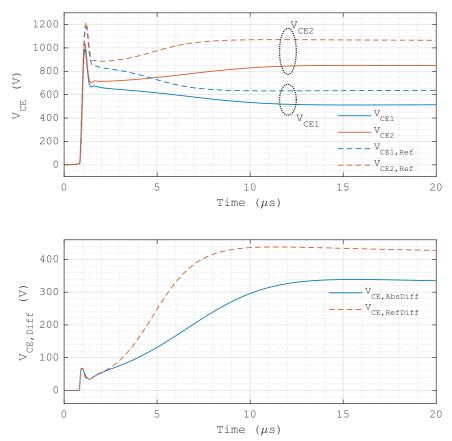

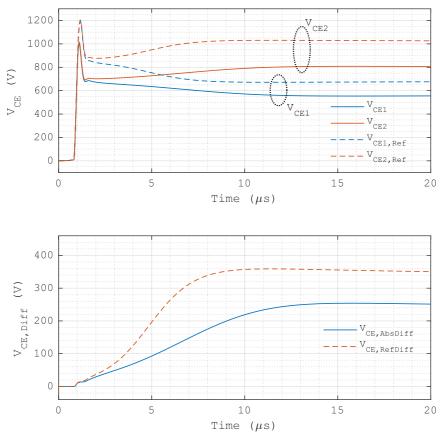

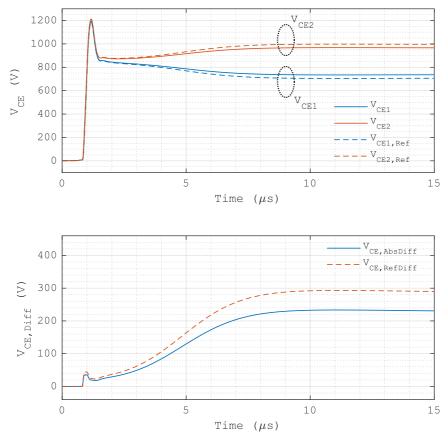

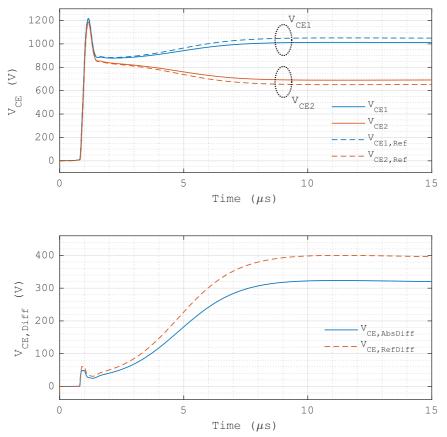

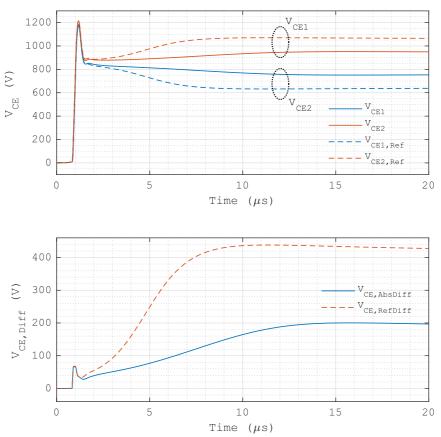

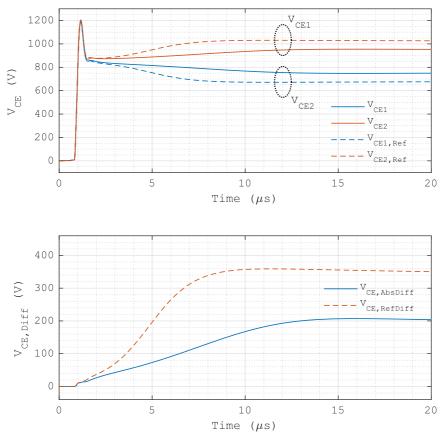

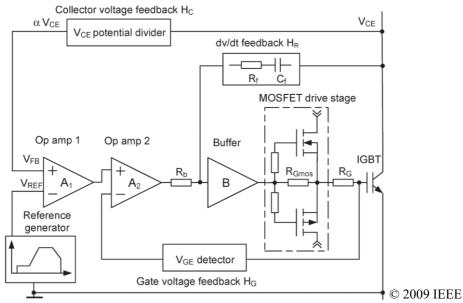

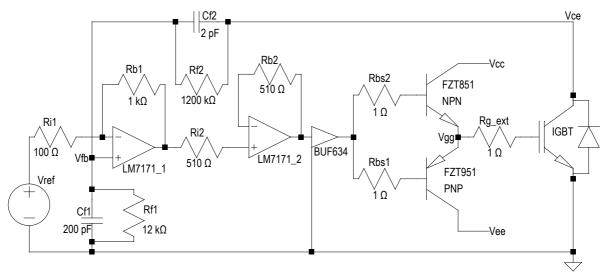

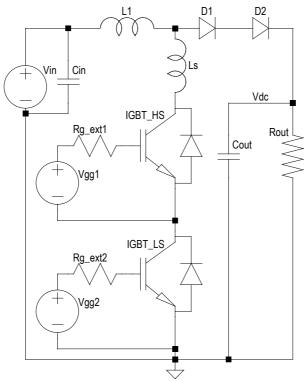

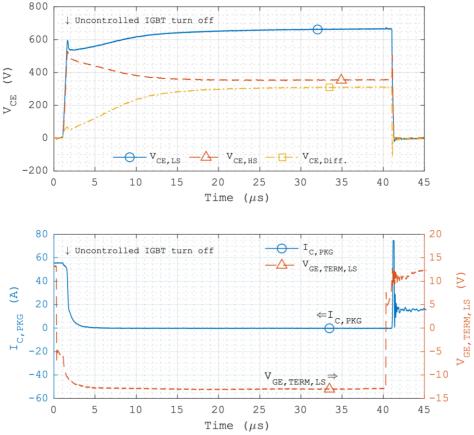

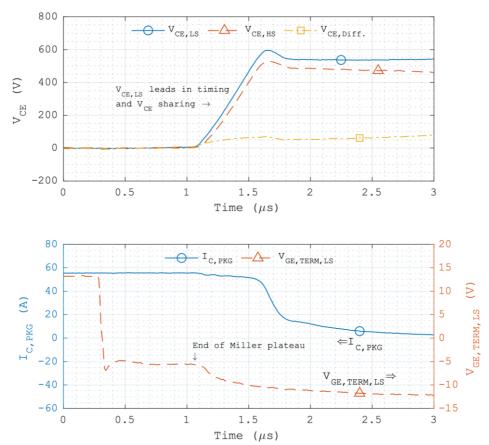

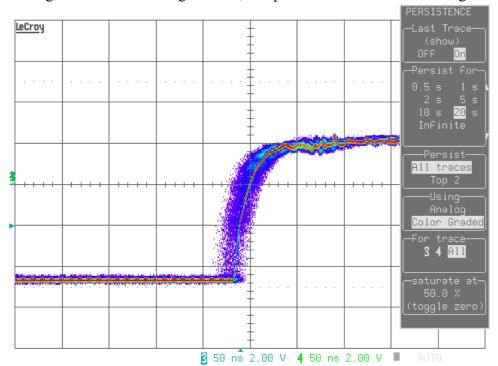

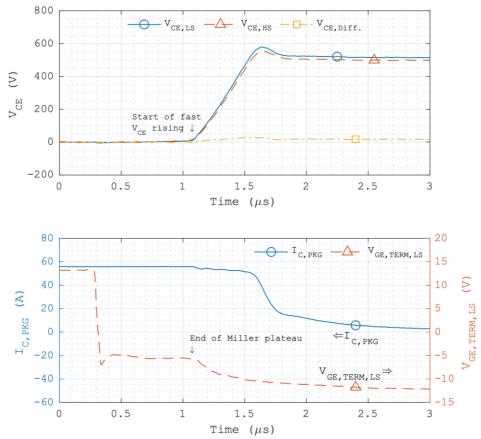

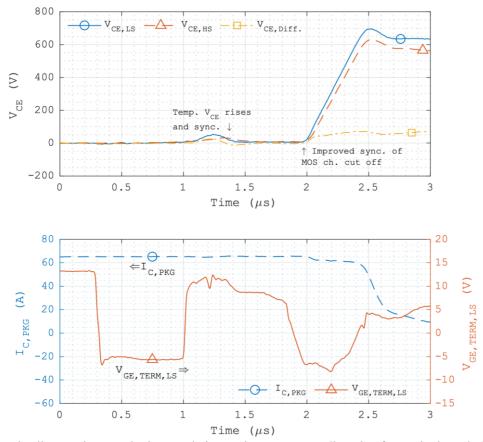

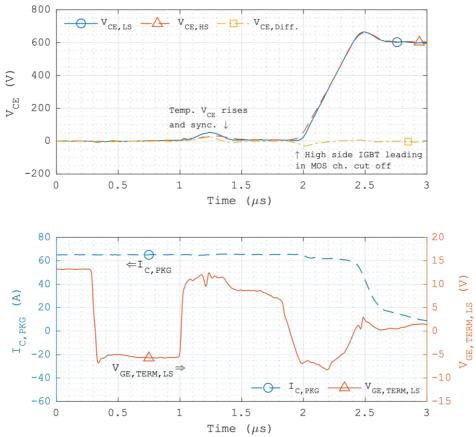

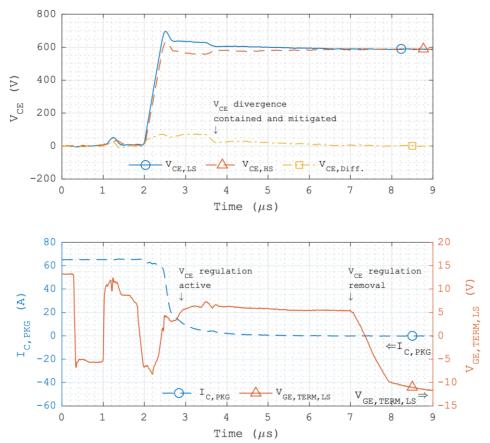

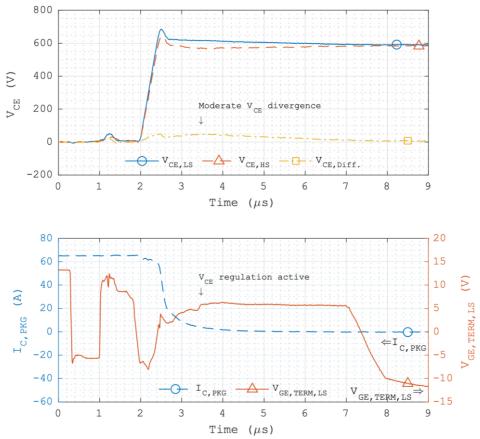

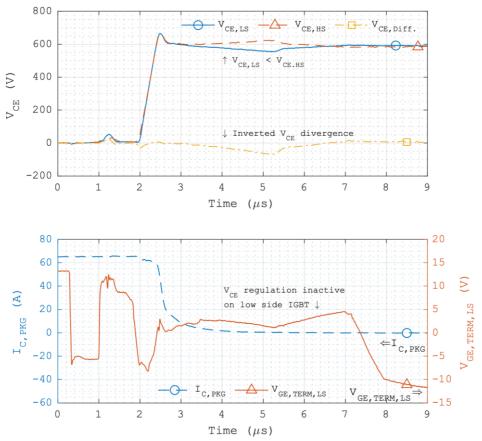

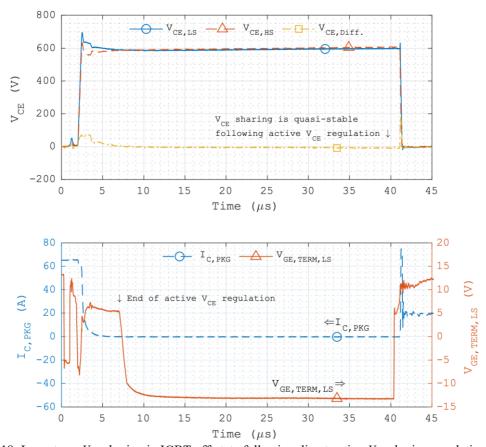

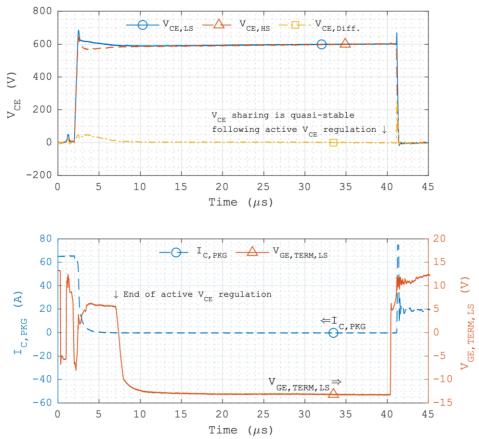

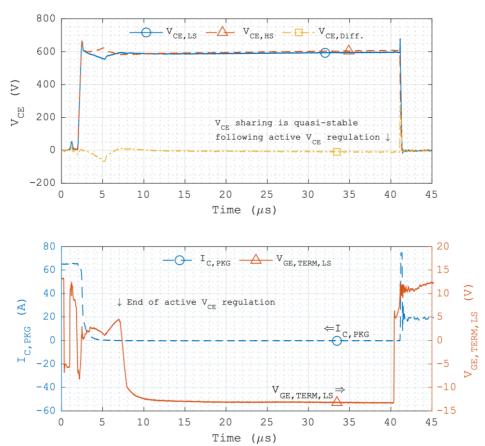

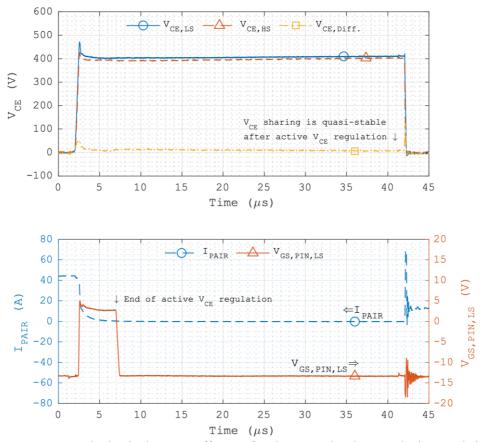

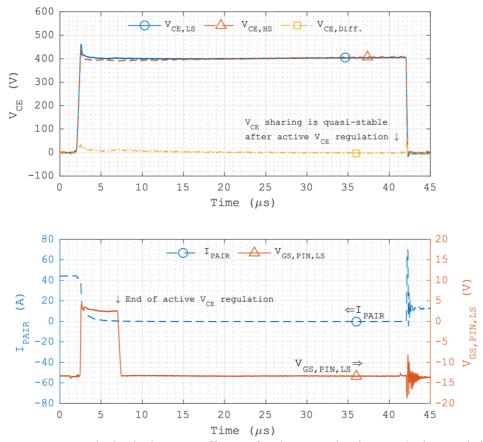

Figure 1.1: An experiment example of the uncontrolled switching of two series-connected IGBTs under inductive load condition.

load conditions which are common in power electronic converters. In inductive IGBT turn-on, the device voltage will remain at near the DC level until the device current reaches the load current. Often, a current overshoot is observed as the FreeWheeling Diode (FWD) requires reverse recovery. Similarly, in inductive IGBT turn-off, the device current will remain at near the load level until the device voltage reaches the DC level. Often, a voltage overshoot is observed due to the stray inductance in the Current Commutation Loop (CCL). An example of uncontrolled switching of two FS IGBTs in series connection under inductive load condition is shown in Figure 1.1 with diverged voltage sharing during the turn-off, the off-state, and the turn-on. Due to the internal gate resistance inside the IGBT module, the gate-emitter voltage measured is different from that of the IGBT chip. Normally operation of IGBTs in the gate voltage controlled active region is only expected in switching events.

#### 1.1.2 General Limits in Commercial Si IGBTs

Until 2016, commercial IGBTs are Si based and are subject to compromises between fabrication cost and multiple performance aspects arising from the limits in Si properties. For Si IGBTs, a higher voltage rating will result in a higher on-state voltage at a given current density. Reducing the on-state voltage at a certain voltage rating can be achieved by increasing the on-state excess carrier concentration, which will reduce the turn-off speed and increase the turn-off losses.

For Si IGBTs, to achieve a forward-blocking voltage of 5 kV, the theoretical maximum operating frequency will be limited to 500 Hz, and to achieve a forward-blocking voltage of 10 kV, the theoretical maximum operating frequency will be further limited to 230 Hz [17]. An

alternative approach for reducing the on-state voltage is increasing the IGBT active chip area. As the current density is reduced, the on-state voltage at a given load current decreases. But with the increased active chip area the fabrication cost to achieve a given current rating increases.

The pursuit for the ideal power semiconductor device has inspired many innovations in power semiconductor technologies. Still, modern commercial power semiconductor devices are subject to compromises between performance, fabrication, and cost. To fulfil the requirements of high-power converters, semiconductor chips and devices are often operated together. Multiple chips are often connected in parallel in a package to provide a high current rating. Several devices are operated in parallel for a load current beyond the highest current rating provided in a product line. Most modern IGBTs have positive temperature coefficient of resistance that is favourable for parallel on-state current sharing. Still, current sharing between chips and devices needs careful attention, especially in switching events.

Similarly, to support a high DC link voltage, IGBTs are often operated in series connection, although the form of the series connection varies. The uncontrolled switching of IGBTs in series connection with evenly distributed voltage sharing between the IGBTs is challenging under practical conditions. The inevitable variations in device parameters and control errors can cause large divergence in the voltage sharing. Snubbers can limit the voltage divergence at the cost of additional switching losses. Nonetheless, large numbers of series-connected thyristors have been in use for many years with the assistance of snubbers.

Appropriate active feedback control on IGBTs can also regulate the turn-off voltage sharing of IGBTs in series connection. Although offering an improved trade-off between voltage regulation effects and additional losses, the implementation of such active feedback control can be sophisticated.

#### 1.2 An Introduction to the Relevant Basics of Si IGBT Physics

An introduction to the relevant basics of Si IGBT physics is essential to establish an understanding of the turn-off voltage sharing between Si IGBTs in series connection. Here for Si IGBTs with large cell dimensions, magnetic effects, differences between carrier temperature and lattice temperature, and ultra-short distance effects are not considered. Also, IGBT physics that are irrelevant to the concerned topics of this thesis are not included.

It is also reasonable to assume that IGBTs of the same model are operated in series connection, where differences between the IGBT devices accumulated in the manufacturing processes that affect the turn-off  $V_{CE}$  sharing are of small degrees. The following IGBT physics are intended for a general understanding rather than detailed modelling.

#### 1.2.1 Intrinsic Carrier Concentration

Intrinsic carriers exist in silicon semiconductor material due to thermal generation. The concentration of the intrinsic carriers is determined by the energy bandgap  $E_G$  and the density of states in the conduction band  $N_C$  and the valence band  $N_V$  [20]–[22]:

$$n_i = \sqrt{np} = \sqrt{N_C N_V} \exp\left(-\frac{E_G}{2kT}\right)$$

Equation 1.1

where k is the Boltzmann's constant 1.38×10<sup>-23</sup> J/K, T is the absolute temperature. In silicon, an expression of the  $n_i$  of Si with good agreement near 300 K is [21], [23]:

$$n_i = 9.15 \times 10^{19} (T/300)^2 \exp\left(-\frac{6880}{T}\right) cm^{-3}$$

Equation 1.2

#### 1.2.2 Impact Ionisation Coefficients

Impact ionisation is related to the carrier generation by high electric fields in semiconductors, e.g. in the depletion region of an IGBT with a high  $V_{CE}$ . The impact ionisation coefficient for electrons  $(\alpha_n)$  or holes  $(\alpha_p)$  is defined as the number of electron-hole pairs created by an electron or a hole traversing 1 cm in the depletion region along the direction of the electric field. In Si the impact ionisation coefficients satisfy Chynoweth's Law [24]:

$$\alpha = a_{\infty} e^{-b/E}$$

Equation 1.3

where E is the electric field component in the direction of current flow, with separate parameters for electrons and holes around the room temperature [25]:

|           | $a_{\infty}$ (cm <sup>-1</sup> ) | b (V/cm)              | Condition                                                                                                  |

|-----------|----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------|

| Electrons | 7.03×10 <sup>5</sup>             | 1.231×10 <sup>6</sup> | $1.75 \times 10^5 \text{ V} \cdot \text{cm}^{-1} \le E \le 6.0 \times 10^5 \text{ V} \cdot \text{cm}^{-1}$ |

| Holes     |                                  |                       | $1.75 \times 10^5 \text{ V} \cdot \text{cm}^{-1} \le E \le 4.0 \times 10^5 \text{ V} \cdot \text{cm}^{-1}$ |

| 110168    | 6.71×10 <sup>5</sup>             | $1.693 \times 10^6$   | $4.0 \times 10^5 \text{ V} \cdot \text{cm}^{-1} \le E \le 6.0 \times 10^5 \text{ V} \cdot \text{cm}^{-1}$  |

$a_{\infty}$  is relatively constant with temperature [26], [27]. For electrons  $db_n/dT \approx 1.3 \times 10^3$  cm/V°K, and for holes  $db_p/dT \approx 1.1 \times 10^3$  cm/V°K [26].

#### 1.2.3 Carrier Mobility

Here, only conductivity carrier mobility is considered for the scope of Si power devices. In general, carrier drift velocity is related to electric field and scattering. Carrier drift velocity increases until scattering occurs, which is between carriers and lattices, ionised dopants, or other free carriers [22], [28], [29]. Carrier mobility  $\mu$  is defined as the coefficient that relates the electric field E to the average carrier drift velocity  $v_d$  [22], [30]:

$$v_d = \mu E$$

Equation 1.4

The average carrier drift velocity saturates at high electric fields in silicon, often expressed as [22], [30], [31]:

$$v_d = v_m \frac{E/E_c}{[1 + (E/E_c)^{\beta}]^{1/\beta}}$$

Equation 1.5

with separate parameters including temperature dependences for electrons and holes [31], [32], for  $T \ge 250$  K:

The saturation drift velocity is virtually independent of doping concentration [22], [33]. The electric field dependence of carrier mobility can be derived from Equation 1.5 [30]:

$$\mu = \frac{v_m/E_c}{[1 + (E/E_c)^{\beta}]^{1/\beta}} = \frac{\mu_0}{[1 + (E/E_c)^{\beta}]^{1/\beta}}$$

Equation 1.6

where  $\mu_0$  is the low field carrier mobility.

In typical operating temperatures of Si IGBTs, e.g. -40 to 175 °C, the low-field carrier mobility  $\mu_0$  in silicon decreases with temperature [22], [28], [29], [31]. The temperature dependence of the low-field carrier mobility is expressed in [31] as:

$$\mu = AT^{-\gamma}$$

Equation 1.7

with separate parameters for electrons and holes:

|           | $A \text{ (cm}^2\text{K}^{\gamma}/\text{Vs)}$ | γ    |

|-----------|-----------------------------------------------|------|

| Electrons | 1.43×10 <sup>9</sup>                          | 2.42 |

| Holes     | 1.35×10 <sup>8</sup>                          | 2.20 |

which agrees with the temperature dependence in Equation 1.5.

Low-field carrier mobility is related to doping concentration [28], [30], [31], [34]. The doping dependence of low-field carrier mobility at 300 K is expressed in [28], [34] as:

$$\mu = \mu_{min} + \frac{\mu_{max} - \mu_{min}}{1 + (N/C_r)^{\alpha}} - \frac{\mu_1}{1 + (C_s/N)^{\beta}}$$

Equation 1.8

where N is the doping concentration, with separate parameters for electrons and holes:

|           | $\mu_{min}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $\mu_{max}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $\mu_1 \text{ (cm}^2\text{V}^{-1}\text{s}^{-1}\text{)}$ | $C_r$ (cm <sup>-3</sup> ) | $C_s$ (cm <sup>-3</sup> ) | α     | β    |

|-----------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|---------------------------|---------------------------|-------|------|

| Electrons | 68.5                                                           | 1414                                                           | 56.1                                                    | 9.20×10 <sup>16</sup>     | $3.41 \times 10^{20}$     | 0.711 | 1.98 |

| Holes     | 44.9                                                           | 470.5                                                          | 29.0                                                    | 2.23×10 <sup>17</sup>     | $6.10 \times 10^{20}$     | 0.719 | 2.00 |

The dependence of carrier mobility on carrier-carrier scattering becomes significant at high carrier concentrations, e.g. in an IGBT N-drift region under high-level injection where the minority carrier concentration exceeds the doping concentration. The carrier concentration dependence of low-field carrier mobility is expressed in [35]–[37] as:

$$\mu = \mu_{min} + \frac{\mu_{max} - \mu_{min}}{1 + (N/C_r)^{\alpha}} - \frac{\mu_1}{1 + (C_s/N)^{\beta}}$$

Equation 1.9

The carrier mobility in an inversion layer close to the oxide-semiconductor interface, e.g. a MOS channel, in Si IGBTs and MOSFETs is related to surface scattering, including phonon scattering, Coulomb scattering, and surface roughness scattering [38], [39]. As will be discussed later, here the use of a small gate resistance is assumed for the concerned IGBT turn-off in this thesis, which results in an IGBT MOS channel cut-off very early in the fast  $V_{CE}$  rising. And since an IGBT MOS channel in a typical on-state is in the linear region of operation, the surface scattering related to an IGBT MOS channel is less relevant to the topics in this thesis and hence will not be discussed in further detail here.

#### 1.2.4 Carrier Recombination and Recombination Lifetime

In the bulk of a semiconductor under non-equilibrium condition, i.e.  $pn \neq n_i^2$  where p and n are the hole and the electron concentrations, respectively, recombination where  $pn > n_i^2$  and thermal generation where  $pn < n_i^2$  tend to restore the carrier state back to equilibrium. Si IGBTs are designed to achieve high-level injection in the N base, where in typical operation excess carriers exist in the on-state before turn-off. Hence, in inductive IGBT turn-off, carrier recombination is a major process to consider. Since Si is an indirect-bandgap semiconductor, the carrier recombination processes to consider for Si IGBT turn-off are Shockley-Read-Hall (SRH)

recombination and Auger recombination [29], [40]–[42]. Here, the effective recombination lifetime  $\tau_{eff}$  as a combination of the SRH recombination lifetime  $\tau_{SRH}$  and the Auger recombination lifetime  $\tau_{Auger}$  is given by [42], [43]:

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{SRH}} + \frac{1}{\tau_{Auger}}$$

Equation 1.10

#### 1.2.4.1 Shockley-Read-Hall Recombination

In Si as an indirect-bandgap semiconductor, indirect carrier recombination and generation via bulk traps are important carrier transition processes. The single-level recombination involves electron capture and hole capture, and was first described by Shockley and Read [44], and by Hall [45] (SRH), usually referred to as SRH recombination. The net SRH recombination rate U in steady state is described in the general form of [44]–[46]:

$$U = \frac{pn - n_i^2}{\tau_p \left(n + n_i \exp\left(\frac{E_t - E_i}{kT}\right)\right) + \tau_n \left(p + n_i \exp\left(\frac{E_i - E_t}{kT}\right)\right)}$$

Equation 1.11

where p is the hole concentration, n is the electron concentration,  $\tau_p$  is the low-level hole lifetime in heavily doped N-type silicon,  $\tau_n$  is the low-level electron lifetime in heavily doped P-type silicon,  $E_t$  is the trap energy level, and  $E_i$  is the intrinsic Fermi level. The  $\tau_n$  and  $\tau_p$  are dependent on the doping concentration N [47]–[49], described in [49] as:

$$\tau_n = \frac{\tau_{n0}}{1 + \frac{N}{N_{ref}}}$$

Equation 1.12

$$\tau_p = \frac{\tau_{p0}}{1 + \frac{N}{N_{ref}}}$$

Equation 1.13

where  $\tau_{n0} = 30 \,\mu s$  is the low-concentration electron lifetime,  $\tau_{p0} = 10 \,\mu s$  is the low-concentration hole lifetime, and  $N_{ref} = 10^{17} \,\mathrm{cm}^{-3}$  is the reference roll-off concentration.

The N<sup>-</sup> drift region and the N buffer region in a modern FS IGBT in a typical on-state are under high-level injection, where the excess electron and hole concentrations  $\delta n$  and  $\delta p$ , respectively, satisfy  $\delta n \approx \delta p > N_D > n_i$ , where  $N_D$  is the N-type doping concentration. As  $n = n_0 + \delta n$  and  $p = p_0 + \delta p$  where  $n_0$  and  $p_0$  are the equilibrium electron and hole concentrations, respectively, the SRH lifetime under high-level injection becomes [43], [44]:

$$\tau_{SRH} = \frac{\delta n}{U} \approx \frac{\tau_p \left( n_0 + \delta n + n_i \exp\left(\frac{E_t - E_i}{kT}\right) \right) + \tau_n \left( p_0 + \delta p + n_i \exp\left(\frac{E_i - E_t}{kT}\right) \right)}{n_0 + p_0 + \delta n}$$

Equation 1.14

Assuming  $E_t$  is near  $E_i$ , the high-level SRH lifetime  $\tau_{SRH,HL}$  approximates [43]:

$$\tau_{SRH,HL} \approx \tau_n + \tau_p$$

Equation 1.15

#### 1.2.4.2 Auger Recombination

In Si regions where the carrier concentration is high, a three-particle carrier transition process, Auger recombination, is important in addition to the SRH recombination. Auger recombination is a band-to-band process that transfers the excess energy from the recombination process to a third free electron, the e-e-h process, or hole, the e-h-h process [50]–[55]. Traditional modelling of the Auger recombination rate is  $R_{eeh} = C_n n^2 p$  for the e-e-h process and  $R_{ehh} = C_p n p^2$  for the e-

h-h process, where  $C_n$  and  $C_p$  are the respective Auger recombination coefficients [51], [54], [55]. Therefore, the total Auger recombination rate  $R_{Auger}$  in [51], [54], [55] is given by:

$$R_{Auger} = R_{eeh} + R_{ehh} = C_n n^2 p + C_p n p^2$$

Equation 1.16

Under low-level injection, the Auger recombination lifetimes in [54], [55] are given by, for N-type silicon:

$$\tau_{Auger,n,LL} = \frac{1}{C_{n,LL}N_D^2}$$

Equation 1.17

and for P-type silicon:

$$\tau_{Auger,p,LL} = \frac{1}{C_{p,LL}N_A^2}$$

Equation 1.18

where  $C_{n,LL}$  and  $C_{p,LL}$  are the low-level Auger recombination coefficients for electrons and holes, respectively,  $N_D$  and  $N_A$  are the doping concentrations of N-type and P-type silicon, respectively. For doping concentrations higher than  $2\times10^{18}$  cm<sup>-3</sup>, at T=300 K,  $C_{n,LL}=2.8\times10^{-31}$  cm<sup>6</sup>s<sup>-1</sup> and  $C_{p,LL}=9.9\times10^{-32}$  cm<sup>6</sup>s<sup>-1</sup> as in [51].  $C_{n,LL}$  and  $C_{p,LL}$  have weak dependences on temperature [51], and vary as  $T^{0.6}$  between 195 and 372 K as in [56]. Under high-level injection, the Auger recombination lifetime in [54], [55] is given by, assuming  $\delta n \approx \delta p$ :

$$\tau_{Auger,HL} = \frac{1}{C_a \delta n^2}$$

Equation 1.19

where  $C_a$  is the ambipolar Auger recombination coefficient. For  $\delta n$  between  $1 \times 10^{15}$  to  $2 \times 10^{17}$  cm<sup>-3</sup>,  $C_a = 1.66 \times 10^{-30}$  cm<sup>6</sup>s<sup>-1</sup> as in [57].

From Equation 1.16,  $C_a \equiv C_n + C_p$ , however, the measurement of  $C_a$  reveals that  $C_a$  is generally higher than  $(C_{n,LL} + C_{p,LL})$  [54], [55]. The transition of the Auger recombination coefficients in Equation 1.16 from low-level to high-level is approximated in [54] by:

$$C_{n,eff} = C_{n,LL} \left( \frac{N_D}{N_D + p} \right) + \frac{C_a}{2} \left( \frac{p}{N_D + p} \right)$$

Equation 1.20

$$C_{p,eff} = C_{p,LL} \left( \frac{N_A}{N_A + n} \right) + \frac{C_a}{2} \left( \frac{n}{N_A + n} \right)$$

Equation 1.21

where  $C_{n,eff}$  and  $C_{p,eff}$  are the effective Auger recombination coefficients to replace the respective  $C_n$  and  $C_p$  in Equation 1.16.

#### 1.2.5 Basic Equations for Si Power Devices

The equations included here for Si power devices describes the basics of the internal physics relevant to the low-loss turn-off of modern IGBTs under typical operating conditions.

In Maxwell's equations, the differential form of Gauss's law, Poisson's equation, is useful for describing the electric field distribution:

$$\nabla \cdot \vec{E} = \frac{\rho}{\varepsilon_s}$$

Equation 1.22

where E is the electric field,  $\rho$  is the total charge density,  $\varepsilon_s$  is the permittivity of a semiconductor. In some high voltage vertical Si power devices, such as Si IGBTs, the bulk regions feature uniform horizontal doping profiles and a total thickness considerably greater than the scale of

the cell pitch, for which some analyses can be simplified to One-Dimensional (1D) problems. In these cases, Equation 1.22 can be reduced to:

$$\nabla \cdot \vec{E} = \frac{\partial \vec{E}}{\partial x} = \frac{\rho}{\varepsilon_s} = \frac{q(p - n + N_D - N_A)}{\varepsilon_s}$$

Equation 1.23

where x is the distance, q is the elementary charge, p and n are the hole and electron concentrations, respectively,  $N_D$  and  $N_A$  are the donor and acceptor doping concentrations, respectively.

The steady state conducting current can be approximated by a combination of the drift current due to the electric field and the diffusion current due to the carrier concentration gradient, for electrons and holes [22], [31], [58]:

$$\overrightarrow{J_n} = qn(\mu_n \vec{E}) + qD_n \nabla n$$

Equation 1.24

$$\overrightarrow{J_p} = qp(\mu_p \vec{E}) - qD_p \nabla p$$

Equation 1.25

where  $\overrightarrow{J_n}$  and  $\overrightarrow{J_p}$  are the electron and hole current densities, respectively,  $D_n = (kT/q)\mu_n$  and  $D_p = (kT/q)\mu_p$  are the electron and hole diffusion coefficients, respectively, both given by Einstein relation.  $\mu_n \vec{E}$  and  $\mu_p \vec{E}$  yield the respective electron and hole drift velocities, which saturate at high electric fields with quantitative reductions in  $\mu_n$  and  $\mu_p$ . For 1D problems, Equation 1.24 and Equation 1.25 can be reduced respectively to:

$$\overrightarrow{J_n} = qn(\mu_n \vec{E}) + qD_n \frac{\partial n}{\partial x} = qn(\mu_n \vec{E}) + q\left(\frac{kT}{q}\mu_n\right)\frac{\partial n}{\partial x}$$

Equation 1.26

$$\vec{J_p} = qp(\mu_p \vec{E}) - qD_p \frac{\partial p}{\partial x} = qp(\mu_p \vec{E}) - q\left(\frac{kT}{q}\mu_p\right)\frac{\partial p}{\partial x}$$

Equation 1.27

Due to charge conservation, the net changes in the carrier concentrations are related to the carrier generation and recombination and the current densities, expressed by the continuity equations for electrons and holes [22], [58]:

$$\frac{\partial n}{\partial t} = (G_n - U_n) + \frac{1}{a} \nabla \cdot \overrightarrow{J_n}$$

Equation 1.28

$$\frac{\partial p}{\partial t} = (G_p - U_p) - \frac{1}{a} \nabla \cdot \overrightarrow{J_p}$$

Equation 1.29

where  $G_n$  and  $G_p$  are the respective electron and hole generation rates,  $U_n$  and  $U_p$  are the respective electron and hole recombination rates. For 1D problems, Equation 1.28 and Equation 1.29 can be reduced respectively to:

$$\frac{\partial n}{\partial t} = (G_n - U_n) + \frac{1}{q} \frac{\partial \overrightarrow{J_n}}{\partial x}$$

Equation 1.30

$$\frac{\partial p}{\partial t} = \left(G_p - U_p\right) - \frac{1}{q} \frac{\partial \overrightarrow{J_p}}{\partial x}$$

Equation 1.31

#### 1.3 Introduction to IGBT Structural Components

High voltage Si IGBTs are normally vertical n-channel devices. Such an IGBT can be considered as an integration of a PNP BJT and a n-channel MOSFET that characterises the typical IGBT performance [59]. The semiconductor relevant contents in this thesis are limited to the scope of modern Field-Stop (FS) n-channel vertical Si IGBTs. The schematic diagrams shown in this thesis are not to scale.

Historically, the naming "collector" and "emitter" of the current conducting terminals of an IGBT was for the compatibility of IGBTs with power BJT circuits when IGBTs were first introduced [16]. The collector and the emitter of the equivalent BJT in an IGBT do not refer respectively to the "collector" and the "emitter" terminals of the IGBT.

#### 1.3.1 PN Junction and Depletion Region

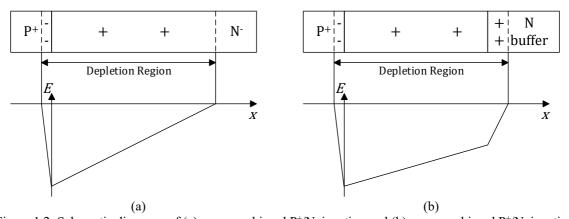

A basic PN junction consists of a P-type region and a N-type region adjacent to each other. In Si IGBTs, reverse biased PN junctions are used to block high voltages. High voltage n-channel IGBTs feature lightly doped N<sup>-</sup> drift regions. In such an IGBT, this N<sup>-</sup> drift region forms a P<sup>+</sup>/N<sup>-</sup> junction with the heavily doped P base region, also referred to as the P body region. When this P<sup>+</sup>/N<sup>-</sup> junction is reverse biased, the depletion region is distributed mostly in the lightly doped N<sup>-</sup> drift region according to Equation 1.23, as illustrated by the 1D schematic diagram in Figure 1.2 (a). Therefore, in an IGBT a forward-blocking C-E voltage  $V_{CE}$  is supported mostly in the N<sup>-</sup> drift region, in which case the P<sup>+</sup>/N<sup>-</sup> junction can be considered as an abrupt PN junction. For the depletion region in the N<sup>-</sup> drift region, the 1D Poisson's equation can be reduced to:

$$-\frac{\partial^2 v}{\partial x^2} = \frac{\partial \vec{E}}{\partial x} = \frac{\rho}{\varepsilon_S} = \frac{q(p - n + N_D)}{\varepsilon_S}$$

Equation 1.32

where for a n-channel IGBT in a forward-blocking state, p is related to the hole current in the depletion region and n is related to the electron current in the depletion region.

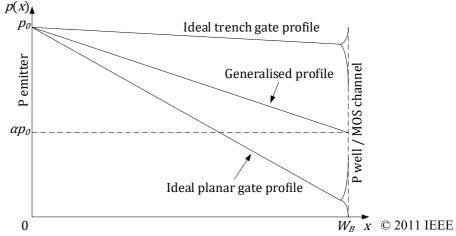

Field-Stop (FS) IGBT design and similar design concepts such as Soft Punch-Through and Light Punch-Through are widely adopted in modern IGBTs [59]–[62]. In general, these IGBT design concepts feature a N buffer of a doping concentration higher than that of the N<sup>-</sup> drift region that only stops the electric field in the depletion region from reaching the vicinity of the backside P emitter. The schematic diagram in Figure 1.2 (b) illustrates a such reverse biased P<sup>+</sup>/N junction with a N buffer where the electric field in the depletion region is stopped by the N buffer. Equation 1.32 also applies to the depletion region in the N-type region here. FS IGBTs achieve reduced device thicknesses and conducting losses while achieving reduced switching losses due to the reduced on-state excess carriers in the N bulk regions [59].

Figure 1.2: Schematic diagrams of (a) a reverse biased  $P^+/N^-$  junction and (b) a reverse biased  $P^+/N^-$  junction with the electric field "stopped" by a N buffer.

#### 1.3.2 Power BJT

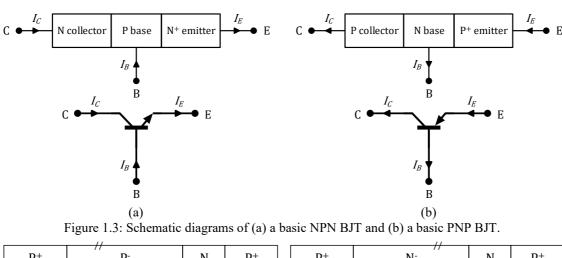

A basic n-channel IGBT includes a PNPN structure, in which the PNP component forms an equivalent BJT with the base current provided by the MOS channel in the IGBT. In normal operation, a BJT is fully controllable by the base current  $I_B$ . Regarding the general doping profile, a basic BJT consists of a NPN or PNP structure. Schematic diagrams of a NPN BJT and a PNP BJT are shown in Figure 1.3 (a) and (b), respectively.

Regarding the basic operations of power BJTs, the following discussion considers a basic PNP power BJT, the same basic type as the equivalent PNP BJT in a n-channel IGBT, and only major carrier transport mechanisms. Complementary conclusions are applicable to NPN power BJTs. Under normal forward voltage blocking, the collector-base junction is reverse-biased, and the depletion region is distributed mostly in the wide/thick and lightly doped collector region. In a basic PNP power BJT, when the P<sup>+</sup> emitter to N base junction is forward-biased, electrons diffuse from the N base into the P<sup>+</sup> emitter and holes are injected from the P<sup>+</sup> emitter into the N base. Referring to the directions in Figure 1.3 (b), in a typical PNP power BJT the N base is narrow/thin so that the majority of the injected holes diffuse through the N base and are collected by the P collector, while only a small proportion of the injected holes recombine in the N base.

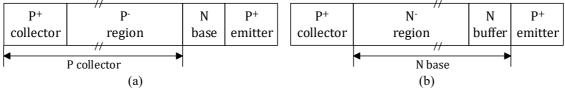

Referring to the directions in Figure 1.3, in a typical power BJT the collector region is normally wide/thick while the base region is narrow/thin. However, in a n-channel IGBT the equivalent PNP BJT has a narrow/thin P<sup>+</sup> collector region and a wide/thick N<sup>-</sup> base region. This difference is shown in the respective schematic diagrams in Figure 1.4.

Power BJTs normally function as power switches in dedicated power BJT circuits. The design and the operation of power BJTs are for reducing operating losses while providing high voltage and current ratings, which are significantly different from those of signal BJTs. To reduce on-state losses, conductivity modulation by high-level injection is applied to the lightly

Figure 1.4: Schematic diagrams of (a) a basic PNP power BJT and (b) the equivalent PNP BJT in a n-channel IGBT.

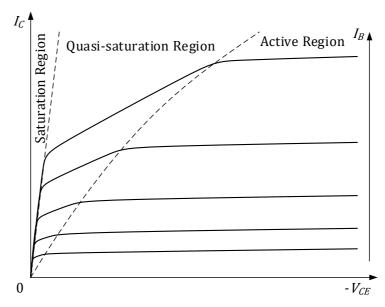

Figure 1.5: Schematic diagram of basic DC I-V characteristics of a NPN power BJT.

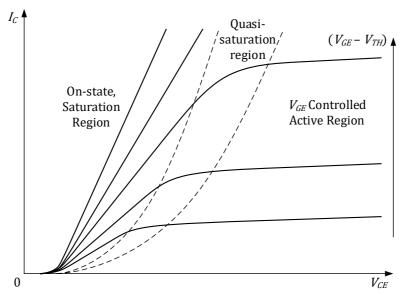

doped regions of a power BJT. For a forward conducting power BJT, its operation modes include active mode, quasi-saturation mode, and saturation mode, as indicated in the schematic diagram of the basic DC *I-V* characteristics of a PNP power BJT shown in Figure 1.5. Breakdown characteristics are not included in Figure 1.5.

In the active mode, the emitter-base junction is forward-biased while the collector-base junction is reverse-biased. A depletion region is formed across the reverse-biased collector-base junction. In static or quasi-static situation, at a certain collector-emitter voltage  $V_{CE}$ , the collector current  $I_C$  increases with the base current  $I_B$ .

In the quasi-saturation mode, the emitter-base and the collector-base junctions are both forward-biased. Part of the lightly doped collector region near the collector-base junction, i.e. part of the P<sup>-</sup> region near the P<sup>-</sup>/N-base junction in Figure 1.4 (a), is under high-level injection and is conductivity-modulated as the conductivity is increased. Depending on the doping profile, the base region may not be entirely under high-level injection. At a given  $V_{CE}$ , the  $I_C$  increases with the  $I_B$ , and at a given  $I_B$ , the  $I_C$  increases with the  $V_{CE}$ .

In the saturation mode, both the emitter-base and the collector-base junctions are forward-biased. The entire lightly doped collector region, i.e. the P<sup>-</sup> region in Figure 1.4 (a), is under high-level injection and is conductivity-modulated. Often, the base region is also under high-level injection. The  $I_C$  increases with the  $V_{CE}$  at a higher rate compare with that in the quasi-saturation mode at the same  $I_B$ .

For a typical power BJT in forward conducting state considering only major current components, the  $I_C$  is related to the  $I_B$  by the common-emitter current gain  $h_{FE}$ :

$$h_{FE} = \frac{I_C}{I_B}$$

Equation 1.33

In normal DC situations, the  $h_{FE}$  is dependent on the  $I_C$ . At a very low  $I_C$  where the emitter-base recombination current is comparable to the effective emitter diffusion current through the base, the  $h_{FE}$  is relatively low and increases with the  $I_C$ . However, at a higher  $I_B$  where the base

becomes under high-level injection, e.g. in the quasi-saturation and saturation modes, the  $h_{FE}$  decreases with the  $I_C$  due to the increase in the effective base doping level and the extension of the electrical base caused by the injected high-level excess carriers. Also, in general,  $h_{FE}$  decreases with the effective base width/thickness [22], [63]–[68].

For the equivalent PNP BJT in a n-channel IGBT, in forward conducting state its wide/thick N base under high-level injection results in a low  $h_{FE}$ . Due to the significant differences in device geometry between a typical PNP power BJT and a n-channel IGBT, the on-state carrier distribution of the equivalent PNP BJT in a n-channel IGBT will be discussed separately.

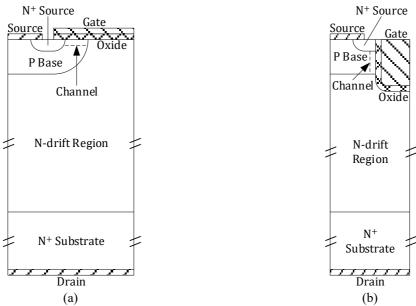

#### 1.3.3 Power MOSFET

A basic n-channel IGBT includes a n-channel MOSFET structure. Since modern high voltage IGBTs are mostly n-channel devices, the following discussions considers a basic n-channel power MOSFET and only major carrier transport mechanisms. Complementary conclusions are applicable to p-channel devices. Schematic diagrams of basic 2D vertical n-channel planar-gate and trench-gate power MOSFETs are shown in Figure 1.6 (a) and (b), respectively, in the form of half-cell vertical cross-sections. Normally, under forward voltage blocking, the N-drift region to P base junction is reverse-biased, and the depletion region is distributed mostly in the thick and lightly doped N-drift region.

MOSFETs are unipolar devices without conductivity modulation by high-level injection in the on-state. In normal operation, MOSFETs are fully controllable by the gate-source voltage  $V_{GS}$ . The current conduction in a MOSFET is controlled by a MOS channel formed by an inversion layer. The n-type MOS channels, n-channels, in power MOSFETs or IGBTs are mostly surface inversion channels formed by electrons. The basic principles of MOS channels are the same for planar-gate and trench-gate devices.

In a n-channel MOSFET, when the gate-source voltage  $V_{GS}$  exceeds the threshold voltage  $V_{TH}$ , electrons from the semiconductor regions are attracted towards the interface between the

Figure 1.6: Schematic diagrams of (a) a basic vertical n-channel planar power MOSFET and (b) a basic vertical n-channel trench power MOSFET.

gate oxide and the semiconductor region, and an inversion layer of electrons is formed in the P base adjacent to the gate oxide. With positive drain-source voltage  $V_{DS}$ , electrons from the N<sup>+</sup> source flow through a MOS channel in the P base formed by that inversion layer and into the N-drift region. The electrons through the MOS channel spread across the width of the N-drift region and flow towards the drain terminal.

In the general scope of vertical power MOSFETs and IGBTs, a trench MOS gate provides direct access to the bulk regions for the electrons through the vertical MOS channel, compared with a planar MOS gate. This avoids the depletion region formed by the reverse-biased N-drift region to P base junction under a forward  $V_{DS}$ . Consequently, the reduced crowding and path length of the electrons out of the MOS channel in the MOS gate area improve the MOS channel density and the on-state resistance.

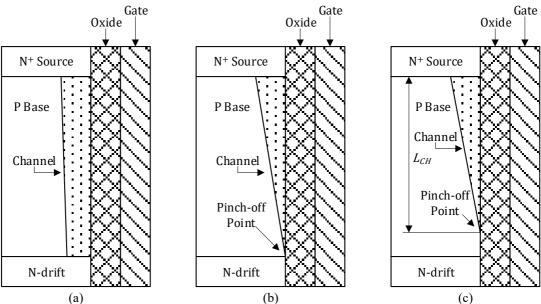

Regarding DC I-V characteristics, long-channel and low-field carrier mobilities are assumed for the MOS channels in n-channel power MOSFETs and IGBTs. The Shockley MOSFET model [69] is widely used in this situation [22], [70], [71]. For a n-channel power MOSFET, when the  $(V_{GS} - V_{TH}) > 0$  and the  $V_{DS} \ll V_{DS,sat}$ , the MOS channel is nearly resistive for the MOS channel current, Figure 1.7 (a), where  $V_{DS,sat}$  is the drain saturation voltage at which the drain current  $I_D$  starts to saturate to  $I_{D,sat}$ . This nearly resistive regime is referred to as the linear region of operation, indicated in the schematic diagram shown in Figure 1.8. The  $V_{DS,sat}$  and the  $I_{D,sat}$  will be discussed later.

As the  $V_{DS}$  increases and is reaching the  $V_{DS,sat}$ , due to the MOS channel resistance the voltage along the MOS channel increases and starts to reduce the effect of the  $(V_{GS} - V_{TH})$  on inducing the inversion charges near the drain end of the MOS channel. Consequently, the inversion charges near the drain end of the MOS channel are reduced, and the  $I_D$  starts to increase sublinearly with the  $V_{DS}$ . This sublinear regime is referred to as the nonlinear region of operation, indicated in the schematic diagram shown in Figure 1.8.

Figure 1.7: Schematic diagrams of a basic MOS channel: (a) in the linear region, (b) when  $V_{DS} = V_{DS,sat}$ , and (c) in the saturation region.

Figure 1.8: Schematic diagram of DC I-V characteristics of a n-channel power MOSFET.

As the  $V_{DS}$  increases to the  $V_{DS,sat}$ , the inversion charges are eventually reduced to near zero at the drain end of the MOS channel, where the MOS channel starts to pinch off, Figure 1.7 (b). As the  $V_{DS}$  exceeds the  $V_{DS,sat}$ , the pinch-off point shifts towards the source end of the MOS channel, and the effective channel length  $L_{CH}$  is reduced slightly, Figure 1.7 (c). The voltage at the pinch-off point with respect to the source remains unchanged. The additional voltage is supported by a depletion region from the pinch-off point along the MOS channel into the N-drift region, formed by the reverse-biased N-drift region to P base junction. The  $I_D$  essentially saturates with the  $V_{DS}$  to the  $I_{D,sat}$ , although a minor increase in the  $I_D$  may be observed due to the slightly reduced  $L_{CH}$ . This saturation regime is referred to as the saturation region of operation, indicated in the schematic diagram shown in Figure 1.8.

In the Shockley MOSFET model, the  $V_{DS,sat}$  is described as:

$$V_{DS,sqt} = (V_{GS} - V_{TH})$$

Equation 1.34

For a n-channel power MOSFET, Equation 1.34 is applicable to the MOS channel area. The resistance and the voltage across the bulk regions, e.g. the N-drift region and the  $N^+$  substrate, need to be considered in determining the actual  $V_{DS,sat}$ .

In the saturation region where  $V_{DS} \ge V_{DS,sat}$ , the  $I_{D,sat}$  is described as:

$$I_{D,sat} = \frac{Z}{2L_{CH}} \mu_{n,CH} C_{ox} (V_{GS} - V_{TH})^2$$

Equation 1.35

where Z is the channel width orthogonal to the cross-sections shown in Figure 1.7,  $\mu_{n,CH}$  is the electron mobility in the MOS channel, and  $C_{ox} = (\varepsilon_{ox}/t_{ox})$  is the gate oxide capacitance per unit area, where  $\varepsilon_{ox}$  and  $t_{ox}$  are the permittivity and the thickness of the oxide, respectively.

In the linear and the nonlinear regions where  $V_{DS} < V_{DS,sat}$ , the  $I_D$  is described as:

$$I_D = \frac{Z}{L_{CH}} \mu_{n,CH} C_{ox} \left\{ (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^2}{2} \right\}$$

Equation 1.36

For a n-channel MOSFET, the  $V_{TH}$  is described as:

$$V_{TH} = \phi_{MS} - \frac{Q_{ox}}{C_{ox}} + \frac{2kT}{q} \ln\left(\frac{N_A}{n_i}\right) + \frac{\sqrt{4\varepsilon_S N_A kT \ln(N_A/n_i)}}{C_{ox}}$$

Equation 1.37

where  $\phi_{MS}$  is the work function difference between the gate and the semiconductor,  $Q_{ox}$  is the fixed oxide charges per unit area,  $N_A$  is the P-type doping concentration in the n-channel, and  $\varepsilon_s$  is the permittivity of the semiconductor. For Equation 1.37,  $dV_{TH}/dT < 0$  for n channels [72].

#### 1.4 An Introduction to Relevant IGBT Basics

#### 1.4.1 High Voltage IGBT Structures

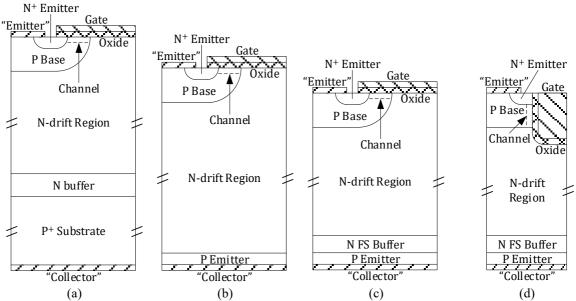

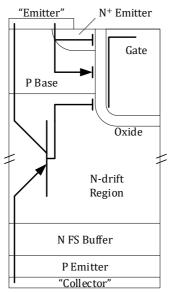

High voltage IGBTs are mostly vertical n-channel devices. Schematic diagrams of a few representative 2D vertical n-channel IGBT structures are shown in Figure 1.9. A n-channel IGBT is an integration of a n-channel MOSFET and a PNP BJT, where the MOS channel current functions as the base current of the PNP BJT structure, Figure 1.10. Compared with a vertical n-channel MOSFET, a n-channel IGBT has a P emitter layer or a P<sup>+</sup> substrate as the P emitter on the backside. This integration forms a PNPN structure.

Unlike the PNPN structure in a thyristor, in an IGBT to avoid the latch-up of the PNP and NPN BJTs in the PNPN structure, the NPN BJT is suppressed first by shorting its P-base and N-emitter with the "emitter" metallisation of the IGBT. Also, that P-base is small and heavily doped to avoid an excessive voltage across it that would activate the P-base/N-emitter junction of the NPN BJT in normal operation. These methods ensure that an IGBT is fully controllable by its MOS gate in normal operation.

In this thesis when referring to IGBTs, the term "P emitter" and its variants refer to the P emitter of the PNP BJT structure in a n-channel IGBT on the backside. Also, the term "N base" and its variants refer to the thick N base of the PNP BJT structure, which for an FS IGBT includes the N-drift region and the N FS buffer.

Some early n-channel IGBTs were fabricated on thick and heavily doped P<sup>+</sup> substrates. This P<sup>+</sup> substrate as the P emitter has very high injection efficiency which requires a heavily

Figure 1.9: Schematic diagrams of basic vertical n-channel IGBTs: (a) a planar PT IGBT, (b) a planar NPT IGBT, (c) a planar FS IGBT, and (d) a trench FS IGBT.

Figure 1.10: Schematic diagrams of a basic vertical n-channel trench FS IGBT.

doped N<sup>+</sup> buffer layer, Figure 1.9 (a), and carrier lifetime control to achieve usable switching speeds. In a forward-blocking off-state at high collector terminal to emitter terminal voltage  $V_{CE}$ , the N-drift region to P base junction is reverse-biased, and the electric field in the depletion region can punch through the N-drift region and is stopped in the N<sup>+</sup> buffer, resulting in a quadrilateral (1D, vertical) distribution of the electric field in the N base. IGBTs of this type are commonly referred to as Punch-Through (PT) IGBTs.

Later, the maturing of thin wafer technologies enabled the fabrication of n-channel IGBTs without P<sup>+</sup> substrates. The resulting IGBT has a thin P emitter with low injection efficiency, which no longer requires a N<sup>+</sup> buffer, Figure 1.9 (b), or carrier lifetime control for practical use. In a forward-blocking off-state, the N-drift region to P base junction is reverse-biased, and the electric field in the depletion region is designed to not punch through the N-drift region and reach the vicinity of the P emitter. IGBTs of this type are commonly referred to as Non-Punch-Through (NPT) IGBTs.

Advancing from NPT IGBTs, to reduce the thickness of the N-drift region, a lightly doped N buffer layer is implemented, Figure 1.9 (c), to achieve a quadrilateral (1D, vertical) distribution of the electric field in the depletion region in the N base at high forward-blocking  $V_{CE}$  in an off-state. This N buffer layer is designed to stop the electric field from reaching the vicinity of the P emitter without significantly reducing the injection efficiency of the P emitter [59], [60]. This lightly doped N buffer layer is often referred to as a Field-Stop (FS) layer, and IGBTs of this type are often referred to as Field-Stop (FS) IGBTs.

A comparison of the key features of the three aforementioned mainstream IGBT design concepts is shown in Table 1.1 [59]. Other commercial IGBTs that are based on essentially the same key design concept of Field-Stop IGBTs, e.g. Soft Punch-Through and Light Punch-Through IGBTs, will not be discussed separately.

Table 1.1: Comparison of key features of mainstream IGBT design concepts. © 2017 IEEE

|             | P emitter                                                      | N drift | N buffer | Carrier lifetimes                        |

|-------------|----------------------------------------------------------------|---------|----------|------------------------------------------|

| PT<br>IGBT  | Thick P <sup>+</sup> substrate, very high injection efficiency | Thin    |          | Low, by carrier lifetime control         |

| NPT<br>IGBT | Thin, low injection efficiency                                 | Medium  |          | High, no global carrier lifetime control |

| FS<br>IGBT  | Thin, low injection efficiency                                 | Thin    |          | High, no global carrier lifetime control |

In a modern FS IGBT, the doping concentration of the N FS buffer is often about one to two orders of magnitude lower than that of the P emitter [73]–[75]. As a result, the N FS buffer is also under high-level injection in a typical on-state, where the N FS buffer can be considered as part of the N base of the PNP BJT structure alongside the N-drift region.

Regarding the MOS gate structure of FS IGBTs, a trench MOS gate, Figure 1.9 (d), provides direct access to the N base for the electrons through the vertical MOS channel, compared with a planar MOS gate. This avoids the depletion region formed by the reverse-biased N-drift region to P base junction under a forward  $V_{CE}$ . Consequently, the reduced crowding and path length of the electrons out of the MOS channel in the MOS gate area improve the MOS channel density and the on-state performance.

#### 1.4.2 Basic IGBT Operations

A basic FS IGBT only has practical forwarding blocking capability due to the N FS buffer and is normally operated with a Free-Wheeling Diode (FWD) in anti-parallel, which enables reverse current conducting and prevents excessive reverse voltage for the IGBT. At a high forward  $V_{CE}$ , the N-drift region to P base junction is reverse-biased. As previously discussed and illustrated in Figure 1.2 (b), a high forward  $V_{CE}$  is supported by a depletion region distributed mostly in the N-drift region.

Some early FS IGBTs were designed with a N-drift region of a very low doping concentration to reduce the thickness of the N-drift region and the operating losses. Such a design results in a low static punch-through voltage  $V_{PT}$ , where the  $V_{PT}$  refers to the forward static off-state  $V_{CE}$  when the depletion edge in the N base just reaches the N buffer. However, a major issue of such a low  $V_{PT}$  design is that the FS IGBT is more likely to be subject to oscillation at fast turn-off due to lack of high-level excess carriers after the depletion region reaches the N buffer [73]–[75]. Later generations of FS IGBTs greatly mitigated this issue by increasing the thickness and the doping concentration of the N-drift region to raise the  $V_{PT}$  above the typical utilisation of the  $V_{CE}$  rating in practice. This situation is assumed in this thesis.

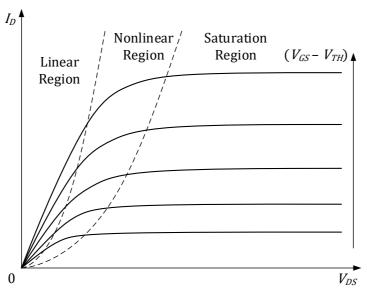

The typical DC I-V characteristics of a n-channel IGBT resemble those of a n-channel power MOSFET, with the differences resulting from the P emitter of the PNP BJT structure in the IGBT. In a n-channel IGBT, when the gate-emitter voltage  $V_{GE}$  exceeds the threshold voltage  $V_{TH}$ , an inversion layer of electrons is formed in the P base adjacent to the gate oxide. With a positive  $V_{CE}$  and the P emitter to N FS buffer junction forward-biased, electrons from the N<sup>+</sup> emitter flow through a MOS channel in the P base formed by that inversion layer and into the N-drift region.

In a typical IGBT on-state, this electron current functions as the base current of the PNP BJT structure and induces a hole injection current from the P emitter through the N FS buffer and into the N-drift region. With a sufficient ( $V_{GE} - V_{TH}$ ) for the voltage across the MOS channel, the MOS channel is in its linear region, and the resulting ambipolar current components in the N-drift region lead to high-level injection and conductivity modulation in it. As  $p \approx n$  under high-level injection and due to the higher mobility of the electrons, the electron current via the MOS channel accounts for a higher proportion of the ambipolar current in the N-drift region.

The hole current in the N-drift region flows into the P base at the frontside and to the "emitter" terminal. Meanwhile, the electrons in the N-drift region flows into the P emitter, where the electrons diffuse into the P emitter with the electron concentration decreasing due to recombination. This operation region of an IGBT, often referred to as the saturation region in Figure 1.11, resembles the linear region of operation of a power MOSFET.

In static or quasi-static situations, when the  $(V_{GE} - V_{TH})$  is inadequate for the voltage across the MOS channel, the MOS channel pinches off and the MOS channel current saturates with the  $V_{CE}$ . Since this MOS channel current functions as the base current of the equivalent PNP BJT with a very thick N base typically under high-level injection, the induced hole injection current from the P emitter also tends to saturate with the  $V_{CE}$ . Hence, the IGBT collector terminal current  $I_C$  exhibits saturation characteristics against the  $V_{CE}$ . Determined by the MOS gate structure, the  $I_C$  under channel pinch-off conditions is related to  $(V_{GE} - V_{TH})^2$ . With a sufficient  $I_C$  that results in high-level injection in the undepleted part of the N base, the saturated IGBT  $I_C$  can be approximated by [76]:

$$I_{C,sat} \approx \frac{I_{MOS}}{1 - \alpha_{PNP}} \propto \{C_{ox}(V_{GE} - V_{TH})^2\}$$

Equation 1.38

where  $I_{MOS}$  is the MOS channel current,  $\alpha_{PNP}$  is the common-base current gain of the PNP BJT structure, and  $C_{ox}$  is the gate oxide capacitance per unit area. This operation regime is often referred to as the  $V_{GE}$  controlled active region in Figure 1.11, and the transition region between this active region and the saturation region is often referred to as the quasi-saturation region.

Figure 1.11: Schematic diagram of DC *I-V* characteristics of a n-channel IGBT.

The carrier transport in the IGBT N base in the transient of a fast turn-off from a typical on-state has an additional degree of freedom contributed by the high-level excess carriers. Detailed IGBT turn-off process will be discussed later.

#### 1.4.3 High-level Injection and Ambipolar Carrier Transport

IGBTs are designed to achieve high-level injection in the N base from low current densities [76]. Under high-level injection, the concentrations of both types of carriers exceed the doping concentration. Carriers of each type attract carriers of the complementary type. The drift of electrons and holes is coupled by the same electric field [76]. As a result, the electron concentration is approximately equal to the hole concentration. In the regions under high-level injection, the electric field is referred to as the ambipolar electric field  $E_A$  and is responsible for the carrier transport and the quasi-neutrality of the net charges,  $p \approx n$  [77]–[81]. The carrier transport under high-level injection is often referred to as ambipolar carrier transport, which is significantly different from the carrier transport in signal BJTs.

For the N base in a high voltage IGBT, the discussion of the carrier transport under high-level injection can be reduced to 1D situations [76]. From Equation 1.26 and Equation 1.27, the electron current  $I_n$  and the hole current  $I_p$  are described as:

$$I_n = qnA(\mu_n E) + qAD_n \frac{\partial n}{\partial x} = qnA(\mu_n E) + qA\left(\frac{kT}{q}\mu_n\right)\frac{\partial n}{\partial x}$$

Equation 1.39

$$I_{p} = qpA(\mu_{p}E) - qAD_{p}\frac{\partial p}{\partial x} = qpA(\mu_{p}E) - qA\left(\frac{kT}{q}\mu_{p}\right)\frac{\partial p}{\partial x}$$

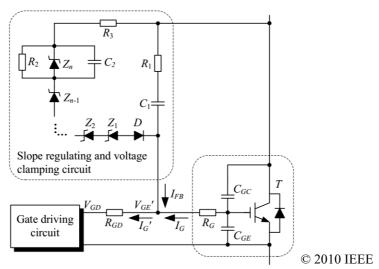

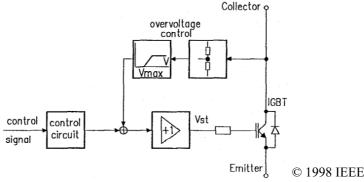

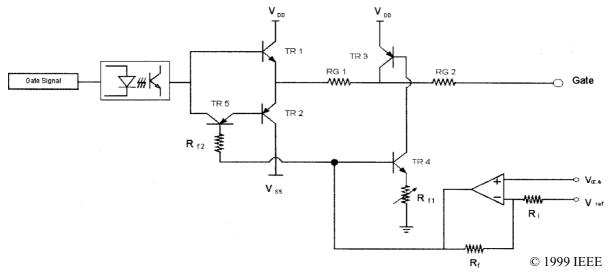

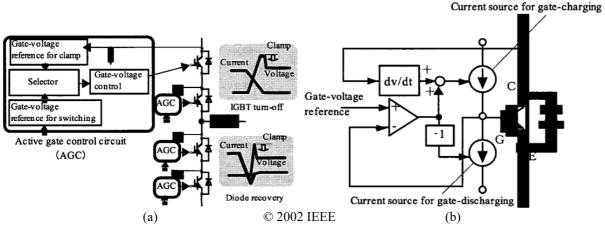

Equation 1.40