# Structure and Optimisation of Liquid Crystal based Phase Shifter for Millimetre-wave Applications

### Jinfeng Li

Wolfson College, Cambridge

This dissertation is submitted for the degree of

Doctor of Philosophy

Under the supervision of

Prof. Daping Chu

### **DEPARTMENT OF ENGINEERING**

UNIVERSITY OF CAMBRIDGE

June 2018

**Declaration of Originality and Statement of Length**

I hereby declare that except where specific reference is made to the work of others, the contents

of this dissertation are original and have not been submitted in whole or in part for consideration

for any other degree or qualification in this, or any other University.

This dissertation is the result of my own work and includes nothing which is the outcome of

work done in collaboration, except where specifically indicated in the text.

This dissertation contains less than 65,000 words including appendices, bibliography, footnotes,

tables and equations and has less than 150 Figs.

Jinfeng Li

11<sup>th</sup> June. 2018

Sinfens a

Acknowledgement

First and foremost, I express my sincere gratitude to my supervisor Prof. Daping Chu, who

guides me in the field of liquid crystal based millimetre-wave devices, from fundamental

studies to device fabrication and characterisation. Deeply influenced by him, I have created my

love of research and my desire to contribute to human knowledge. With his support, I have

gained significant research experience in GHz low-loss tunable dielectrics and phase element

applications based on in-depth understanding of material properties and device physics. I have

developed hands-on computational electromagnetics skills, and applied appropriate research

methodologies, tools and techniques for the design and optimisation of millimetre-wave devices.

I have enhanced my capability of critically analyzing and evaluating findings and results for

knowledge contribution with much attention to details from simulation to fabrication.

Specifically, the participation in the Variable Dielectric Delay Lines in Liquid Crystals for

Phased Array Feeds project in collaboration with Cambridge Astrophysics Group has

developed my commitment to doing research that challenges the conventional thinking and

strengthened my life-long aspiration to engage in academic research.

I extend my appreciation to my doctoral advisor and other postdoctoral research associates of

diverse backgrounds in our group (Centre for Photonic Devices and Sensors) for their

continuous suggestions and feedback on my research. Most especially, I would like to thank

Kasia for the cleanroom training.

I acknowledge the Cambridge Commonwealth, European & International Trust for sponsoring

my PhD study and maintenance. I appreciate the Department of Engineering and Wolfson

College for supporting me with grants to attend the 46th European Microwave Conference

(EuMC), during which I interacted with leaders in the field of microwave and millimetre-wave

engineering. I wish to thank my college Tutor Dr Shadia Taha for her help in Wolfson College.

I appreciate the useful comments from Dr Tim Coombs and Dr Anibal Fernandez as my viva

examiners. Finally, I dedicate this work to my wife and my parents for their love.

Sinfens (

11<sup>th</sup> June. 2018

### **Abstract**

The delivery of tunable millimetre-wave components at 60GHz is of research and development interests with the advent of 5G era. Among applications such as high-data-rate wireless communications, high-precision automotive radars and hand-gesture sensing, variable phase shifters are vital components for antenna arrays to steer an electromagnetic beam without mechanical movement. However, present microwave technology has limited scope in meeting more and more stringent requirements in wavefront phase control and device performance for those cutting-edge applications in the millimetre-wavelength range. Although some existing microwave switchable techniques (such as RF MEMS and solid-state p-i-n diodes) can offer ultra-fast speed for phase modulation, their binary beam-steering nature is resolution-limited and thereby degrades the beam-scanning performance. In response to this, continuously-tunable phase shifting can be realised by using tunable dielectric materials such as ferroelectric BST and liquid crystals (LCs). BST thin films can offer relatively fast switching and modest tunability. However, the increased dielectric loss beyond 10GHz impedes their implementation for higher frequency applications. By comparison, liquid crystals (LCs) have drawn attention in recent years because of their continuous tunability as well as low losses especially at millimetre-wavebands. The principle of shifting the phase continuously is based on the shape anisotropy of LC molecules for variable polarizabilities and hence tunable dielectric constants, which allows wave speed to be controlled with ease by a low-frequency field of only up to 10V. However, LC-based tunable delay lines are not well established in the frequency regime of 60GHz-90GHz because of the limited status of LC microwave technology in which most of the LC based devices have been designed for below 40GHz. It is the aim of this PhD research to bridge the gap and address future societal needs based on our group's focus and experience in developing cutting-edge LC-based agile microwave components.

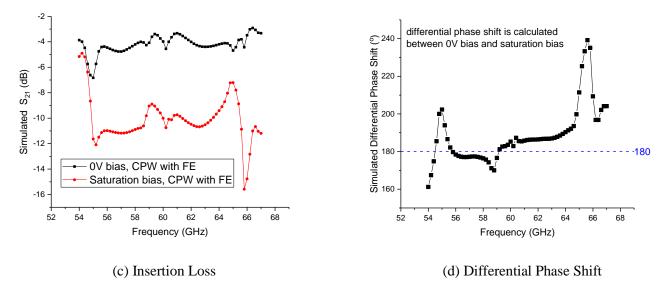

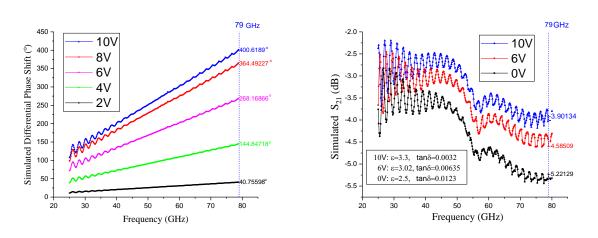

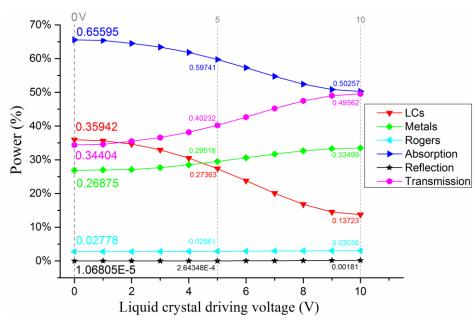

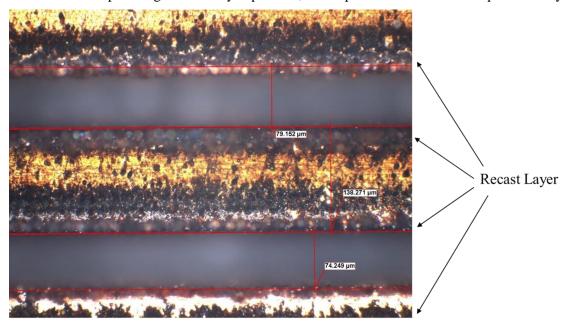

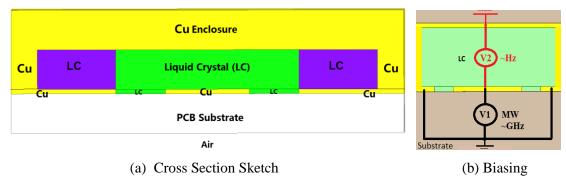

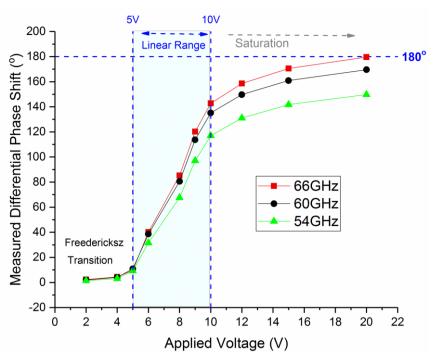

In this work, a liquid crystal (LC) based 0-180° continuously-variable phase shifter is developed with insertion loss less than -4.4dB and return loss below -15dB across a wide spectrum from 54GHz to 67GHz. The device is driven by a 0-10V AC bias and structured in a novel enclosed coplanar waveguide (ECPW) including an enclosed ground plate in the design, which significantly reduces the instability due to floating effects of the transmission line. This structure screens out interference and stray modes, allowing resonance-free quasi-TEM wave

I

propagation up to 90GHz. The tunable ECPW is optimised by competing spatial volume distribution of the millimetre-wave signal occupying lossy tunable dielectrics versus low-loss but non-tunable dielectrics and minimising the total of dielectric volumetric loss and metal surface loss for a fixed phase-tuning range. A variety of influences affecting the actual device performance are studied, experimented and optimised. Fabricated prototypes exhibit wideband low-loss performance and  $0-\pi$  continuous tuning with low power consumptions and high linearity compared with the state-of-the-arts. Potentially, the ECPW-fed phased antenna array will be incorporated with advanced beam-forming algorithms to develop compact beam-steering systems of improved performances and targeted for ultra-high-data-rate wireless communications, inter-satellite communications, current road safety improvement, futuristic autonomous driving, and other smart devices such as the hand-gesture recognition.

### **Table of Contents**

| Abstrac | t     |                                                                            | I  |

|---------|-------|----------------------------------------------------------------------------|----|

| Chapter | 1. Mi | llimetre-wave Beam Steering Applications and Technologies                  | 1  |

| 1.1     | 6     | 0 GHz – 90 GHz Opportunities                                               | 1  |

|         | 1.1.1 | Fifth Generation (5G) Mobile Communications (57GHz-66GHz)                  | 1  |

|         | 1.1.2 | Inter-satellite Communications (60GHz)                                     | 3  |

|         | 1.1.3 | Automotive Radar (76GHz-81GHz)                                             | 3  |

|         | 1.1.4 | Gesture Sensing (60GHz)                                                    | 5  |

| 1.2     | N     | Millimetre-wave Beaming Steering Technologies                              | 7  |

|         | 1.2.1 | Conventional Beam Scanning by Mechanically Rotating                        | 7  |

|         | 1.2.2 | Electrically Steerable Phased Array Antenna                                | 7  |

|         | 1.2.3 | Phase Shifting Devices as Key Components in a Phased Array System          | 10 |

| 1.3     | S     | Survey of Current Millimetre-wave Phase Shifters and Their Limitations     | 12 |

|         | 1.3.1 | Ferrites                                                                   | 12 |

|         | 1.3.2 | p-i-n diodes, Varactors                                                    | 12 |

|         | 1.3.3 | MEMS                                                                       | 13 |

|         | 1.3.4 | Tunable Dielectrics Methods                                                | 14 |

| 1.4     | E     | exploring Liquid Crystal based Phase Shifters for 60GHz-90GHz Applications | 17 |

|         | 1.4.1 | Ferroelectric Barium Strontium Titanate (BST)                              | 17 |

|         | 1.4.2 | LC's Advantages over BST for Millimetre-wave Applications                  | 17 |

|         | 1.4.3 | Limitations of Nematic Liquid Crystal                                      | 19 |

| -       |       | ferent Approaches of Phase Shifter Configurations with LC above            | 21 |

| 2.1     | Princ | iple of Liquid Crystal based Phase Tuning Components                       | 21 |

|         | 2.1.1 | LC Dielectric Anisotropy due to Molecular Shape Anisotropy                 | 21 |

|         | 2.1.2 | Elements of Electrically-Tuned LC Phase-Shifting Architecture              | 23 |

|         | 2.1.3 | Planar Alignment by Surface Anchoring                                      | 25 |

| 2.2     | Chall | enges in LC-based Phase Shifters at Millimtre-wave                         | 27 |

|         | 2.2.1 | Transmission Line Effects and Characteristics of Various Line Structures   | 27 |

|         | 2.2.2 | Line Loss due to Standing-wave Resonance and Parasitic Mode Radiation      | 28 |

|         | 2.2.3 | Line Loss due to Metal Surface Roughness and Skin Effect                   | 28 |

|         | 2.2.4 | Line Loss due to Substrate's Thermal Properties                            | 30 |

|       |      | 2.2.5 | Manufacturing Tolerance                                               | 30    |

|-------|------|-------|-----------------------------------------------------------------------|-------|

|       | 2.3  | Wave  | guide and Substrate Integrated Waveguide Methods                      | 32    |

|       | 2.4  | Tradi | tional Transmission Line Method                                       | 33    |

|       |      | 2.4.1 | LC-filled Phase Shifters based on Coaxial and Stripline Structures    | 33    |

|       |      | 2.4.2 | LC-based Inverted Microstrip Line (IMSL) vs. Coplanar Waveguide       | 35    |

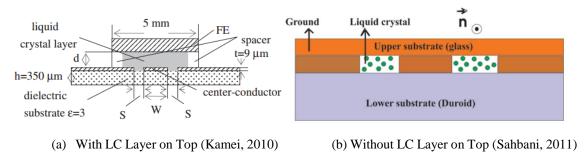

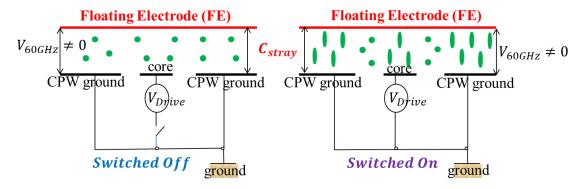

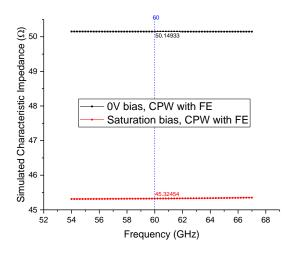

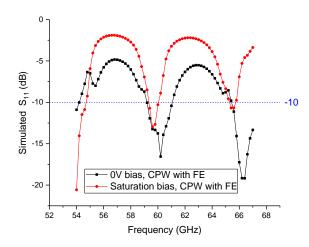

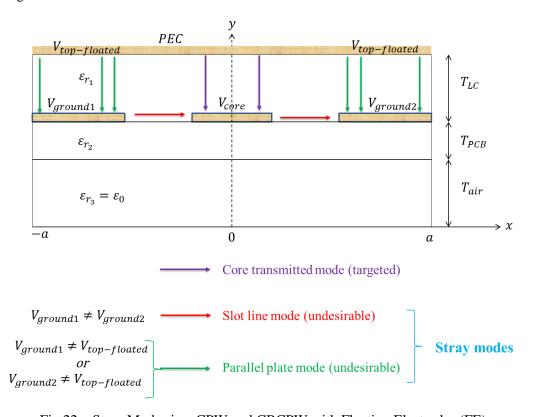

|       |      | 2.4.3 | LC-based Traditional CPW with Top-floated Electrode (FE CPW)          | 39    |

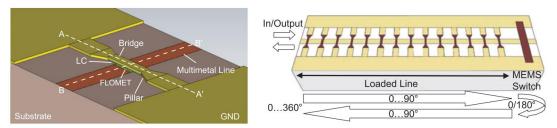

|       |      | 2.4.4 | LC-based Traditional CPW with MEMS Switches                           | 43    |

|       | 2.5  | Propo | osed CPW with no Floating Electrodes (FE-free CPW)                    | 44    |

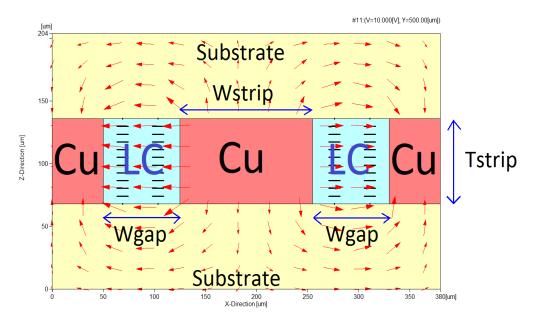

|       |      | 2.5.1 | Floating Electrode Free CPW Structure (FE-free CPW)                   | 44    |

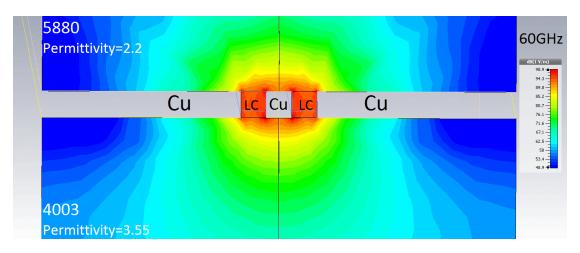

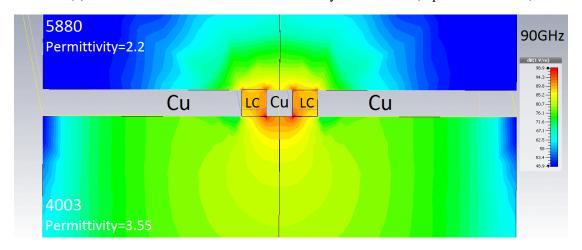

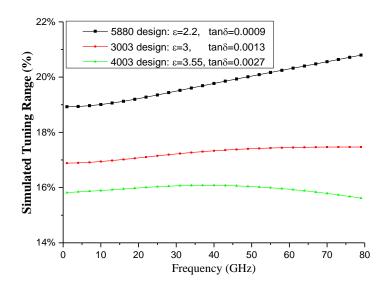

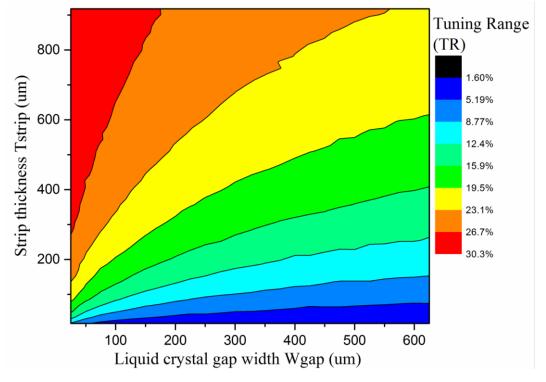

|       |      | 2.5.2 | Tuning Range Study and Impact of Substrate Materials                  | 45    |

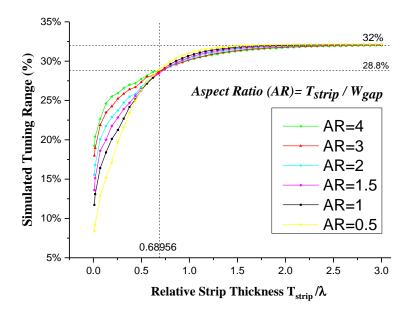

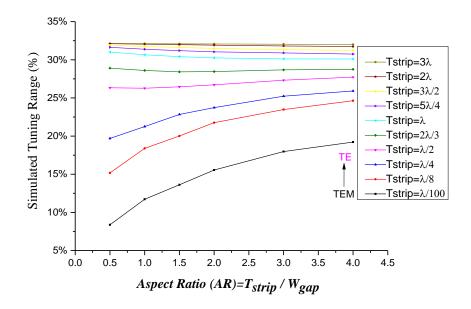

|       |      | 2.5.3 | Aspect Ratio Effect on Modes and Tuning Range                         | 47    |

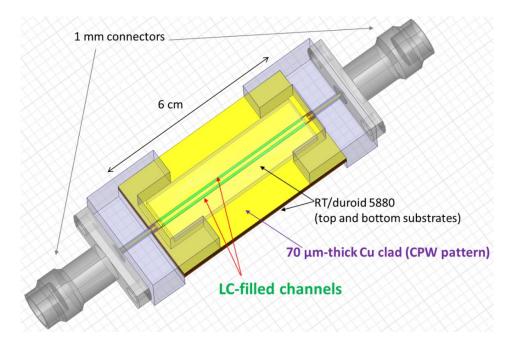

|       |      | 2.5.4 | Performance Analysis by Simulation                                    | 49    |

|       |      | 2.5.5 | Challenges in Heavy-Cu Patterning and Alignment inside                | 51    |

|       |      | 2.5.6 | Limitations of the Proposed LC-based FE-free CPW                      | 52    |

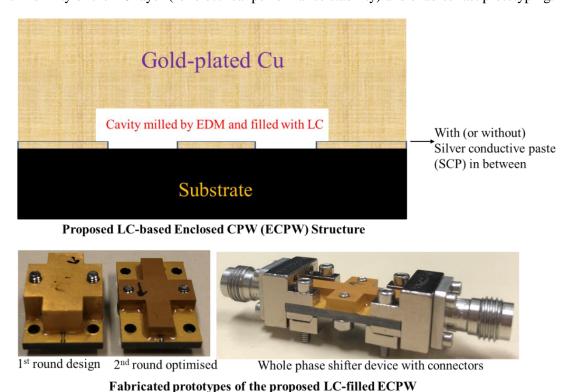

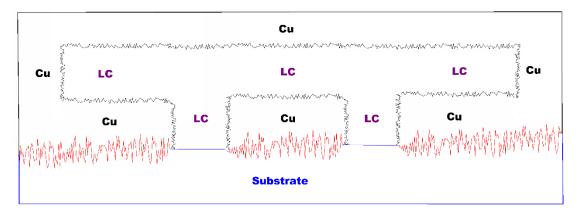

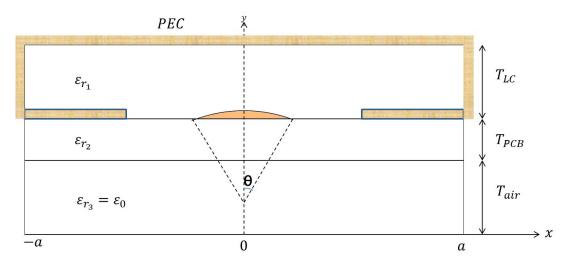

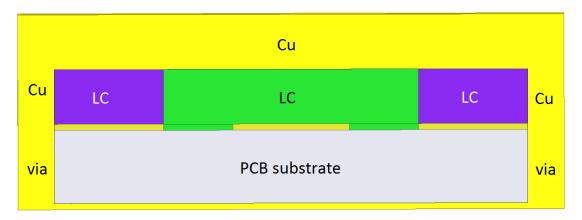

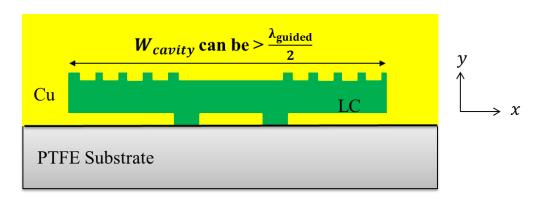

|       | 2.6  | Propo | osed Enclosed Coplanar Waveguide (ECPW) Method                        | 54    |

|       |      | 2.6.1 | LC-based Enclosed Coplanar Waveguide (ECPW)                           | 54    |

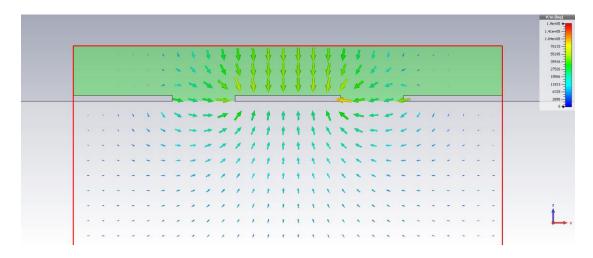

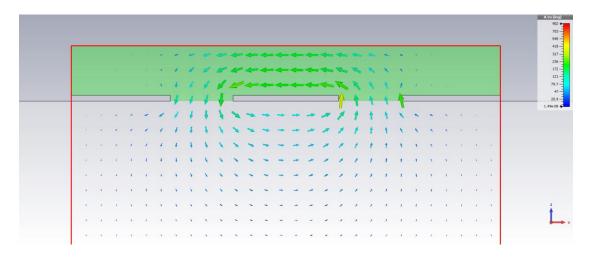

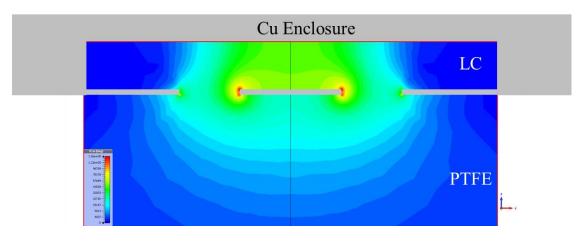

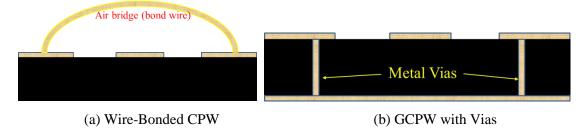

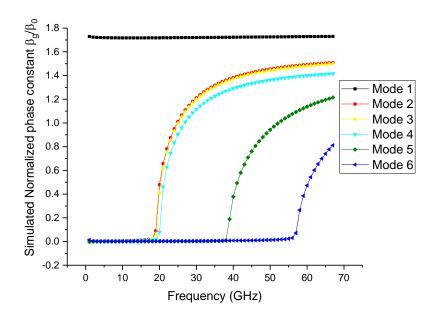

|       |      | 2.6.2 | Connectivity between the Top Conductor and the Coplanar Ground Planes | 56    |

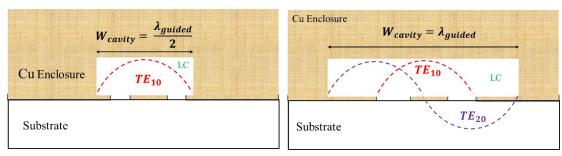

|       |      | 2.6.3 | Upper Frequency Limit of a Single ECPW Mode Operation                 | 58    |

|       | pter |       | Computational Electromagnetics for LC-based Enclosed CPW (ECPV        |       |

| at 60 | 0GE  |       |                                                                       |       |

|       | 3.1  |       | mission Line Computation Approaches and Assumptions                   |       |

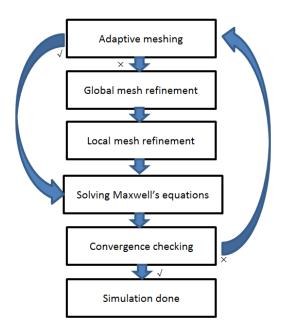

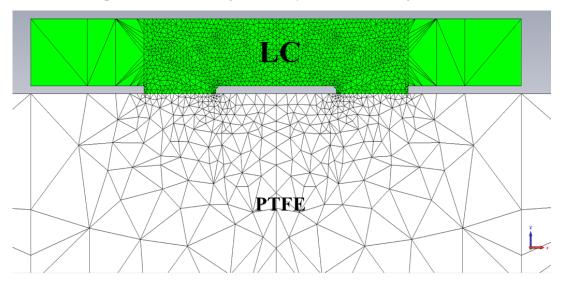

|       | 3.2  | Num   | erical Approaches and Adaptive Meshing                                | 62    |

|       |      | 3.2.1 | Full-wave Approach based on Field Theory                              | 62    |

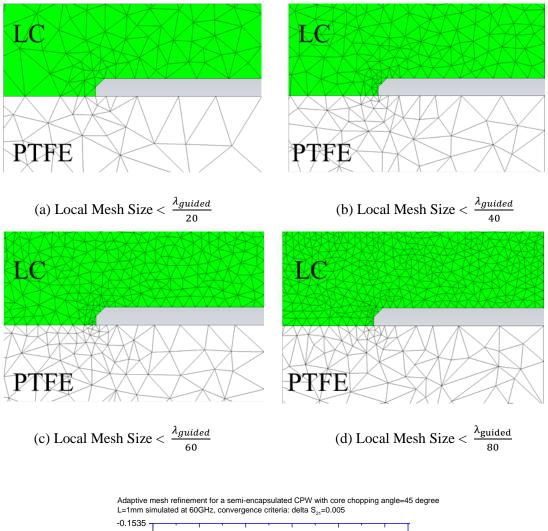

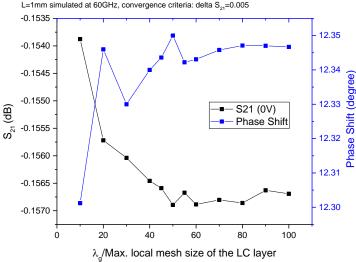

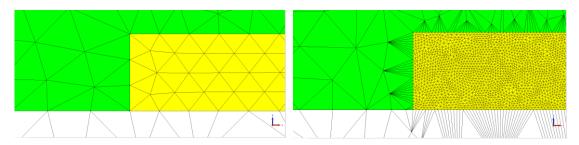

|       |      | 3.2.2 | Adaptive Meshing inside Dielectrics                                   | 63    |

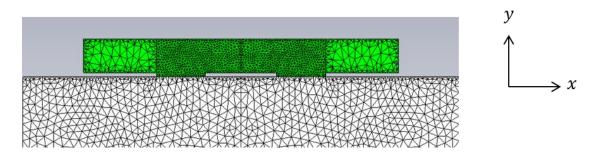

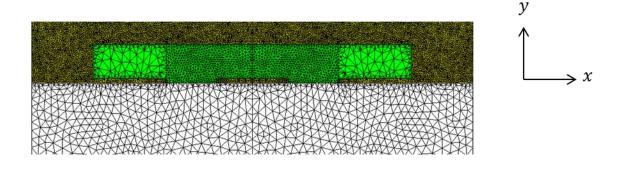

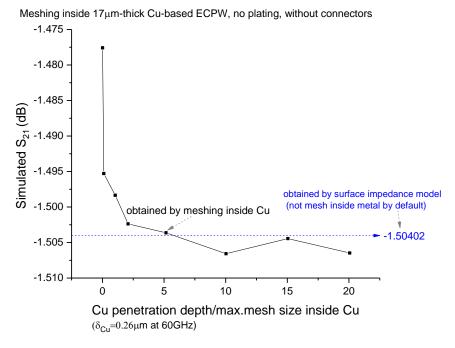

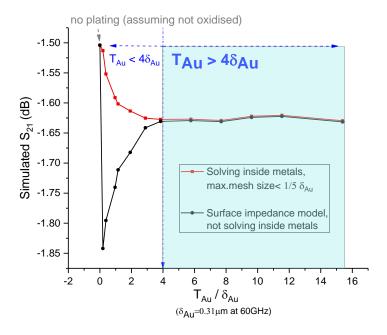

|       |      | 3.2.3 | Adaptive Meshing inside Metals                                        | 66    |

|       | 3.3  | LC's  | Material Tunability with the Enclosed CPW Structure                   | 69    |

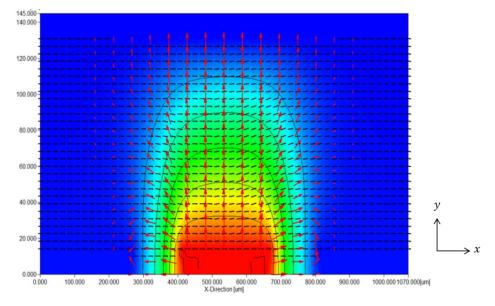

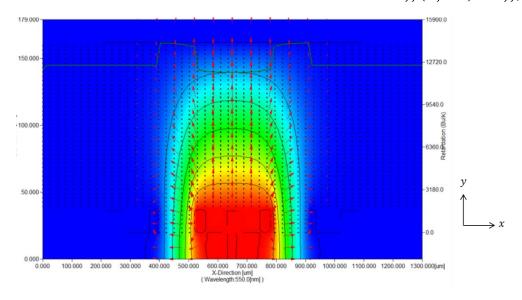

|       |      | 3.3.1 | Surface-anchoring Alignment Direction for the Maximum Tunabiltiy      | 69    |

|       |      | 3.3.2 | A Partitioning Model for Local Polarisation and Tunability Analysis   | 70    |

|       |      | 3.3.3 | LC Director Calculations based on Finite Element Simulations          | 72    |

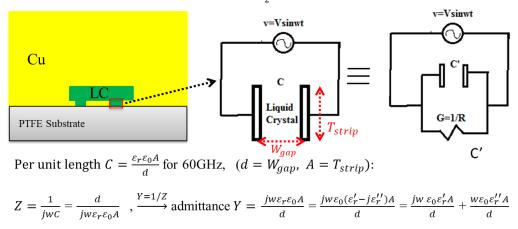

|       | 3.4  | Т     | Theoretical Modelling and Full-wave Simulation of Enclosed CPW (ECPW  | V) at |

|       | 60G  | Hz 7  | 4                                                                     |       |

|       |      | 3.4.1 | Analytical Model of the ECPW Structure                                | 74    |

|       |      | 3.4.2 | Calculation of Conductor Loss                                         | 76    |

|         | 3.4.3  | Calculation of Dielectric Loss                                                                                                | 77    |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------|-------|

|         | 3.4.4  | Optimisation in Stages                                                                                                        | 79    |

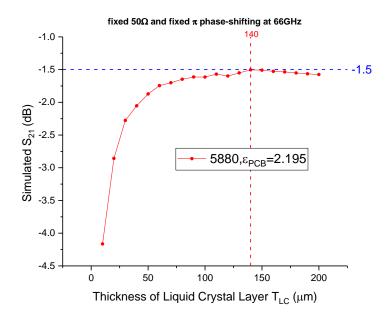

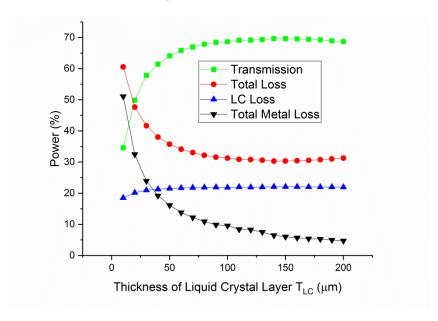

| -       |        | Cunable Part Design: Tailoring Spatial Volume and Distribution of twe Signal Occupying Tunable versus Non-tunable Dielectrics | .80   |

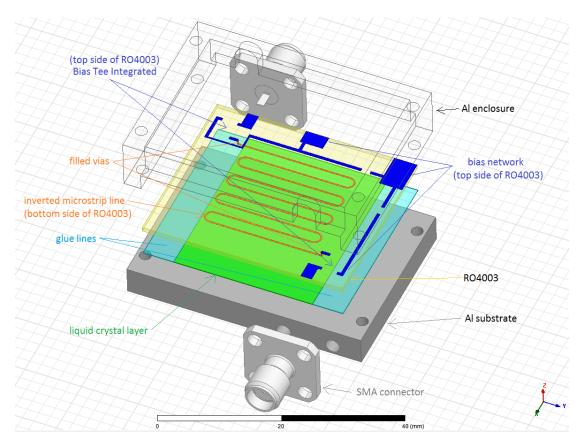

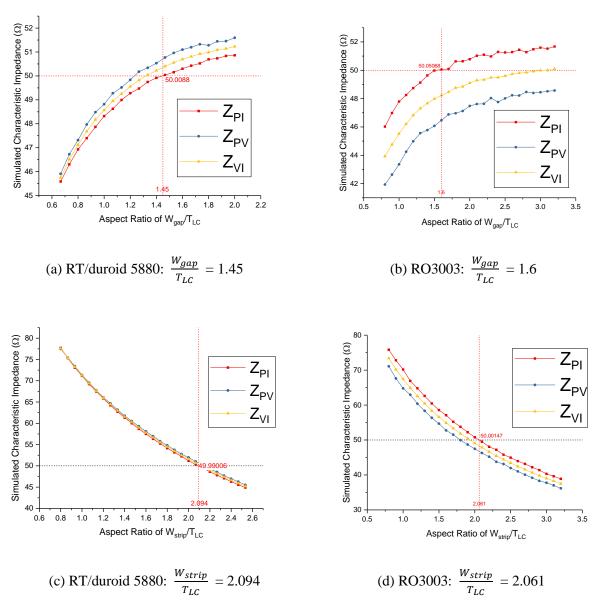

| 4.1     | Imped  | dance-Matching Scheme Targeted for a Phased Array                                                                             | 80    |

|         | 4.1.1  | Novel Biasing-voltage Dependent Wideband Impedance-Matching                                                                   | 80    |

|         | 4.1.2  | ECPW's Geometrical Aspect Ratios for 50Ω Controlled Impedance                                                                 | 80    |

| 4.2     | Nonli  | nearities in Tuning Range and Insertion Loss                                                                                  | 82    |

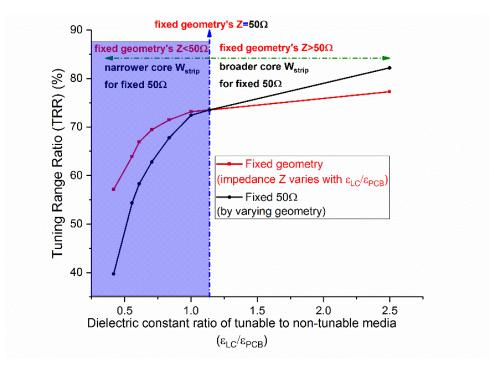

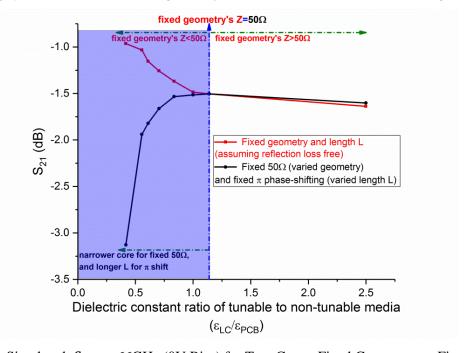

|         | 4.2.1  | Definition of wave-occupied-volume ratio and tuning range ratio (TRR)                                                         | 82    |

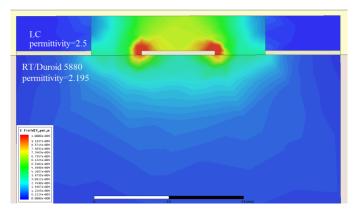

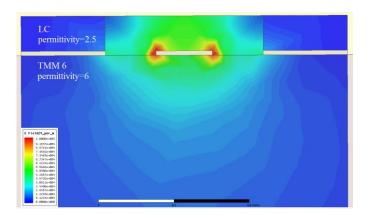

|         | 4.2.2  | Fixed LC-layer Thickness: Compute $TRR$ Parametrised with $\varepsilon LC / \varepsilon PCB$                                  | for   |

|         | Fixed  | Geometry (Varied Impedance) vs. Fixed Impedance (Varied Geometry)                                                             | 83    |

|         | 4.2.3  | Optimising LC-layer Thickness by Balancing TRR and the Minimum Sun                                                            | ı of  |

|         | Condu  | actor and Dielectric Losses                                                                                                   | 84    |

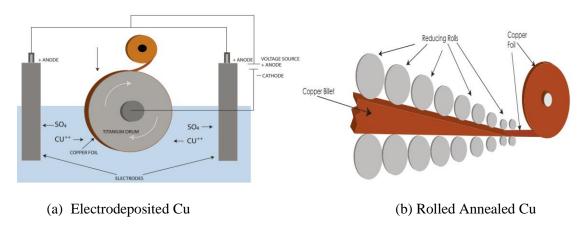

| 4.3     | Low-   | loss PCB Substrates and Cu Foil Investigation at 60GHz                                                                        | 88    |

|         | 4.3.1  | Mismatch in Coefficient of Thermal Expansion (CTE) and Post-etch Stress Ro                                                    | elief |

|         |        |                                                                                                                               | 88    |

|         | 4.3.2  | CTE Mismatch Induced Standing Waves Resonance and Higher-order Mo                                                             | odes  |

|         | Radia  | tion                                                                                                                          | 90    |

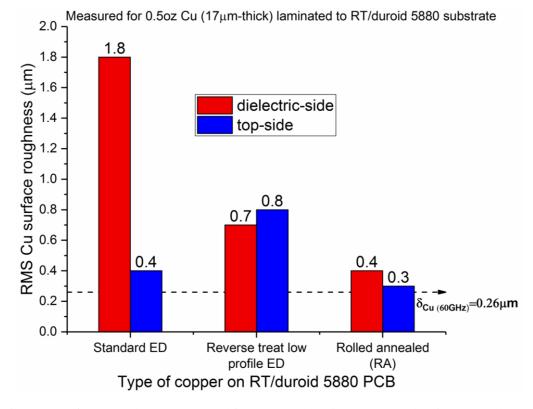

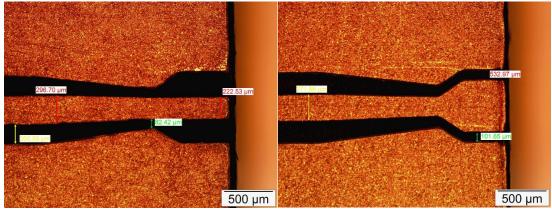

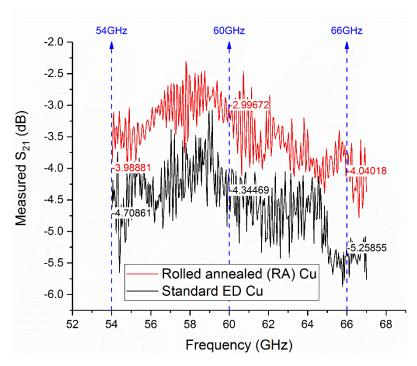

|         | 4.3.3  | Effect of Copper Surface Roughness on Insertion Loss                                                                          | 90    |

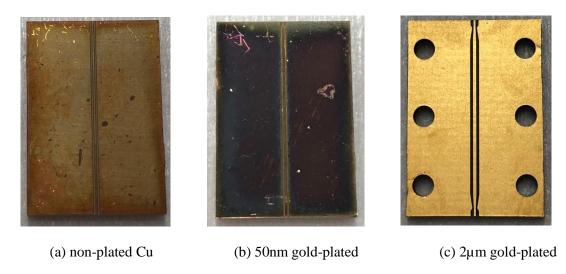

| 4.4     | Electr | rode Materials and Gold-plating                                                                                               | 93    |

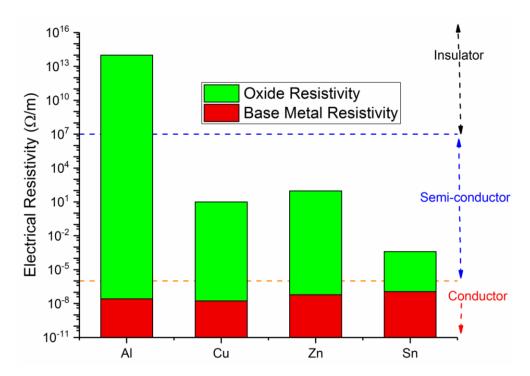

|         | 4.4.1  | Electrical Conductivity of Enclosure Materials and Oxidation                                                                  | 93    |

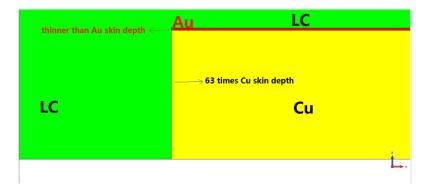

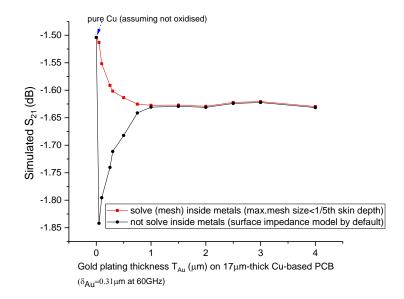

|         | 4.4.2  | Simulated Impact of Gold-plating Thickness on Insertion Loss                                                                  | 94    |

|         | 4.4.3  | Practical Consideration of Gold-plating Thickness: Cu Migration into Gold                                                     | and   |

|         | Oxida  | tion                                                                                                                          | 96    |

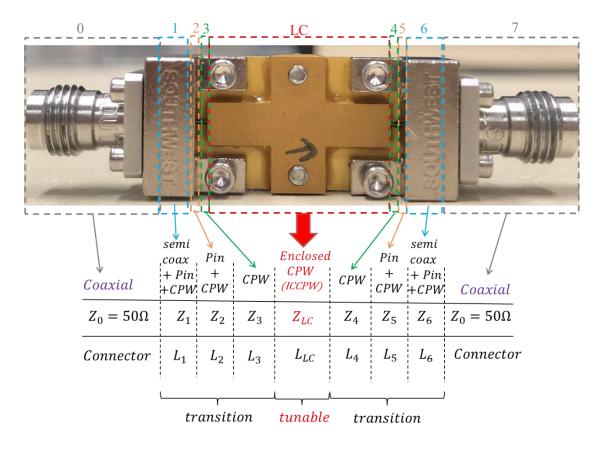

| Chapter | · 5. D | Design of Connector-to-PCB Transitions                                                                                        | .97   |

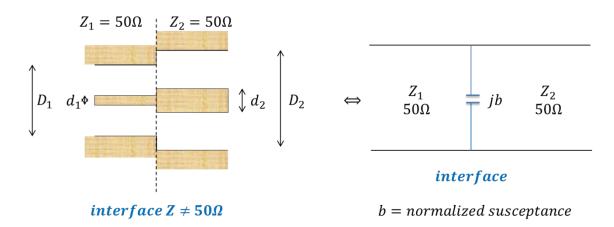

| 5.1     | Geom   | netry Discontinuity, Polarisation Transition, and Coupling                                                                    | 97    |

| 5.2     | Wide   | band Impedance-Matching Scenarios for ECPW Device                                                                             | 102   |

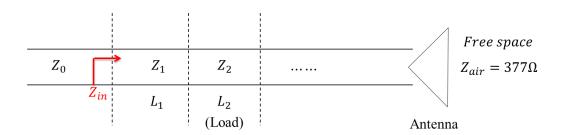

|         | 5.2.1  | Cascade of Sections with a Uniform Impedance for Symmetric Network                                                            | 102   |

|         | 5.2.2  | Coupling and Higher-order Modes                                                                                               | 103   |

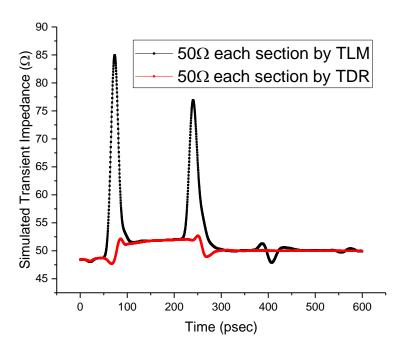

|         | 5.2.3  | Getting Knowledge of the Interface Impedance by TLM vs. TDR                                                                   | 104   |

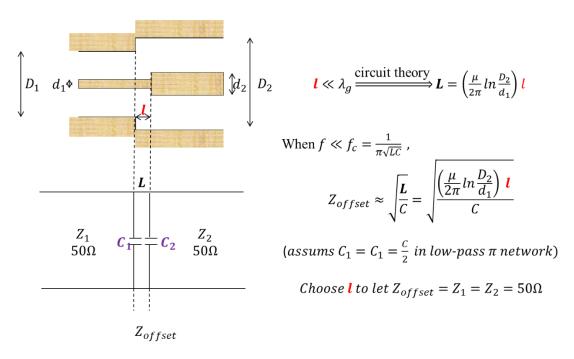

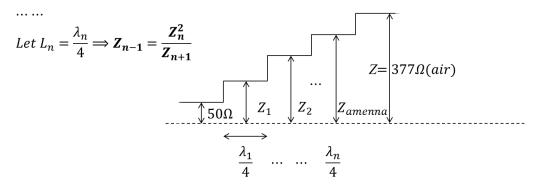

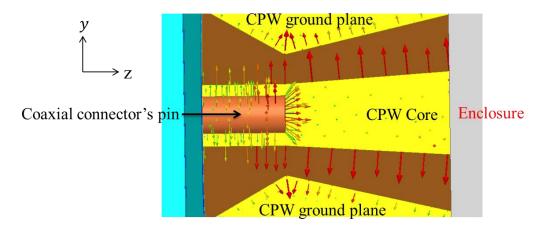

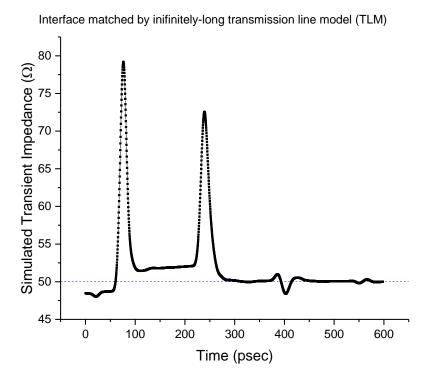

| 5.3     | 50Ω Ι  | Interface Matching based on Infinitely-long Transmission Line Model (TLM)                                                     | 105   |

| 5.4     | 50Ω ]  | Interface Matching by Time Domain Reflectometry (TDR)                                                                         | 107   |

|         | 5.4.1  | TDR Concept and Calculation Setup                                                                                             | 107   |

|         |        |                                                                                                                               |       |

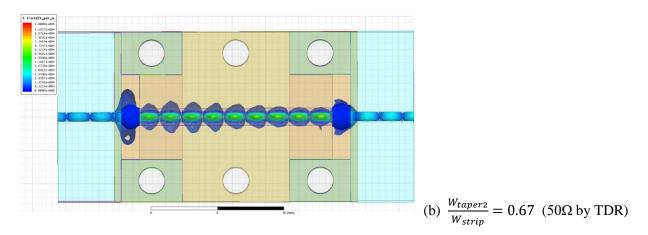

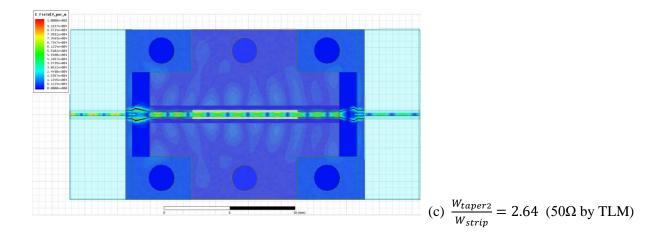

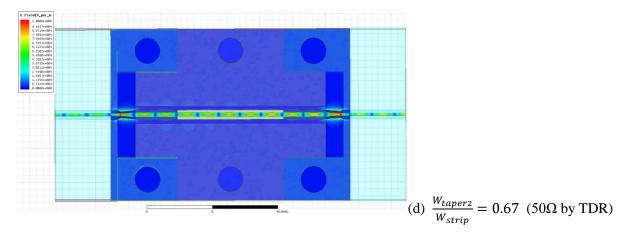

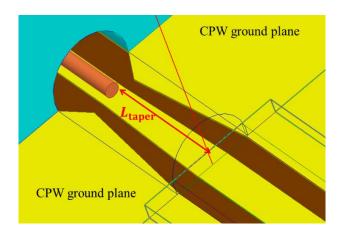

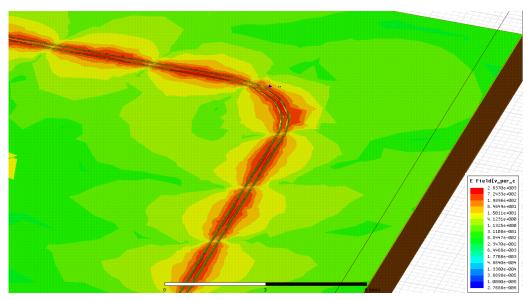

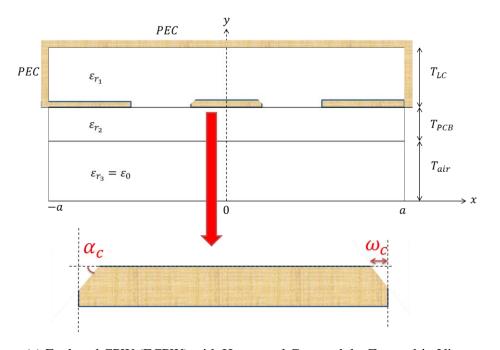

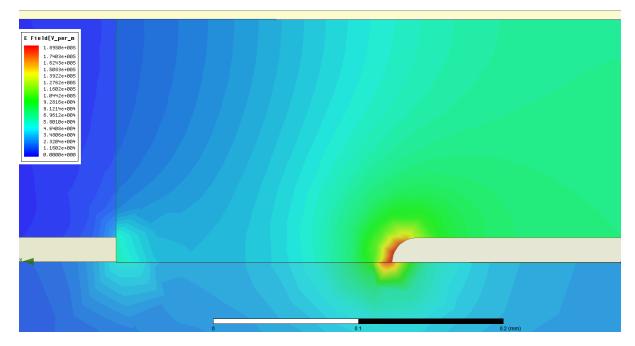

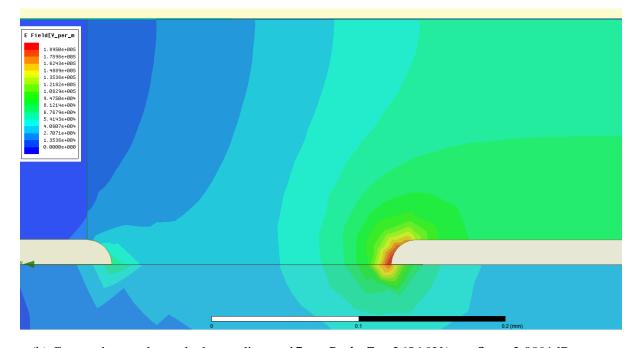

|     |      | 5.4.2    | Taper Design by TDR vs. TLM and 60GHz Electric Field 3D Visualisation .                   | 108    |

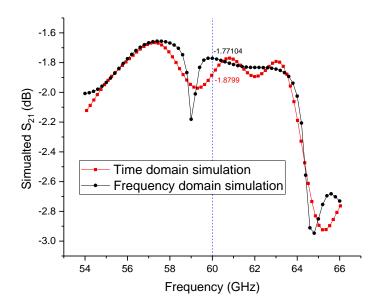

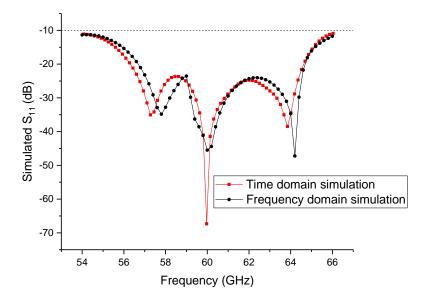

|-----|------|----------|-------------------------------------------------------------------------------------------|--------|

|     | 5.5  | Bench    | nmarking the $50\Omega$ -transition Structure Optimised by the Proposed TDR Meth          | nod in |

|     | Free | quency ! | Domain                                                                                    | 120    |

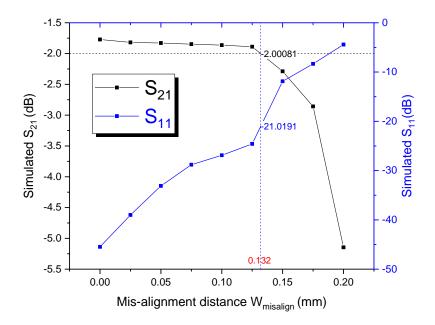

|     | 5.6  | Devic    | ee Simulation Incorporating Fabricating Tolerances                                        | 122    |

|     |      | 5.6.1    | Impact of Connector Misalignment on Insertion Loss                                        | 122    |

|     |      | 5.6.2    | Impact of Alignment Layer on Insertion Loss                                               | 123    |

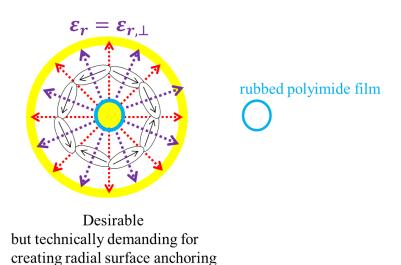

| Cha | pter | 6. D     | Device Fabrication and Experimental Setup                                                 | . 125  |

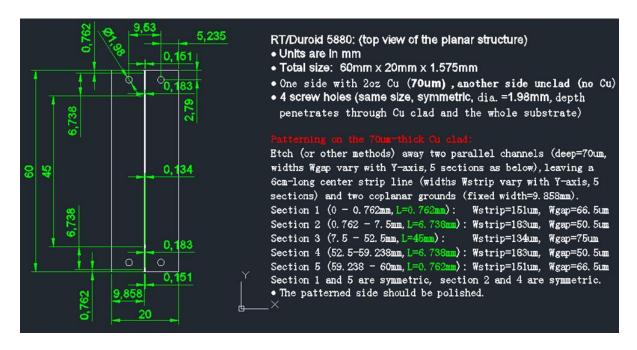

|     | 6.1  | Electr   | odes Patterning and Substrates Shaping                                                    | 125    |

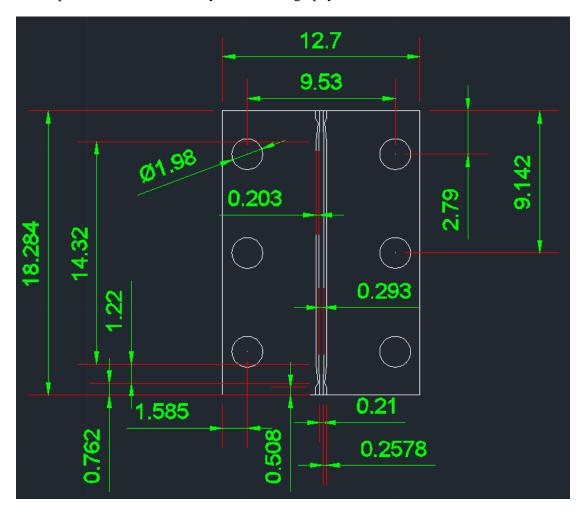

|     |      | 6.1.1    | PCB Engraving by Photolithography                                                         | 126    |

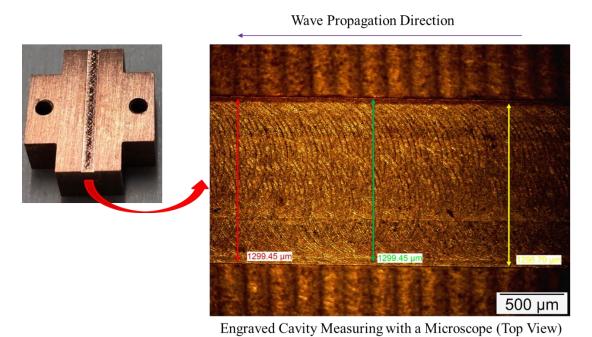

|     |      | 6.1.2    | Enclosure Machining by Wire Erosion                                                       | 129    |

|     |      | 6.1.3    | Gold-plating and Conductor's Profile Measurement                                          | 130    |

|     | 6.2  | Creat    | ing Rubbed Alignment Layers for Surface Anchoring                                         | 135    |

|     |      | 6.2.1    | Spin-coating Planar Alignment Agents                                                      | 135    |

|     |      | 6.2.2    | Rubbing Polyimide Alignment Film                                                          | 138    |

|     | 6.3  | Subst    | rates Assembling, LC-filling, and Connectors Mounting                                     | 139    |

|     |      | 6.3.1    | Assembling with Screws and Silver Conductive Paste                                        | 140    |

|     |      | 6.3.2    | One-Drop LC Filling based on Capillary Action                                             | 141    |

|     |      | 6.3.3    | Samples Sealing and Connectors Installing                                                 | 143    |

|     | 6.4  | Devic    | ee Measurement Setup                                                                      | 145    |

|     |      | 6.4.1    | Instruments and Calibration                                                               | 145    |

|     |      | 6.4.2    | Data Collection and Processing                                                            | 146    |

|     | 1    |          | Measured Device Performance, Optimisation, and Future Research                            | 147    |

|     | 7.1  | S-para   | ameters-based Measurement and Validation                                                  | 147    |

|     |      | 7.1.1    | Measured Performance of Devices with Interface Matched by TDR vs. Infin                   | itely- |

|     |      | long T   | ransmission Line Model (TLM)                                                              | 148    |

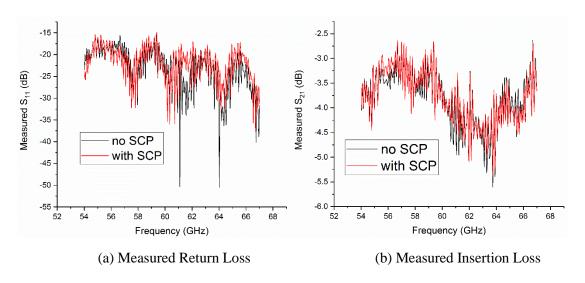

|     |      | 7.1.2    | Measured Performance of Devices with SCP vs. no SCP                                       | 151    |

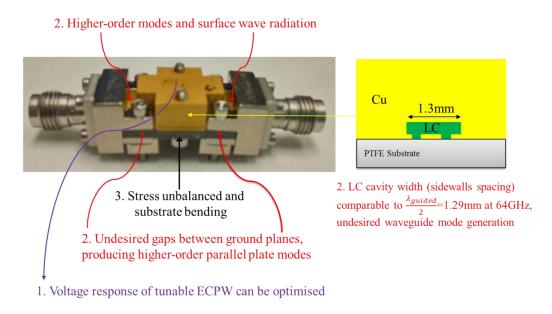

|     |      | 7.1.3    | In-depth Analysis and Limitations of the 1st Round Fabricated Devices                     | 152    |

|     | 7.2  | Devic    | ee Optimisation                                                                           | 155    |

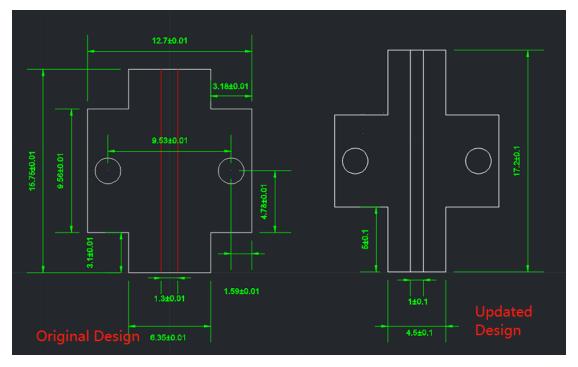

|     |      | 7.2.1    | Components Miniaturisation and Return Loss Reduction                                      | 155    |

|     |      | 7.2.2    | Measured Performance of 2 <sup>nd</sup> Round Optimised Devices vs. 1 <sup>st</sup> Round | 157    |

|     |      | 7.2.3    | Optimisation of Conductor Surface Treatments                                              | 161    |

|     | 7.3  | Meas     | ured Performance Compared with State-of-the-arts                                          | 164    |

|      |                                                            | 7.3.1                                                                 | Summary of Performance Comparison with Different Technologies       | 164 |

|------|------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|-----|

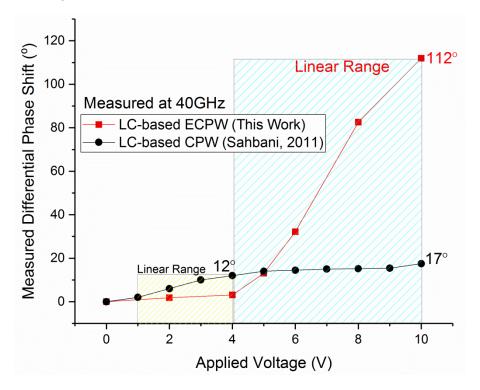

|      |                                                            | 7.3.2                                                                 | Discussion on Phase Tuning Range and Linearity: ECPW vs. CPW        | 167 |

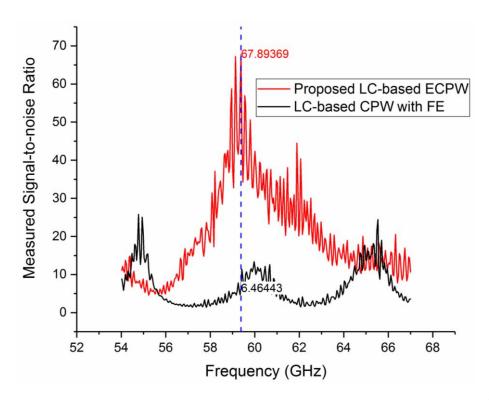

|      |                                                            | 7.3.3                                                                 | Comparison on Signal-to-noise Ratio: ECPW vs. CPW with FE           | 169 |

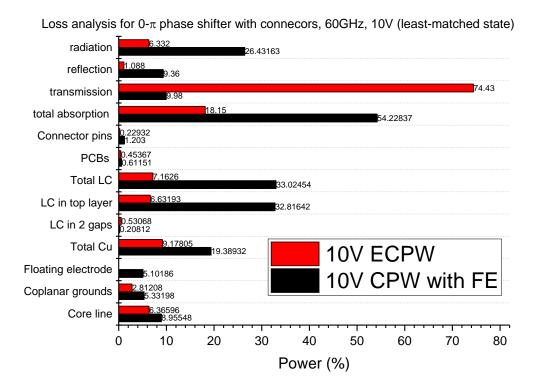

|      |                                                            | 7.3.4                                                                 | Material Absorption Loss Analysis                                   | 170 |

| 7.4  | Discu                                                      | ssion on Device Scalability                                           | 171                                                                 |     |

|      |                                                            | 7.4.1                                                                 | Scalability for 70GHz-90GHz                                         | 171 |

|      |                                                            | 7.4.2                                                                 | Scalability for 2π Phase Shifting                                   | 172 |

| 7.5  | Contr                                                      | rolling 60GHz Field Distribution by Tailoring the Electrodes' Profile | 174                                                                 |     |

|      |                                                            | 7.5.1                                                                 | 60GHz Field Homogenisation                                          | 174 |

|      |                                                            | 7.5.2                                                                 | Hexagonal Core, Right-Angled Ground                                 | 175 |

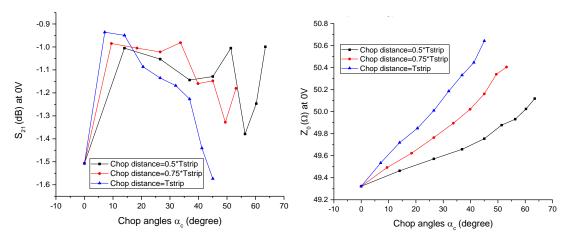

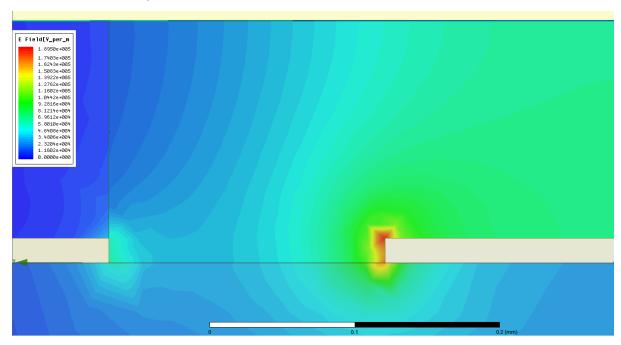

|      |                                                            | 7.5.3                                                                 | Impact of Trapezoidal Effect on the Increase of Insertion Loss      | 178 |

|      |                                                            | 7.5.4                                                                 | Round Conductor(s)                                                  | 181 |

|      |                                                            | 7.5.5                                                                 | Full Conductor-backing Enclosed CPW (CB-ECPW)                       | 182 |

| 7.6  | Other                                                      | Research Possibilities for Optimisation                               | 184                                                                 |     |

|      |                                                            | 7.6.1                                                                 | LC with Lower Product of Dielectric Constant and Dissipation Factor | 184 |

|      |                                                            | 7.6.2                                                                 | Enclosed CPW (ECPW) with Artificial Magnetic Conductor (AMC)        | 185 |

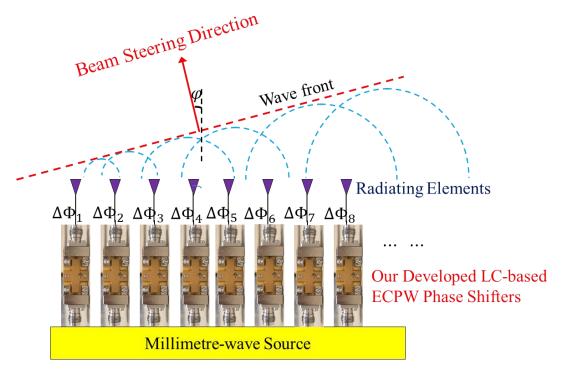

|      |                                                            | 7.6.3                                                                 | LC-based ECPW Phased Shifters Integration for 60GHz Beam Steering   | 185 |

| Cha  | pter                                                       | · 8. C                                                                | Conclusion and Outlook                                              | 188 |

|      | 8.1                                                        | Conc                                                                  | luding Remarks of the Device                                        | 188 |

|      |                                                            | 8.1.1                                                                 | Performance Advantages                                              | 188 |

|      |                                                            | 8.1.2                                                                 | Limitations of the Device Research                                  | 189 |

|      | 8.2                                                        | Know                                                                  | ledge Contributions                                                 | 191 |

|      | 8.3                                                        | Poten                                                                 | tial Applications and Social Impacts                                | 193 |

| Sele | ecte                                                       | l Publi                                                               | cations during PhD                                                  | 194 |

| Ref  | References                                                 |                                                                       |                                                                     | 196 |

| App  | Appendices                                                 |                                                                       |                                                                     | 205 |

|      | Appendix A: Measured Material Properties and Loss Analysis |                                                                       |                                                                     | 205 |

|      | App                                                        | endix I                                                               | 3: CAD for PCB Fabrication                                          | 206 |

|      | App                                                        | endix (                                                               | C: Theoretical Modelling                                            | 208 |

## Chapter 1. Millimetre-wave Beam Steering Applications and Technologies

The availability of 60GHz-90GHz spectrum space is promising in response to a rising demand for bandwidth in the context of the congested spectrum below 30GHz.

### 1.1 60 GHz – 90 GHz Opportunities

Historically, large electrically steered radars were deployed for military applications, such as missile detection/tracking/guidance and fire control, navigation, aircraft surveillance and homeland defence. In addition to the military sector and radio astronomy research (e.g. the Square Kilometer Array (SKA) radio telescope project), phased array antennas also exhibit immerse commercial potential in the Extremely High Frequency band (30GHz-300GHz) for civilian applications, notably the next generation of wireless communications (57GHz-66GHz), satellites communications and navigation systems (60GHz), Intelligent Transport Systems (63GHz-64GHz), as well as the 77GHz automotive multi-beam long-range radars for Adaptive (Autonomous) Cruise Control (ACC), and 79GHz mono-pulse short range radars for vehicle collision avoidance alarm and traffic monitoring functionalities.

### 1.1.1 Fifth Generation (5G) Mobile Communications (57GHz-66GHz)

The ratification of the IEEE 802.11ad amendment has scoped the 60GHz ISM waveband for consumer wireless communication [74]. In Europe, the frequency range from 57GHz to 66GHz provides a license-free 9GHz bandwidth that allows the possibility of high data-rate (multigigabit per second) Wireless Personal Area Network (WPAN) for indoor short-range communications (e.g. supplying wireless multimedia in airplane or car cabins), and other broadband last-mile applications.

In contrast to public bands (2.5GHz and 5GHz) currently deployed for WiFi, 60GHz is susceptible to the following issues that limit its usage in wireless communications.

- [1] Elevated free-space path loss (increases with frequency) according to the Friis transmission formula. As compared with 5GHz, there can be an additional -22dB of signal attenuation for 60GHz at a propagation distance of 10m (a typical range suggested by the IEEE 802.11ad).

- [2] Substantial atmospheric absorptions (98% of 60GHz energy is absorbed by oxygen) and severe rain attenuations in the 60GHz band, which gets more pronounced at ranges beyond 100 meters. From the isolation point of view, however, the oxygen absorption that peaks at 60GHz allows interference-free deployment of closely-spaced systems co-operating at the same frequency, and hence is beneficial for efficient frequency spectrum reuse.

- [3] Struggles to penetrate walls (obstacles in line-of-sight) especially for concrete materials owing to the quasi-optical propagation characteristics and blockage effects followed by 60GHz.

- [4] There are not as many mobile and static devices requiring bandwidth at present. Furthermore, devices based on classical semiconductor integrated circuits and waveguide structures struggle to scale down in size, cost, and insertion loss as required by 60GHz.

Phased array antennas can be used to address these challenges by producing a highly directive beam. Incorporated with beam forming techniques, phased array attracts considerable interests in 60GHz ultra-high-data-rate point-to-point wireless communications by orienting high-gain beams towards distant receivers/transmitters. By producing multiple beams to subdivide the cells, phased array finds its application in base stations with decent improvements without constructing new sites. The far-field radiation pattern is shaped by adjusting the phase/amplitude of the radiators or modifying the aperture distribution. The null difference-pattern offers good beam-pointing accuracy, which improves the spectral efficiency and signal-to-noise ratio. Multi-path fading, bit error rate and co-channel interferences are significantly mitigated, thereby allowing broader band operations and higher data rate delivery for modern communication systems. Undesired interference is insignificant due to the high propagation attenuation at 60GHz. Given these benefits, there is a growing progression of the trend to apply phased array technologies to electrical beam steering at 60GHz in preference to conventional mechanical ways.

### 1.1.2 Inter-satellite Communications (60GHz)

The atmospheric absorption at a geosynchronous altitude of 26000 miles (oxygen-free) is ignorable and hence no longer a concern for 60GHz signal propagation. The last decades have witnessed the development to an increasing extent of terrestrial and satellite services for mobile terminals, airborne and space-based communications. 60GHz inter-satellite communication linking is expected to take advantage of the large bandwidth availability to accommodate the high data-rate capacity required by user satellites (NASA, 1986), and even the emerging multi-spacecraft phase-array communications [8] for deep-space explorations. To track the communication partner between a faster-moving low-earth-orbiting (LEO) satellite and a geostationary orbit (GEO) relay satellite (or between multiple space crafts), electronically steerable phased array antennas play a dominant role in the relay links.

### 1.1.3 Automotive Radar (76GHz-81GHz)

Performing as eyes and ears of a vehicle, radar is arguably a key component of future generation intelligent cars with fully self-driving functions. Superior over light and acoustic sensing technologies, radar offers many advantages, particularly the sustainability in severe weather or lighting conditions. For device size consideration, 60GHz-90GHz is a suitable frequency range to realise a compact car radar system with improved spatial resolution due to the shorter wavelengths. There are increasing incentives towards a worldwide harmonised frequency allocation for car radars in the 76GHz - 81GHz band (3.7mm< $\lambda$ <3.9mm) in place of the current 24GHz one ( $\lambda$ =1.25cm), as higher frequency radars enable antenna array size miniaturisation along with weight reduction. Assuming a 64 by 64 antenna array with a pixel pitch of 2 wavelengths, the dimension of a 24GHz radar will be  $(2 \times 0.0125 \times 64)^2$ =1.6m×1.6m, whereas a 79GHz one by comparison can be scaled to  $(2 \times 0.0038 \times 64)^2$ =48cm×48cm.

Vehicular radar units have already been commercially exploited in modern upper-class models largely for road safety and comfort purposes, such as 24GHz system (resolution in cm level) for pre-crash and lane departure warning, blind spot surveillance and parking assistance, automatic braking and adaptive cruise control (ACC), etc. Radars exhibit several unique

properties when compared with competing/complementing technologies, e.g. ultrasound, video cameras and lidar (Light Detection and Ranging).

Ultrasound sensors (relying on reflected acoustic waves) have limited field of detection and limited resolution by comparison with radar, and hence they are only widely used for parking aid. By contrast with visual observation (optical imaging cameras) and laser-based systems (lidar), radar exhibits robustness to lighting conditions, allowing day and night operations under low visibility and adverse weather conditions (fog, rain, snow, spray). High cost lidar fails to reliably track extremely dirty (non-reflective) vehicles. Furthermore, extreme sunlight and misalignment might cause malfunction. It was reported that Google's latest prototype of a driver-free robotic car (based on lidar and video camera) has yet to be tested in snow or heavy rain out of safety concerns [36]. Another technology reported by [12] is the Night Vision system featuring far-infrared thermal imaging cameras, which rely on temperature differences of objects to function, but the image quality problem is still of customer concern. From the aesthetic point of view, lidar, ultrasound and cameras must be mounted outside (e.g. installed in the bumper), whereas radar can conform into the rooftop or body/glass of the car without extra maintenance.

There has recently been a growing interest in fully self-driving cars, i.e. the vehicle performs all safety-critical functions for the entire trip, with the driver anticipated not to get involved in any control [53]. Intelligent combination of smart radars with camera technology would reliably approach tomorrow's driverless challenge [82]. There is enormous opportunity towards a growth in the automation level, i.e. a leap for semi-automated to truly autonomous, as evidenced by the emerging innovation by sensor fusion (i.e. stereo camera, thermal imaging camera and multi-stage radar sensors) in Mercedes-Benz's Intelligent Drive [51].

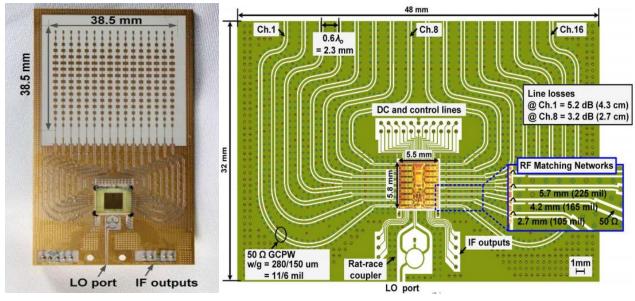

Current commercially available electronically-scanned multi-ranging car radars (e.g. DENSO 77GHz and Delphi ESR 2.5 SAR) are mostly based on Monolithic GaAs p-i-n diodes or Field Effect Transistors (FET) switches. The state-of-the-art includes a 77GHz-81GHz  $16 \times 16$  phased array receiver chip with  $\pm 50^{\circ}$  horizontal field of view for car radar, as demonstrated by the UC San Diego research team [27]. Fig.1 below shows the standard microstrip antenna array and the controller (i.e. their proposed SiGe BiCMOS phased array chip). The overall

dimension of the radar sensor is only 9.2×4.8cm<sup>2</sup>. The phase modulation is still achieved by active switches-based digital phase shifters (5-bit).

(a) Fully Assembled Antenna Array

(b) Control Network

Fig.1 A 77GHz-81GHz Microstrip Antenna Array and Control Network [27]

Note that multiple grounded coplanar waveguides (GCPW with vias) in bended configuration were used for the connection between the SiGe chip and the series-fed microstrip antenna array. The GCPW distributed network causes an average line loss of -3.2dB at the interior and -5.2dB at the periphery of the board due to different line lengths (mostly>3cm).

### 1.1.4 Gesture Sensing (60GHz)

Besides being compact, millimetre-wave radars also significantly improve the spatial resolution, allowing more accurate object distinction. For instance, a 60GHz-90GHz (3mm $<\lambda<5$ mm) radar exhibits a very high positional accuracy inherently suitable for capturing tiny motions of human hands. Based on physical principles of 60GHz radiation that were unexplored in interactive applications, [49] presents a millimetre-wave radar prototype built for driver's hand-gesture sensing, which not only enhances convenience, but also the driving safety.

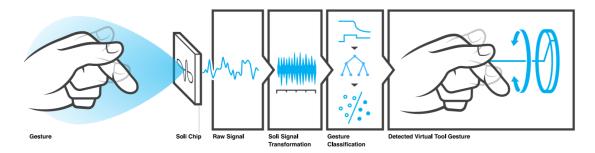

Furthermore, Google's Advanced Technology and Projects group (ATAP) recently launched *Soli* (Fig.2), an interactive computer graphics technology bringing touchless gesture sensing to wearables like a smartwatch and other consumer mobile devices. The demo is essentially a 60GHz radar-on-chip (10mm²), allowing users to intuitively interact with their small-screened

devices by a range of gestures or finger motions, by contrast with traditionally touch-based interface or voice recognition.

Fig.2 An End-to-end 60GHz Phased Array Radar for Fine Gesture Sensing [33]

This is the first time that ubiquitous gesture interaction is realised by an end-to-end millimetrewave radar sensing system that incorporates electrically steered antenna arrays with advanced signal processing and machine learning. Such innovation could help to significantly improve user engagement, and presumably revolutionise the smartphone industry.

### 1.2 Millimetre-wave Beaming Steering Technologies

### 1.2.1 Conventional Beam Scanning by Mechanically Rotating

Conventional beam scanning technology (by parabolic reflector antennas, satellite dishes and previous automotive radars) has long relied on mechanically rotating (motor-driven) antennas to achieve beam redirecting. Fig.3 shows a parabolic antenna for satellite communications, and a radar dish already decommissioned for air traffic control at London Heathrow Airport.

- (a) Satellite Dish in Germany

- (b) Surveillance Radar (London Heathrow Airport)

Fig.3 Traditional Beam Steering by Mechanically Rotating Antenna

This method is inherently slow, clunky, power-consuming, and difficult in responding rapidly enough to track large numbers of fast-maneuvering targets. Moreover, the large and bulky mechanically controlled parts are susceptible to inertia and vibration of mechanical systems, resulting in poor reliability and high maintenance costs. By contrast with a standard single-pixel rotating parabolic dish antenna, there is an increasing demand for electronic beam steering by phased array antennas as discussed below.

### 1.2.2 Electrically Steerable Phased Array Antenna

Adaptive phased antenna array is a key technology for 60GHz wireless communications. The future of beam-steerable systems lies in the implementation of electronically steerable phased array technology, with the advantages and limitations outlined below.

### 1.2.2.1 Advantages of Electronic Beam Steering by Phased Array

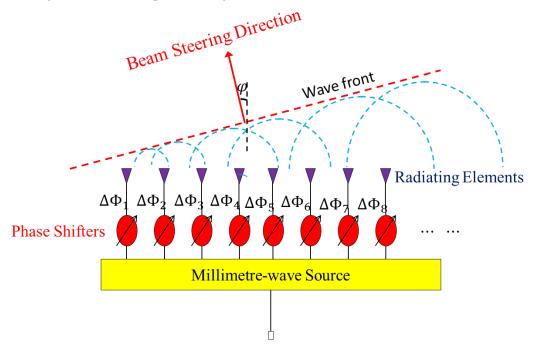

As an evolutionary radar technique, the delivery of a phased array antenna is of research and development interests because of the following features. Firstly, adaptive array smart antennas allow steering the beam to a given direction of focus whilst nulling interfering signals. Without resorting to mechanical rotation, the main beam (maximum energy) of a phased array antenna is electrically steered in one or more dimensions by varying the excitation phases of each radiating element, as interpreted in Fig.4 below.

Fig.4 Electronic Beam Steering by Multiple Phase Shifters-Fed Antenna Array (Static)

The inertia-less beam switching rate falls within the order of  $\sim 1~\mu s$  for certain phased array architectures based on ferroelectrics phase shifters, which outperforms recent advances in mechanical scanning antennas based on RF MEMS. Phased-array based weather-sensing radar would complete a whole-space scanning within 30 seconds, which is far superior to the 4 to 5 minutes required by current mechanical radar systems.

The instantaneous slewing and accurately switching beam-pointing capability allows adaptively programmed multi-mode operations to be performed simultaneously, e.g. multi-target tracking and multi-point communications. Phased arrays also feature far more appreciable reliability and less maintenance costs. Pixel failure with as many as 10% of all the components leads to a loss in gain of only 1 dB, while the system remains operational, and the degradation is graceful. The simultaneous multifunction capability, reconfigurability, and the fault tolerance would contribute to significant cost-effectiveness.

### 1.2.2.2 Challenges in Phased Array based Electronic Beam Steering System

In the domain of radar and communication systems, the behaviour of a phased array is however far more complex than a passive, mechanically positioned antenna. Apart from the benefits as mentioned, current phased-array technique is still subjected to a range of constraints.

First, the performance characteristics of a phased array antenna are scanning angle dependent. Sensitivity is also a function of beam steering direction and fluctuates across the array field of view. For planar arrays, the maximum useful scanning angle is limited to 60° from broadside. When the beam direction moves away from the broadside, there is a slump in the gain of the array. On the contrary, a mechanical driven antenna can steer a beam with a constant gain at any scanning angle.

Second, radiation pattern is strongly affected by mutual coupling effect, causing significant impedance variations with the scanning angle. Taking phased array vehicular radar for an example, the RF interference (RFI) from on-coming vehicles warrants careful consideration.

The third limitation concerns packaging. For aesthetic reasons in the automotive industry, a phased antennas array to be mounted on a car should be light-weight and low-profile. However, reducing the antenna size would increase the beam width and reduce the angular resolution. Solutions of angular resolution improvement can rely on special signal processing techniques, such as Multiple Signal Classification (MUSIC).

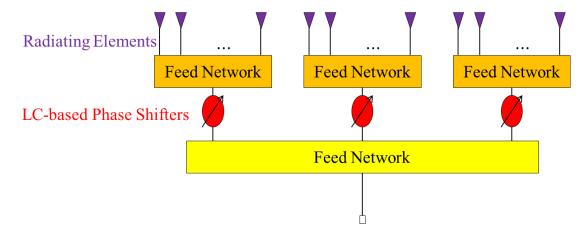

Finally, the quest for decent performance with lower side lobes and wider bandwidth keeps the array costs high. If radiating elements are grouped into several sub-arrays (each equipped with a single delay line as depicted in Fig. 5 below), the required number of phase shifters can be reduced for lower costs, however, the beam scanning range degrades due to the increased side lobes and grating lobes [16].

Fig.5 Primary and Secondary Feeding Networks with the Sub-array Concept

For these reasons, commercialised phased arrays have not yet been in widespread use. Automotive radars based on phased array systems are still limited to being equipped in highend luxury cars such as Mercedes-Benz S-Class [44]. The TracVision A7 antenna system available in the market could provide live satellite television for moving vehicles, but the scanning still partially requires mechanical parts, and the entire hybrid phased array system is still costly, with the retail price reaching \$3995. Whereas for mechanically rotating antennas, the absence of multiple phase shifters and amplifiers (even at large scan angles) drives the cost down. In summary, to commercialise the phased array technology, seeking for millimetre-wave phased shifters with improved performance and lower cost is of paramount importance.

### 1.2.3 Phase Shifting Devices as Key Components in a Phased Array System

As a key component of the phased array antenna system, the phase shifter is of research importance for low-loss beam steering or scanning. In particular, phase shift and insertion loss require a balance of the following performance specifications.

- (1) Millimetre-wave 0-360° or 0-180° phase shift, without breaching the constraint placed on insertion loss (e.g. -4dB).

- (2) Low variation in insertion loss for the full range of phase shift over the required frequency band, i.e. low insertion loss variation with the biasing control. This is aimed at minimising the beam distortion while steering. As the signal combining and null forming at undesired directions is significantly affected by the amplitude of the signal at each channel, the phase shifters are required to not just exhibit a low insertion loss but also maintain a constant loss within their phase tuning range.

- (3) High phase shifting resolution (analogue functionality).

- (4) Ease of control (e.g. low frequency bias), linear phase shift-voltage response, low power consumptions (e.g. bias voltage <10V).

- (5) Fast response (e.g. ferroelectrics can achieve μs switching).

- (6) Robust, reliable (e.g. can work at humid environments and temperature variations).

- (7) High power handling capability (required by low-loss high-power transmitter).

- (8) Compact for integration.

We can envision the use of this low-loss high-tuning-range phase shifter technology in a phased array transceiver to realise certain function as mentioned above, e.g. 5G mobile communications (57GHz-66GHz in Europe), satellite communications (60GHz), gesture sensing (60GHz), and car radar (76GHz-81GHz), etc. Among all these possibilities, we centre attention around the 5G mobile and satellite communications (57GHz-66GHz).

## 1.3 Survey of Current Millimetre-wave Phase Shifters and Their Limitations

Electronically beam-steerable phased array antennas rely on efficient wavefront phase control to produce a desirable rapid-moving radiation pattern with single-radar-based high angular resolution without mechanically sweeping the direction of the antenna in space. There have been various attempts to realise phase modulation in the microwave regime, either by using functional materials (e.g. magnetically or electronically tunable materials), or by switching the antenna elements/transmission lines of different lengths.

#### 1.3.1 Ferrites

Conventional delay lines feeding phased-array antenna systems were implemented with ferrite materials by altering the magnetic bias field. These phase shifters have advantages in terms of high power-handling capacity, decent reliability, radiation tolerance, and thus suitability for high-power applications. However, the tuning is based on the generation of strong magnetic fields, requiring coils biased with hundreds or even thousands of volts. For these reasons, they are bulky, less integratable, slow in response (requiring long tuning times), expensive (not amenable to mass production methods), and have significant power consumptions [38]. Ferrite-based phased array is by no means cost-effective for modern terrestrial applications.

### 1.3.2 p-i-n diodes, Varactors

Current phased array antennas are mostly based on phase shifters implemented in multiple switches, routing the microwave signal through various physical delay lengths to achieve different phase delay for different radiating elements as presented in Fig.6 below.

Fig.6 Principle of Multiple Switchable Delay Lines with Phase Shifts of 45°, 90°, 180°

Such switch-based philosophy has been implemented in different ways, such as GaAs or GaN based p-i-n diodes/Schottky diodes/FETs. The major drawback of these methods is the severely limited phase-shift resolution, predominately limited by control bits, i.e. the number of transmission lines to be switched. According to the nature of discrete tuning in n-bit operation, the phase shift resolution of a 4-bit digital delay line is limited to only  $\frac{360^{\circ}}{2^4}$  =22.5°. Furthermore, solid-state phased arrays based on GaAs monolithic microwave integrated circuit (MMIC) exhibit unacceptably high losses in the millimetre-wave band due to high dissipation factors of the materials.

### **1.3.3 MEMS**

State-of-the-art MEMS technology with microsecond switching speeds seems best suited to a switching function, as it offers a much lower insertion loss, higher linearity over a large bandwidth, and lower power consumptions than the solid-state technology.

However, commercially available MEMS switches are still limited by the maximum operational frequency of up to 40GHz. They are challenged by reliability issues and the drastically rising insertion loss in the millimetre-wave bands when integrating MEMS switches and transmission lines on a substrate. A MEMS-based digital phase shifter (3 bit, 15µs

switching time) was reported to exhibit an insertion loss of -5.7 dB for achieving a 180° phase shift at 76.5GHz [9]. The inherent digital resolution problem as mentioned above finally limits their applicability for the future high-performance phased antenna array beam steering applications.

### 1.3.4 Tunable Dielectrics Methods

Passively controllable microwave components based on continuously tunable dielectrics offer promising alternatives to switch-based topologies (i.e. active semiconductor devices and MEMS as mentioned above).

The permittivity of microwave dielectric materials is a complex value, i.e.

$$\varepsilon = \varepsilon' - j\varepsilon'' = \varepsilon'(1 - j\frac{\varepsilon''}{\varepsilon'})$$

.....(1)

where  $\varepsilon' = \varepsilon_r \varepsilon_0$  is the real relative permittivity (dielectric constant), and  $\frac{\varepsilon''}{\varepsilon'}$  is the loss tangent. The imaginary part  $\varepsilon''$  accounts for power dissipation in the medium (heat) due to damping of the vibrating dipole moments (polarisation induced by an external AC field cannot follow the field anymore). Electrical tunability implies that the permittivity of the interlayer substrate of a device can be modified by an external applied voltage, i.e.

Tunability (E) =

$$\frac{\varepsilon_r(E) - \varepsilon_r(0)}{\varepsilon_r(0)} \times 100\%$$

.....(2)

where  $\varepsilon_r(0)$  and  $\varepsilon_r(E)$  denote the un-tuned and tuned dielectric constants, respectively. Modulation of the real/imaginary part of the relative permittivity of tunable materials could achieve phase modulation of an input signal and hence the control of millimetre-wave transmission properties.

Note that for anisotropic materials, their characteristics variance with directions can be described by anisotropy tensors, i.e. 3 diagonals each for anisotropic permittivity, electric loss tangent, conductivity, permeability, and magnetic loss tangent. Each diagonal represents a tensor of the model along an axis. The permittivity tensor for an anisotropic material is described by

$$\varepsilon = \begin{pmatrix} \varepsilon_1 \varepsilon_0 & 0 & 0 \\ 0 & \varepsilon_2 \varepsilon_0 & 0 \\ 0 & 0 & \varepsilon_3 \varepsilon_0 \end{pmatrix} \dots \dots (3)$$

where  $\varepsilon_1$  is the relative permittivity of the material along one tensor axis,  $\varepsilon_2$  is the relative permittivity along the second axis, and  $\varepsilon_3$  is the relative permittivity along the third axis,  $\varepsilon_0$  is the permittivity of the free space.

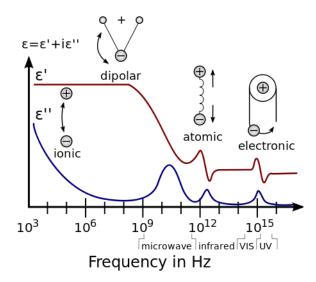

Fig.7 below shows the different polarisation mechanisms occurring in the frequency domain. Up to the microwave region, ion and dipole polarisations dominate. These polarisation types can be described by the Debye's relaxation polarisation model:

$$\varepsilon_{r, complex} = \varepsilon_{r, optical} + \frac{\varepsilon_{r, static} - \varepsilon_{r, optical}}{1 + j\omega\tau}$$

.....(4)

where  $\omega$  is the angular frequency,  $\tau$  is the relaxation time (i.e. the characteristic time that the orientational polarisation or average dipole orientation takes to adjust in a switching field),  $\varepsilon_{r, \ static}$  and  $\varepsilon_{r, \ optical}$  are the static and high frequency permittivity, respectively.

Fig.7 Dielectric Responses in the Electromagnetic Spectrum [50]

As frequency increases, the material's net polarisation drops as each polarisation mechanism ceases to contribute, and hence its dielectric constant. From a certain frequency onwards (>10<sup>15</sup>Hz), the movement of charge cannot remain in step with the alternating field, and all the polarisation mechanisms cease to contribute to the polarisation of the dielectric. The dielectric constant drops to 1, the same as that of a vacuum. Relaxations and resonance processes determine the characteristic of the dielectric constant. Governed by a linear second order ordinary differential equation, the resonance processes are atomic in nature, but out of the scope of this research because they only occur at 10THz onwards. Described by a linear first-order ordinary differential equation, the relaxation processes indicate that the polarisation follows the electric field but is hindered by dissipations [22]. Dielectric loss is especially high around the

relaxation or resonance frequencies of the polarisation mechanisms as the polarisation lags the applied field, causing an interaction between the field and the dielectric's polarisation that results in heating.

However, only a handful of tunable microwave dielectrics have thus far been identified with high tunability and low loss, among them, ferroelectric material barium strontium titanate (BST) and liquid crystal (LC) in nematic phase which are of research and development interests.

## 1.4 Exploring Liquid Crystal based Phase Shifters for 60GHz-90GHz Applications

### 1.4.1 Ferroelectric Barium Strontium Titanate (BST)

As promising candidates for microwave tunable delay lines, BST and LC both exhibit tuning-voltage dependent and temperature dependent electromagnetic properties with different degrees of field-dependent nonlinearity and frequency-dependent dielectric loss. Since tunability and losses of different dielectrics might differ appreciably depending considerably upon the operating frequency, BST and LC operating in different frequency ranges are identified below.

Ferroelectric BST thin films do exhibit decent performance below 10GHz-15GHz (depending on applications), with figure-of-merit in terms of phase shift per loss reaching 50-100°/dB at 1GHz. However, the tunability is counterbalanced by considerably increasing dielectric loss beyond 10GHz. For this reason, there is a slump in the figure-of-merit, dropping down towards only 25°/dB at 10GHz. The high dielectric loss at millimetre-wave bands severely restricts their application potential. The intrinsic loss originates from collisions with thermal phonons, while charged defects, the universal relaxation law, and quasi-Debye contribution account for the extrinsic loss.

Recent efforts in loss reduction rely on doping ferroelectric materials with oxides, e.g. MgO,  $Al_2O_3$ , and  $ZrO_2$ . However, the reduction in loss tangent (as low as 0.004 reported at 10 GHz by adding MgO and Mg<sub>2</sub>TiO<sub>4</sub> to a 50/50 BST) is at the cost of reduced tunability [1], and hence only a minor improvement in figure-of-merit.

### 1.4.2 LC's Advantages over BST for Millimetre-wave Applications

More recently, liquid crystal (LC) in nematic phase has been reported in electrically tuned microwave devices (e.g. resonators, filters, phase shifters, antennas, frequency-selective surfaces) that are essential components of a phased antenna array system. Working as tuning dielectric materials based on molecular shape anisotropy (explained in Chapter 2.1), liquid crystals offer highly attractive properties over competing technologies.

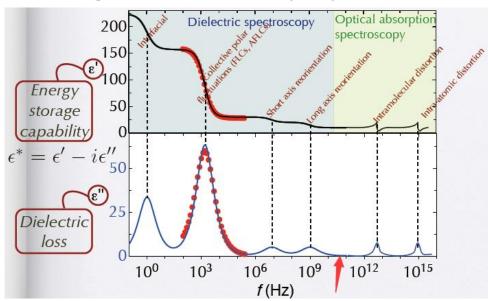

- (1) First and foremost, continuous tunability (0- $2\pi$  analogue phase shifting capability). With LC-based phase shifters, appreciable resolution of beam scanning is achievable to outperform digital resolutions.

- (2) Very low-loss dielectric properties (almost transparent) above 10GHz up to 1THz, as evidenced by the dielectric spectroscopy as shown in Fig.8 below. The dispersion of the permittivity is associated with the dipolar relaxation behavior due to molecular dynamics. For this work, the targeted frequency band is sufficiently higher than the dielectric relaxation absorption bands of liquid crystals, and hence enables low-loss performance. Using a V-band (50GHz 75GHz) rectangular waveguide test cell, it was reported that nematic LC is transparent in the millimetre-wavelength range [76].

Fig.8 Broadband Characterisation of Liquid Crystals [37]

As observed from Fig.8 above, although the tunability of nematic LC between 10GHz and 100GHz is not exceptionally large (almost a constant permittivity as there is no dielectric relaxation in this interval), the low loss tangent (no strong absorption band around this region) tips the balance. The dielectric properties (particularly the low loss tangent) of LC are most favourable at millimetre-wave bands (>30GHz). By contrast with BST thin films, the dielectric loss of LC above 10GHz decreases with frequency. Figure-of-merit (defined as the ratio of phase tunability to insertion loss) of LC rises with millimetre-wave frequency and thus, making it the most competitive low-loss tuning material in the millimetre-wave bands.

- (3) Ease of control. Very low control voltage ( $\sim 10V$ ), low power consumptions (E  $< 0.2V/\mu m$  to drive the LC in comparison with BST ( $30V/\mu m$  to obtain a reasonable tunability, depending on the structure). Under a higher biasing field, ferroelectric devices are more prone to sample aging, polarisation fatigue and hence a degradation of the tunability.

- (4) Good temperature stability. LC-produced phase delay is less sensitive to temperature variation (within  $\pm 20^{\circ}$ C). Measurement conducted by [70] shows a minor temperature dependence of LC in tunability at  $-10^{\circ}$ C,  $24^{\circ}$ C, and  $50^{\circ}$ C.

To recapitulate, the potential of liquid crystals as reconfigurable materials arises from their appreciable tunability, low polarisation loss (especially above 10GHz), ease of control (continuous tuning with low power consumptions), transparency, and possible integration with printed and flexible circuit technologies. The continuous tunability (i.e. analog functionality) is especially useful in beam-scanning applications for improving the beam-pointing accuracy and compensating for temperature or aging drift. In this context, there is a momentum towards the combination of LCs and the phased array antenna technology in preparation for futuristic millimetre-wave applications.

### 1.4.3 Limitations of Nematic Liquid Crystal

However, nematic liquid crystals (NLC) do exhibit three main limitations.

First, the switching speed ranges from  $\sim$ ms to  $\sim$ s (depending on operating wavelength, type of LCs and the layer thickness), which is far slower than that of BST thin films ( $\sim$ µs). Although the increase of applied driving voltage or a decrease of the threshold voltage could effectively reduce the rise time, the tuning speed of a microstrip type NLC cell is predominately limited by the undesirably large decay time (slow reorientations). A diversity of methods has been suggested to alleviate this problem, including a  $\pi$ -cell configuration, membrane impregnated with NLC, dual-frequency switching-mode NLC [6], etc. However, they exhibit different degrees of problems, such as a rise in insertion losses, a decrease in tunability and hence a degradation of the achievable phase shifts.

Second, field-dependent nonlinearity. The effective working range is limited by two threshold voltages, i.e. the Fredericks transition voltage and a saturated voltage. The initial threshold voltage can be lowered by increasing the dielectric anisotropy, reducing the elastic constant, as well as reducing the flow viscosity. However, reducing the elastic constant may weaken the restoring torque, and hence slowing down the response time to post-removal of the bias field.

Third, the fluidic nature limits the device topology. LCs must be enclosed and sealed inside a sandwich structure. Making LCs surrounding a core line in a cylindrical way (coaxial) or strip line presumably achieves a higher tuning range than IMSL and CPW but remains challenging to organise the structural integrity problem. The packaging requirement also increases the device footprint, which limits its integration into chips with close feature registration.

An even bigger challenge is how to best design and fabricate low-loss tunable devices in the millimetre-wave regime to enable innovative phased-array applications and open the door of low-cost manufacturing for commercialisation. While electromagnetic fields interactions with LCs have been well researched for optical and comparatively low-frequency bands, there have been few studies reporting measurements and development for the millimetre-wavelength range. Developing LC-based GHz/THz phased-array antennas remains in an embryonic proof-of-concept stage. Design and optimisation space remain largely unexplored. Challenges in LC at millimetre-wave are studied in Chapter 2.2.

The choice of the LC material type and the structure design of a variable delay line depend on different beam steering applications. For missile-tracking radars, where fast response time is an important consideration, the LC layer must be thinner to enhance the switching speed. Instead, for weather radars, airport surveillance or microwave relay satellite, there is little need for ultrafast response (e.g. for relay links between a faster moving low-earth-orbiting satellite and a geostationary relay satellite, the requirement for angular tracking velocities of low earth orbiting satellites is typically 180° in 45 minutes, i.e. 4°/min), so the LC layer could be made thicker to reduce the insertion loss. To improve phase shift performance without degrading the switching speed significantly, we could replace the current LC materials with higher birefringent ones to reduce the thickness of the LC layer (but insertion loss will be increased), or optimise the device structure as discussed next.

## Chapter 2. Different Approaches of Phase Shifter Configurations with LC above 60GHz

This chapter conducts a critical review of the situation in existing knowledge about LC-based phase-shifting device configurations, which provides motivation and justification for the research question. Based on the working principles and unique structural requirements of LC-based phase components (Chapter 2.1), a variety of challenges are envisioned for the 60GHz phase shifters combining with LC (Chapter 2.2).

### 2.1 Principle of Liquid Crystal based Phase Tuning Components

The potential of liquid crystals (LCs) as reconfigurable materials arises from their appreciable tunability, low polarisation loss (especially above 30GHz), ease of control (continuous tuning with low power consumptions), transparency, and possible integration with printed and flexible circuit technologies. Working as electrically tunable dielectrics based on molecular shape anisotropy (section 2.1.1), nematic LCs have relatively high tunability and low loss to outperform ferroelectric materials (e.g. barium strontium titanate BST thin films) in the millimetre-wavelength range (>30GHz). The underlying physics and chemistry of nematic liquid crystals reviewed in literature [64] and [30] are applied to our research into the LC-based millimetre-wave phase shifter device.

### 2.1.1 LC Dielectric Anisotropy due to Molecular Shape Anisotropy

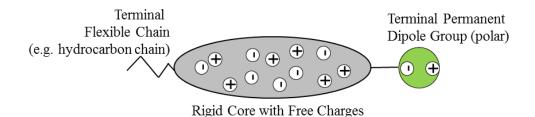

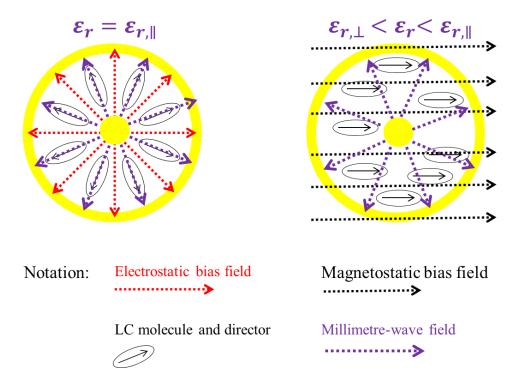

First, we depict a rod-shaped model of the liquid crystal (LC) in nematic phase in Fig.9 (a) below, with mobile charges inside a rigid core polarised by an external low-frequency bias field (5Hz for example) as shown in Fig.9 (b), resulting in reoriented dipole moments.

(a) An Exemplary Molecule Representation of the Nematic Liquid Crystal

Reorientation of LC's dipole moment  $(Q\overrightarrow{d_n})$  by electrostatic field

(b) Bias Field-Induced Reorientation of the Liquid Crystal in Nematic Phase

Fig.9 An Exemplary Nematic LC Molecule Model and the Reorientation Mechanism

The chief effect of a low-frequency field  $\vec{E}_{bias}$  applied to the molecule is producing dipole moments that align themselves in the direction of  $\vec{E}_{bias}$  (a phenomenon called polarised). From the free-energy minimisation point of view, lowest energy of the anisotropic LC occurs when the largest component of the dielectric constant tensor is in line with the applied bias field, hence the induced reorientation as shown above.

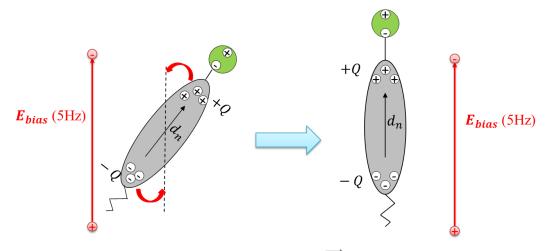

The fundamental of LC's tunability in the dielectric constant is attributed to its molecular shape anisotropy, where the size across two orthogonal molecule axes differs (i.e.  $d_{\perp} \neq d_{\parallel}$ ), resulting in dipole moment difference and hence the difference in polarisation  $\vec{P} = NQ\vec{d}$  ( $C/m^2$ ). We depict this in Fig. 10 below, with a positive dielectric anisotropy assumed (i.e.  $d_{\parallel} > d_{\perp}$  and hence  $\vec{P}_{\parallel} > \vec{P}_{\perp}$ ). The polarisation  $\vec{P}$  characterises the polarisation density (induced dipole moment per unit volume) of the LC dielectric medium under the 60GHz field  $\vec{E}_{60GHz}$  to be transmitted. Here N denotes the number of dipoles per unit volume, and  $Q\vec{d}$  is the dipole moment. Note that the LC reorientation effect is not induced by the 60GHz electric field (as it is oscillating too fast for molecules to follow, and also the field is too weak far below the

transition voltage), but attributed to the low-frequency AC biasing, or mechanical anchoring using a surface alignment layer (section 2.1.3).

Fig.10 LC Molecule Interacting with 60GHz Signal:

Molecular Shape Anisotropy and the Resulted Polarisation Difference

From  $\vec{P} = NQ\vec{d} = (\varepsilon_r - 1)\varepsilon_0\vec{E}$ , and the  $\overrightarrow{P_{\parallel}} > \overrightarrow{P_{\perp}}$  as explained above, we can derive that  $\varepsilon_{r,\parallel} > \varepsilon_{r,\perp}$ . With this dielectric anisotropy  $(\varepsilon_{r,\parallel} > \varepsilon_{r,\perp})$ , the low-frequency bias voltage -dependent molecular director transition from the perpendicular to the parallel state allows a continuous tuning of the dielectric constant and hence a differential phase shift for a phase shifter device, as interpreted in the following section 2.1.2.

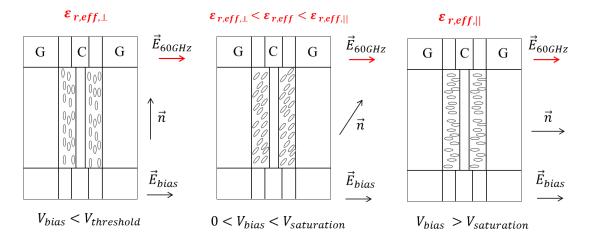

### 2.1.2 Elements of Electrically-Tuned LC Phase-Shifting Architecture

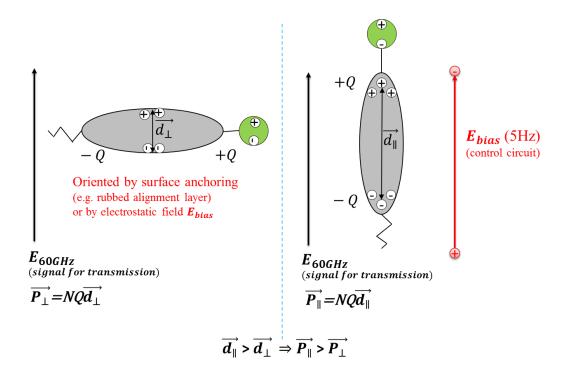

In Fig.11 below, we sketch a classical structure of two-planar-electrodes separated by a distance (cell gap) where LCs and alignment layers are placed. The cell gap is within the range of the anchoring effect enforced by surface treatment (alignment layer). The low-frequency voltage bias ( $V_{bias}$ ) here is a low-frequency AC (e.g. 5Hz sinusoidal or rectangular) instead of a DC for avoiding ions localisation in the LC.

Fig.11 Exemplary Architecture of the LC-based Phase Shifter and the Tuning Mechanism

When the bias voltage is lower than a threshold, i.e. the Fredericks transition voltage [64], molecular switching is not induced, but anchored by the pre-treated surface with a mechanically rubbed polyimide film (called alignment layer). A nearly homogeneous LC dielectric layer with molecular directors orthogonal to the 60GHz electric field can be assumed ( $\varepsilon_{r,LC} = \varepsilon_{r,\perp}$ ). With the applied voltage increasing to the saturation bias, the mechanical anchoring effect by the treated surface is eclipsed by the low-frequency biasing field, resulting in the directors being in parallel with the biasing field. Note that for a standard transmission line structure that supports transverse-electromagnetic (TEM) mode (cutoff frequency is 0Hz, i.e. DC), the 60GHz electric field vectors follow an identical direction of the biasing field at the low frequency. Therefore, the director of the LC layer under the saturation bias is also parallel with the 60GHz signal's polarisation, i.e.  $\varepsilon_{r,LC} = \varepsilon_{r,||}$ . The dielectric anisotropy and hence the dielectric tunability of the material is defined as:

$$Tunability = \frac{\varepsilon_{r,||} - \varepsilon_{r,\perp}}{\varepsilon_{r,\perp}} \times 100\% \dots (5)$$

The dielectric constants ( $\varepsilon_{r,\perp}$  and  $\varepsilon_{r,\parallel}$ ) here are bulk (macroscopic) properties. The macroscopic dielectric anisotropy and hence the material tunability depends on the ordering of the molecules and polarisabilities of the molecules. For an incident millimetre-wave signal, the bias voltage-controlled analogue tuning of the LC's dielectric constant can produce a

continuous differential time delay  $\Delta t$  and hence the differential phase shift  $\Delta \Phi_{21}$  as derived below.

Differential time delay

$$\Delta t = \frac{L}{c_0} \Delta n_{eff} (V_{bias})$$

.....(6)

Differential phase shift

$$\Delta \Phi_{21} = 2\pi f \Delta t = \frac{2\pi f L}{c_0} \Delta n_{eff} (V_{bias})$$

.....(7)

where:

f is the frequency of the millimetre-wave signal.

L is the is the physical length of the phase shifter.

$c_0$  is the light velocity in vacuum.

The effective birefringence  $\Delta n_{eff} = \sqrt{\varepsilon_{r,eff,||}} - \sqrt{\varepsilon_{r,eff,||}}$  here is the maximum effective dielectric anisotropy in the wave-occupied volume (WoV, a concept we propose and is detailed in Chapters 2.6 and 4.2).

Note that both  $\varepsilon_{r,eff,||}$  and  $\varepsilon_{r,eff,\perp}$  are effective dielectric constants based on the wave-occupied volume (WoV) of a specific device structure, instead of purely the permittivity of LC in two extreme states. In this regard, the device tuning range (TR) of a LC-based tunable phase shifter structure is defined as eq.8 below (not to confuse device's tuning range with material's tunability).

$$TR = \frac{\varepsilon_{r,eff,\parallel} - \varepsilon_{r,eff,\perp}}{\varepsilon_{r,eff,\perp}} \times 100\% \quad .....(8)$$

With a fixed type of LC material (i.e. tunability is known and fixed), the device's tuning range (*TR*) is not only a function of the LC material's tunability, but also is affected by the guiding structure's geometry as well as the dielectric properties of other substrates interacting with the millimetre-wave fields. We will cover the investigation into the device's tuning range maximisation and optimisation in Chapters 2.6 and 4.2.

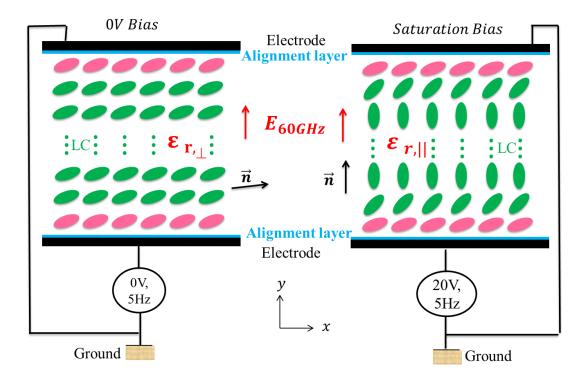

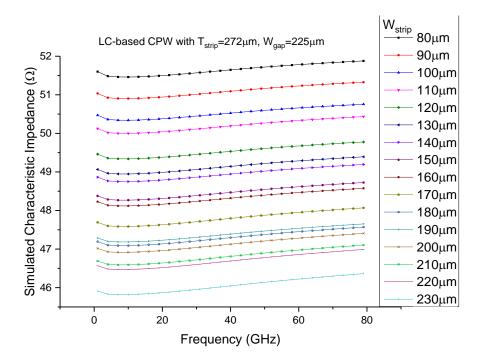

### 2.1.3 Planar Alignment by Surface Anchoring

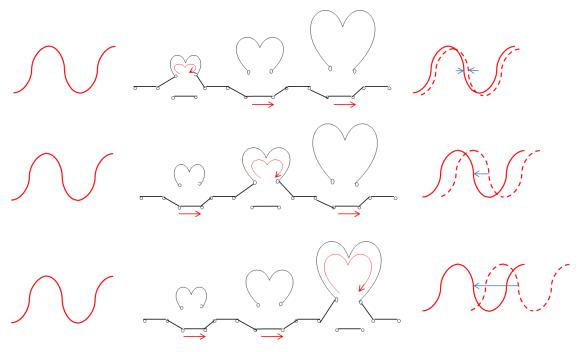

Planar alignment of LC molecules can be achieved by mechanically rubbing micro-grooves on a polyimide film, which helps anchoring the molecules in a desired reference direction ( $\varepsilon_{r,\perp}$ ), for which the maximum tunability can be realised when a saturation bias voltage is applied ( $\varepsilon_{r,\parallel}$ ). Meanwhile, it helps restoring the original planar structure when the bias is removed.

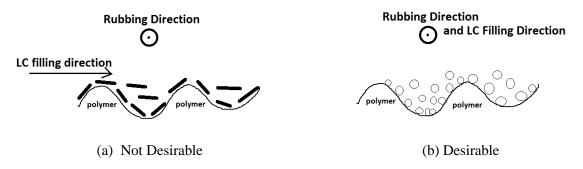

In addition, LC-filling is arguably also an alignment process. As illustrated in Fig.12 below, it is energetically favourable to make the LC filling direction in line with the pre-alignment (rubbing) direction to minimise distortions in the director field.

Fig.12 Implications of the LC-Filling Direction and the Rubbing Direction

# 2.2 Challenges in LC-based Phase Shifters at Millimtre-wave

## 2.2.1 Transmission Line Effects and Characteristics of Various Line Structures

At extremely high frequency (microwave and millimetre-wave) as the circuit length is comparable to the guided wavelength ( $>\lambda/8$ ), transmission line effects become prevalent. The behavior of a transmission line in the millimetre-wavelength range is predominately wave-like, exhibiting a distributed parameter network, where voltages and currents vary appreciably in magnitude and phase over its length, making it insufficient to define voltage, current and impedance by the classical circuit theory (e.g. lumped element model). The propagation effects produce substantial time delays in time domain, or phase shifts in harmonic (phasor) amplitudes. The dynamic behavior is governed by the full set of Maxwell's equations. Electric and magnetic field vectors governed by Maxwell's equations are the primary unknown quantities, whereas voltages and currents (as secondary quantities) are derived by integrations along specific paths upon which they depend [19].

A transmission-type phase shifter (i.e. phase delay produced by transmission of a signal through a device) can be implemented in different transmission-line or waveguide topologies (Table.1), depending critically on the targeted wavelength range.

Table 1. Comparison of Various Types of Transmission Lines [45]

(★★★★★ is very good, ★★★★☆ is good, ★★★☆☆ is neutral, ★★☆☆☆ is poor)

| Topology        | Frequency | Characteristic       | Q-factor | Power    | Physical | Ease of Fabrication |

|-----------------|-----------|----------------------|----------|----------|----------|---------------------|

|                 | (GHz)     | Impedance $(\Omega)$ |          | Handling | Size     |                     |

| Strip Line      | <20       | 10-120               | ***      | ****     | Medium   | * <b>*</b> *        |

| Slot Line       | <40       | 20-150               | ****     | ****     | Medium   | * <b>*</b> *        |

| Coaxial         | <50       | 10-600               | ****     | ****     | Large    | <b>★★</b> ☆☆☆       |

| Suspended Strip | <50       | 30-200               | ****     | ****     | Large    | *** <b></b>         |

| Microstrip      | <50       | 10-120               | ***      | ****     | Small    | ****                |

| Coplanar Line   | <100      | 40-150               | ****     | ****     | Medium   | ****                |

| Waveguide       | 1-300     | 100-500              | ****     | ****     | Large    | ***                 |

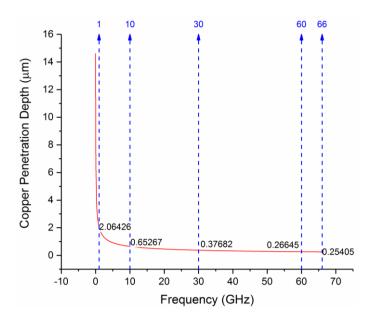

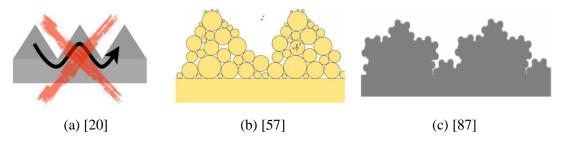

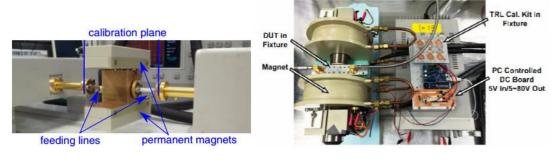

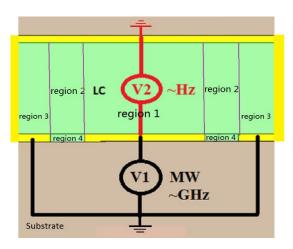

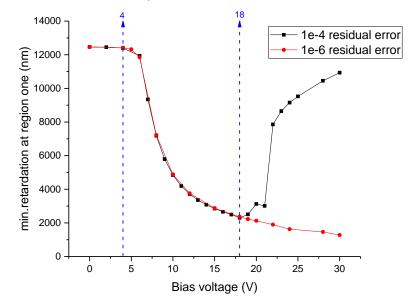

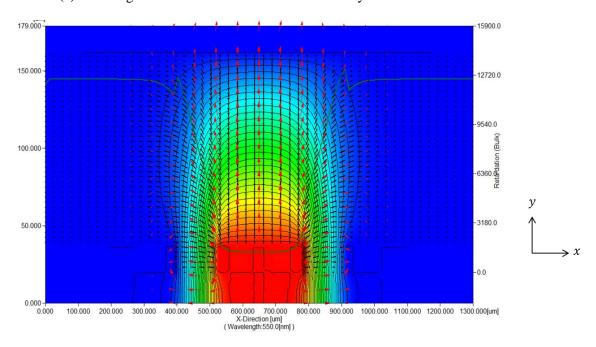

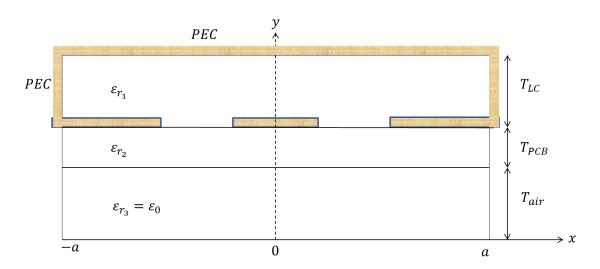

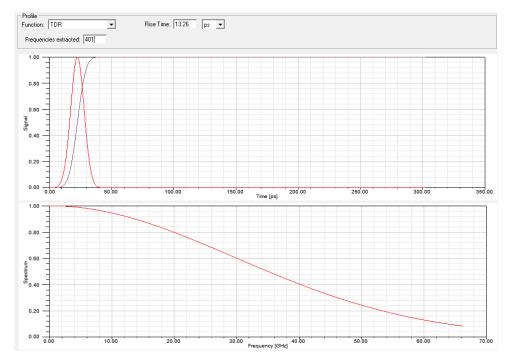

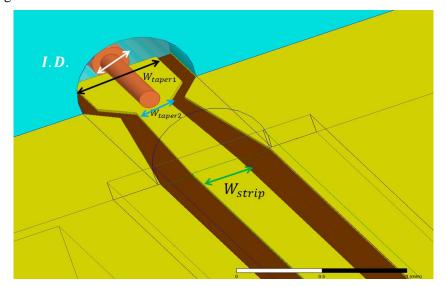

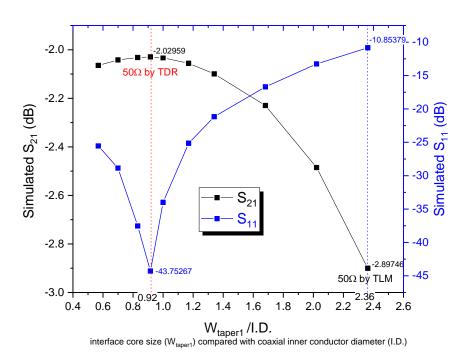

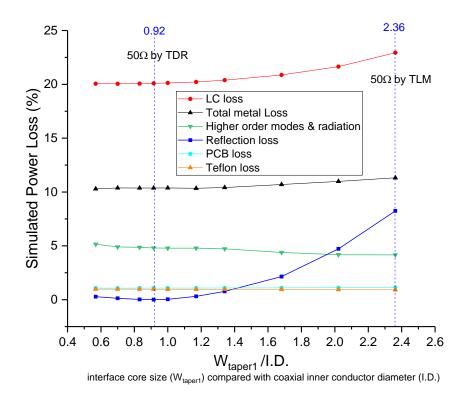

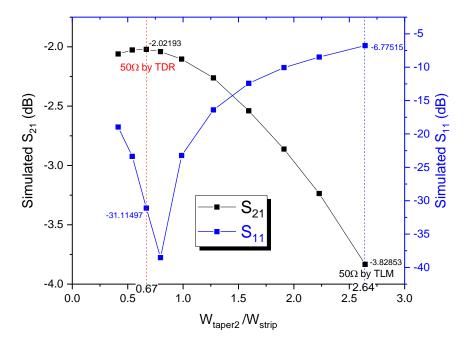

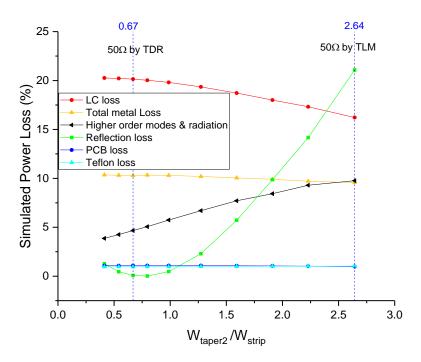

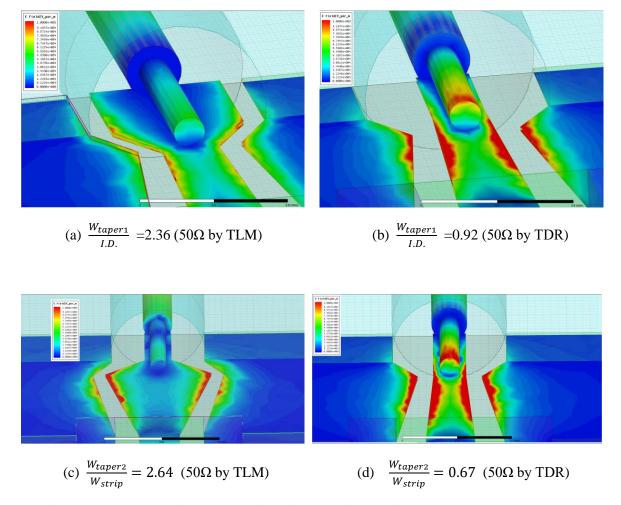

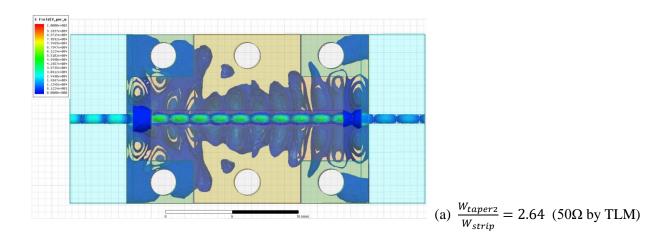

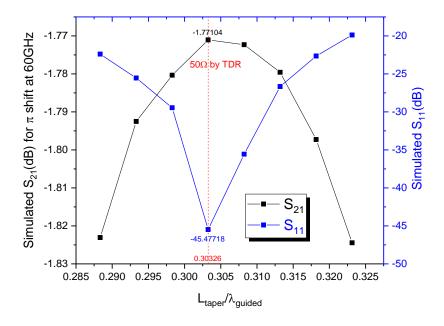

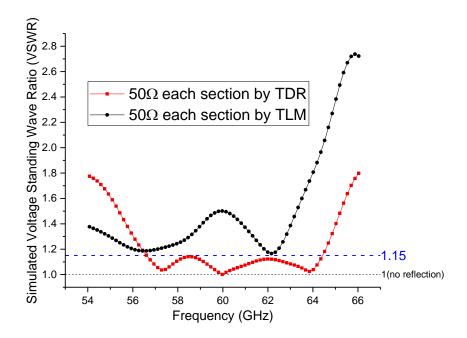

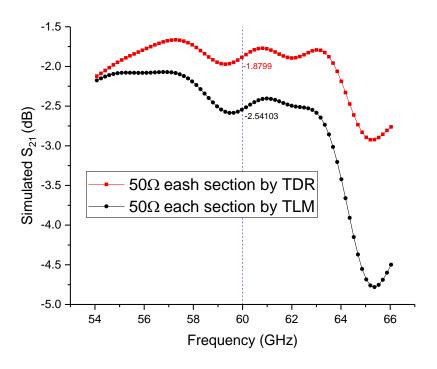

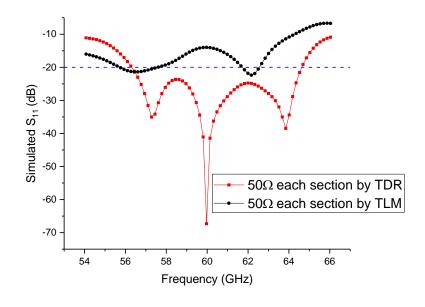

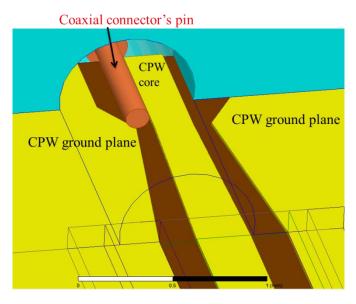

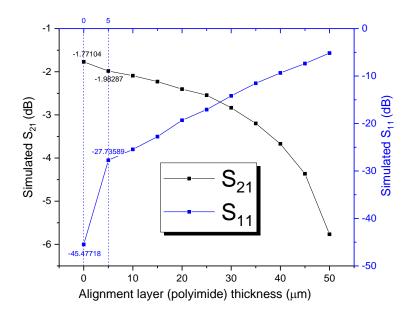

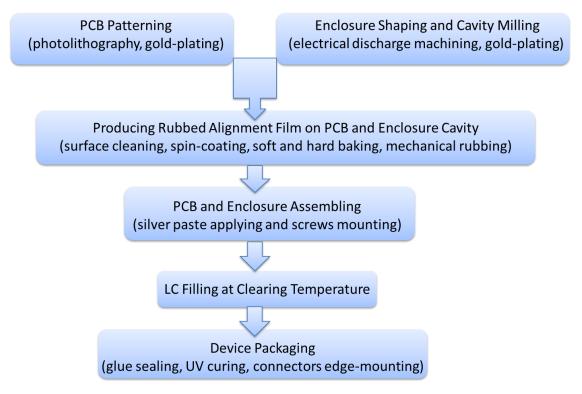

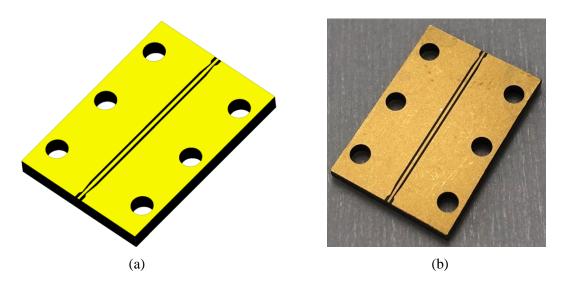

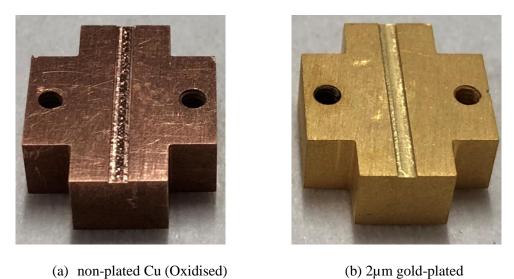

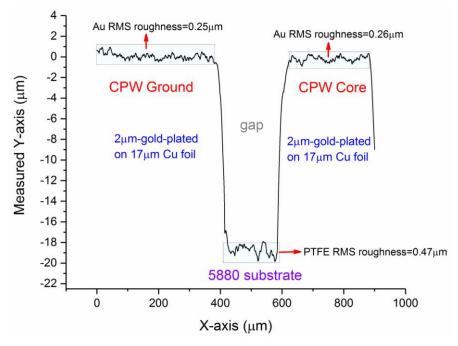

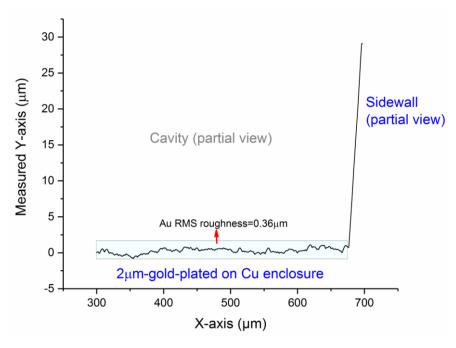

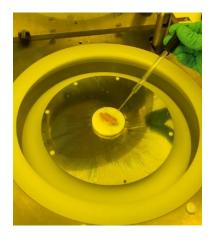

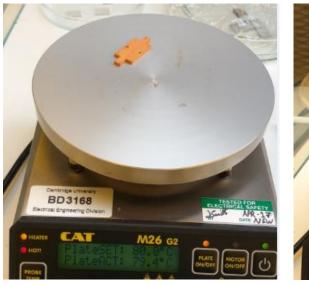

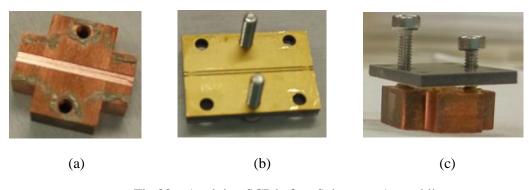

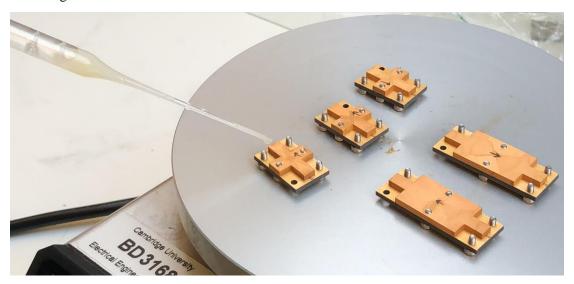

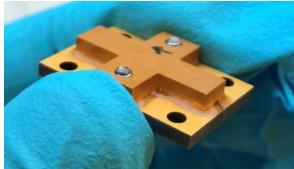

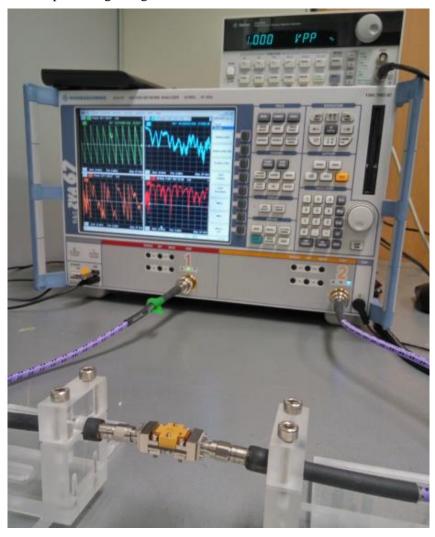

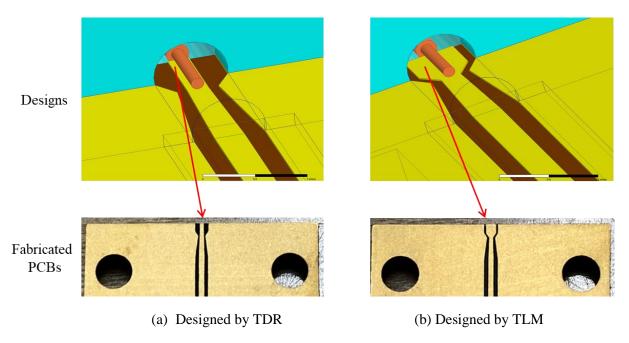

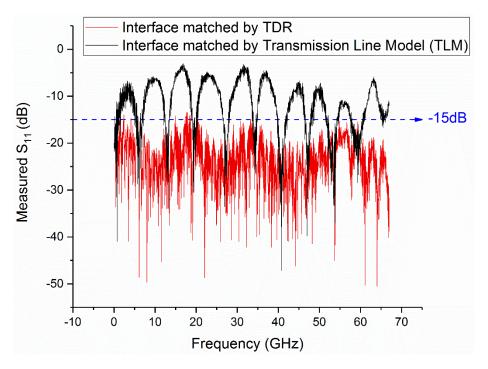

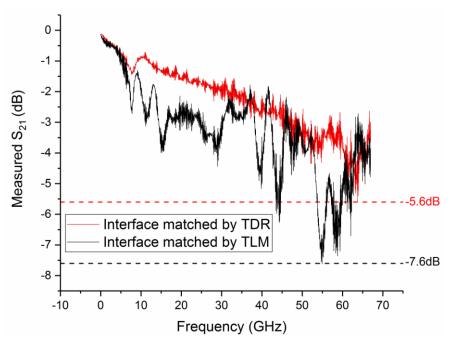

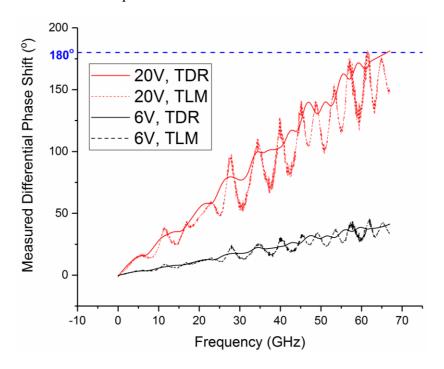

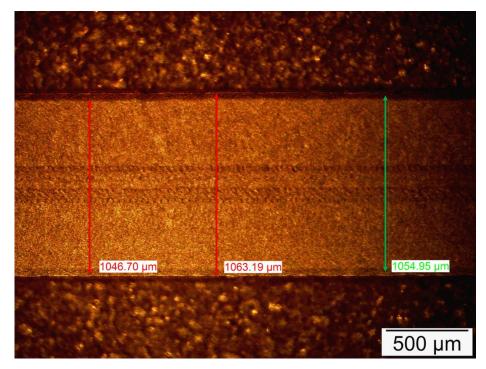

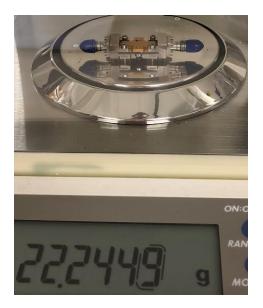

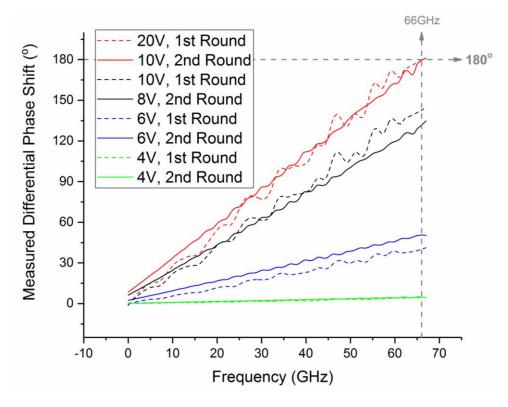

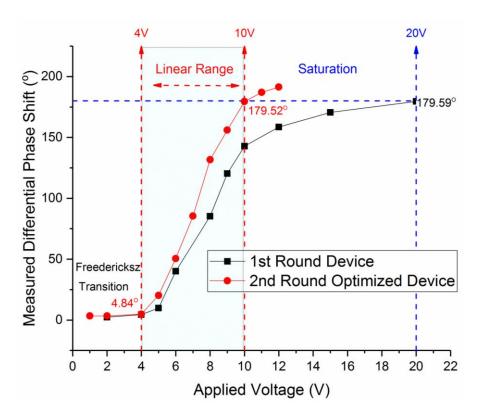

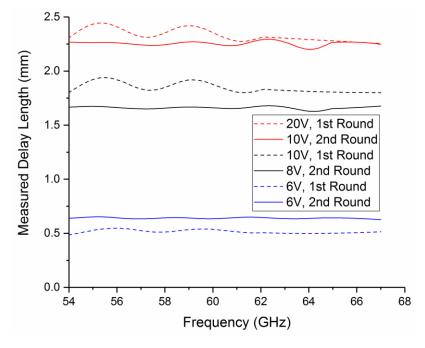

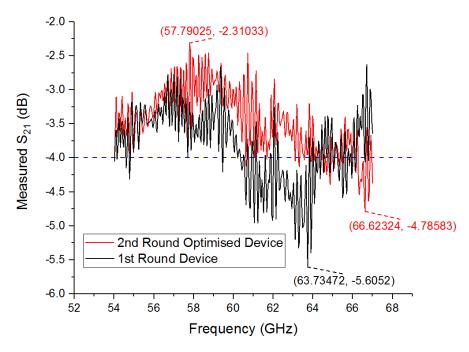

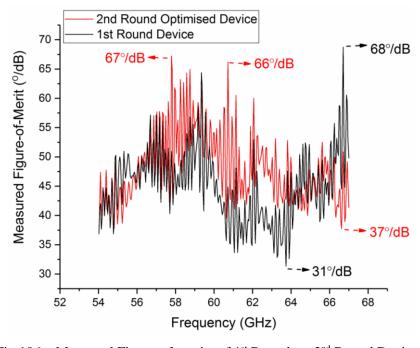

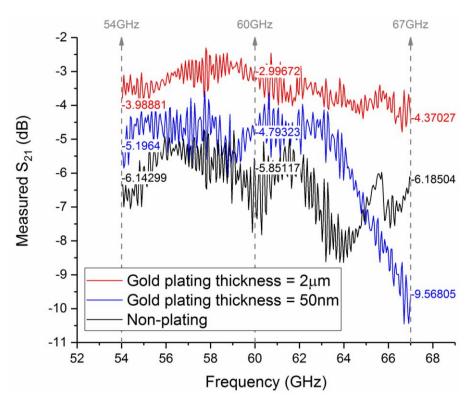

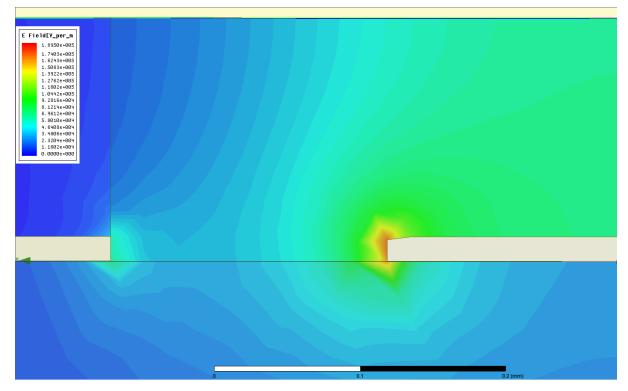

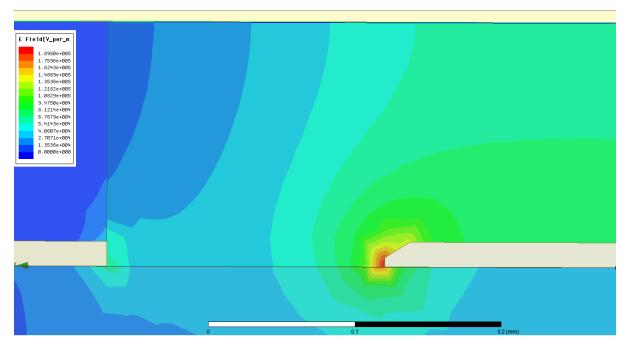

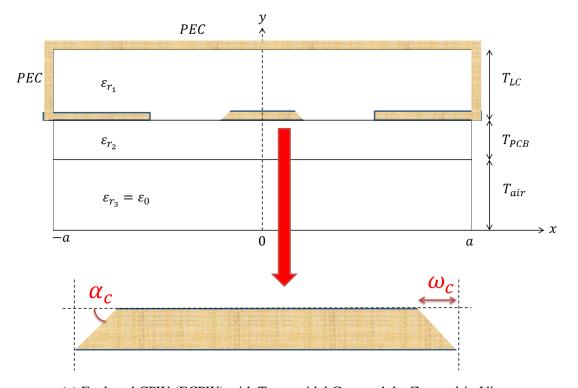

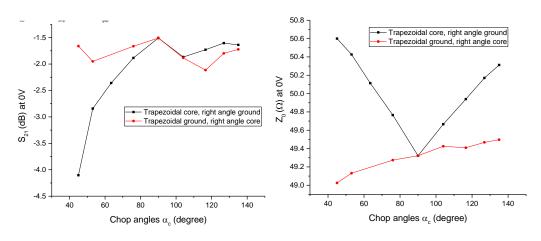

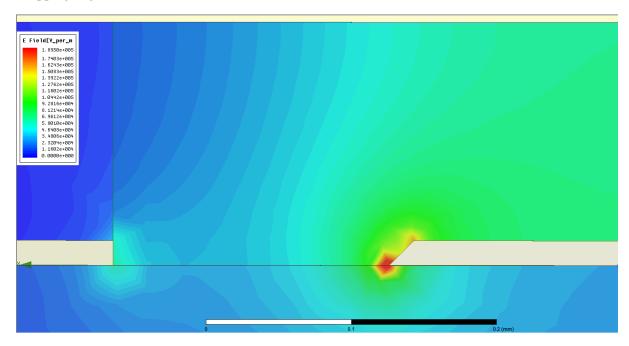

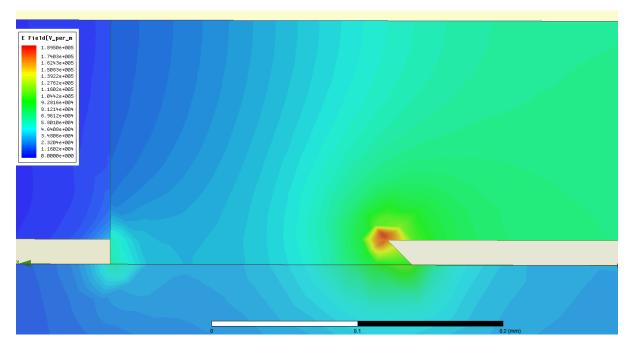

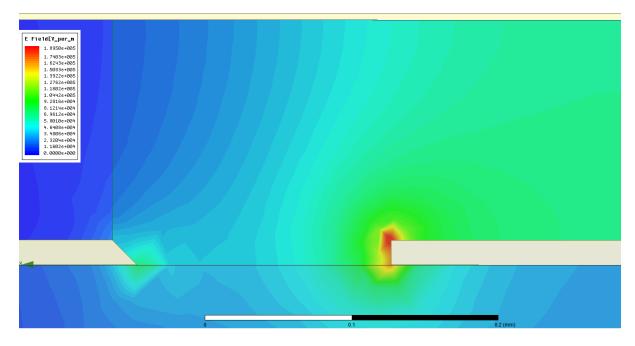

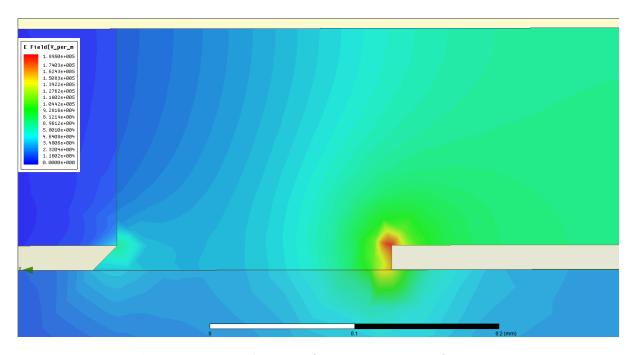

Conductor loss and dielectric loss are of paramount research importance, with the theoretical calculating mechanism of which detailed later in Chapter 3.4, as it is challenging to decompose different losses by experiment. Beyond that, there are a few loss mechanisms that are particularly of research interest for 60GHz-90GHz. With the decrease of wavelength from microwave to millimetre-wave, circuit performance degradation not observable at the microwave bands can, however, be noticeable in the millimetre-wave frequencies. A few millimetre-wave effects that make a difference to the device performance are studied and reported in the following sections.